一种机载相控阵雷达波控系统设计

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

相控阵技术广泛地应用于军事民用的各个领域,其主要特点和优点就是天线系统能够实现快速灵活的波束扫描,为雷达系统更好地完成对目标的搜索与跟踪提供了必要的条件。波控系统不仅要为天线扫描提供正确的相位码,还要满足波束转换的速度要求,做到迅速精确地布相,同时还要具有阵面监视与状态控制能力,因此相控阵雷达波束控制系统设计的好坏,对整个雷达系统能否实现其强大的功能是至关重要的[1]。本文介绍了一种机载相控阵雷达波控系统的设计,具有小型高速、可靠性高与灵活性高等特点,适用于中型及大规模相控阵雷达设计。

1 系统设计实现

1.1 波控系统架构设计

波控设备是安装在载机平台的舱外天线单元内部,根据雷达任务要求,需要完成1 000多个T/R组件的数据和时序控制任务。系统设计时,考虑到波控的计算任务量不是很大,可由雷达综合处理单元中的时序监控模块完成波控码的计算,这样可以省去计算机模块的设备量。另外根据总体要求,对天线阵面上的波控接口、T/R组件及组件调制电源进行一体化设计,形成通用SAM多功能板模块,既减少了单元之间的电缆连接,又有利于信号传输的稳定性,实现了波控及整个天线设备的小型化设计要求。

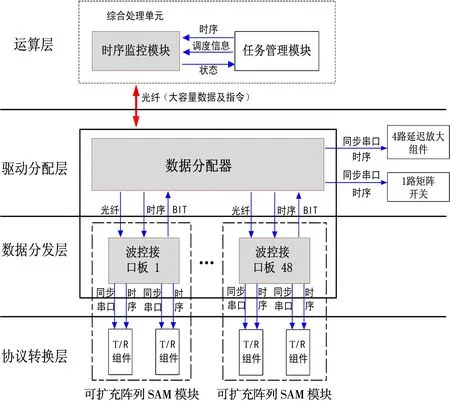

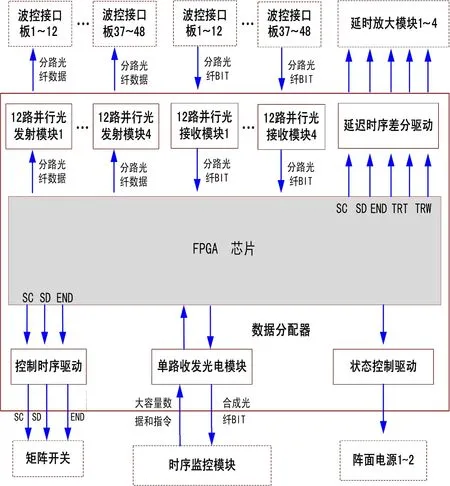

鉴于前述几个方面的考虑,波控设计采用分级架构,从上至下各层级分别为运算层、驱动分配层、数据分发层和协议转换层,具体框图如图1所示。

图1 雷达阵面波控分级架构

运算层设备是指雷达任务电子的综合处理单元,该单元包括时序监控模块和任务管理模块等,波控的移相码运算功能就是嵌入在时序监控模块中。时序监控模块收到任务管理模块的控制指令后,提前一个波位周期计算出所有1 000多个T/R组件的移相码值,然后将这些数据打包,通过光纤高速线送给波控。时序监控模块同时产生整机的时序触发,并转发给波控。

驱动分配层设备是由数据分配器实现,主要完成大容量数据的分发任务。数据分配器位于天线阵面,接收时序监控模块送来的光纤打包数据,在FPGA(现场可编程逻辑阵列)内部对数据进行分析处理后,再根据数据去向,重新生成48路子模块光纤信号,定向送至阵面48个SAM多功能板模块中的波控接口。数据分配器还从打包数据中解析出阵面延迟组件和矩阵开关的控制数据和时序信号,送至延迟放大组件和矩阵开关。另外数据分配器还负责采集阵面电源及组件的BIT信息,回传给时序监控模块。

数据分发层设备由48个波控接口组成。波控接口位于48块一体化设计可扩充SAM多功能板模块的内部,每个波控接口负责将数据分配器送来的子模块打包数据,解析为32路串行数据信号和时序信号,同步发送给多功能板模块内的32个T/R组件。波控接口完成对48组T/R组件的移相码分配和时序控制。

协议转换层设备指位于T/R组件内部的ASIC芯片,数量为48个,可以将波控接口送来的同步串行信号转换为并行数据,用来控制T/R组件内部的移相器、衰减器和多路开关,这部分功能由T/R组件设计自行完成。

1.2 移相码设计

波控系统根据天线波束指向信息,首先计算相应方位、仰角上的相位初始值,再根据初始值计算天线阵列中每个移相器单元的相位,最后控制驱动移相器移相,使天线波束指向规定的方向,实现天线在方位角φ和仰角θ这两个方向上的任意扫描[2]。

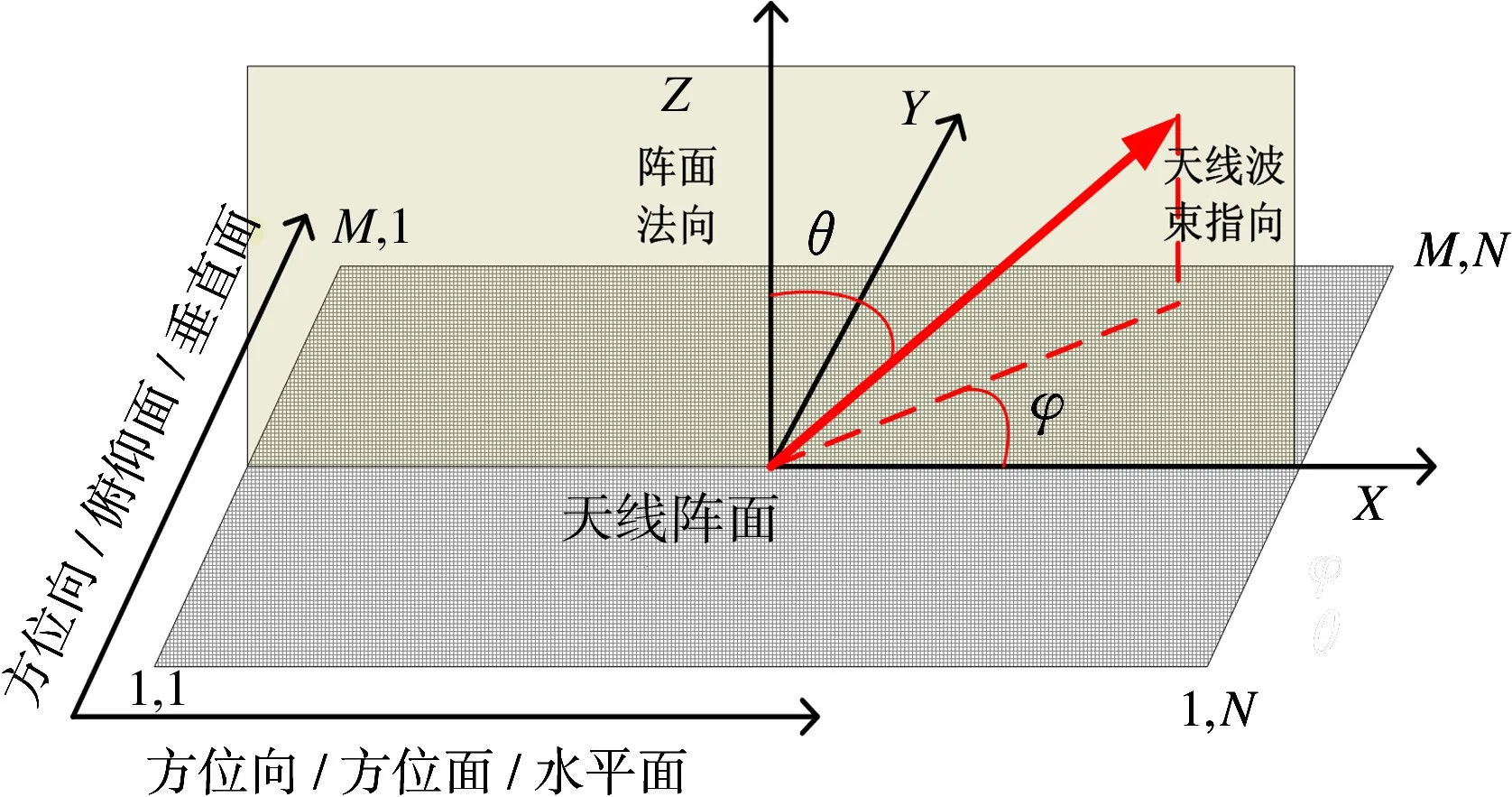

根据雷达总体要求,波控系统需要实现二维天线阵面的移相控制。整个阵面在XY平面上,共有16×72个天线单元,天线单元间距分别为dx(X轴方向)和dy(Y轴方向)。二维相控阵天线阵面天线单元排序及阵面坐标定义如图2所示。

图2 天线阵面天线单元排序及坐标图

在上述N行M列的相控阵天线中,若取阵面中心为坐标原点,当要求波束指向为θB和φB时,依据二维分离布相法则,则第n行的相位值为

第m列的相位值为

式(1)和式(2)中,

第n行第m列单元的相位值为

式(6)中相关参数dx,dy,N,M是确定的,n=1,2,…,16;m=1,2,…,72。

根据确定的波束指向和阵面参数,可以计算出阵面布相所需的单元相位值φm,φn和

实际扫描工作时,天线系统为了获得较低副瓣的天线波束,在由天线近场测试得出各天线单元的波程校正后,通过改变波控码来进行相位修正,使天线相位误差变为零。因此上式还应叠加上相位值Z(n,m),Z(n,m)为阵面中第(n,m)单元的移相器本身的校正同波程校正之和(该值为固定值,由天线实测数据确定)[4]。

本系统设计中,波控移相码的计算任务是嵌入在时序监控模块的软件处理中。时序监控模块在完成某个波束指向的移相码计算后,通过光纤数据通道,将移相码连同时序触发打包送给波控的数据分配器单元。

1.3 系统单元电路设计

依据分级架构设计思想,波控系统需要设计1个数据分配器和48个波控接口板。

1)数据分配器设计

数据分配器接收时序监控送来的波控码和波形码,经过数据解析和重新编码后,分发给波控接口板。数据分配器还收集波控接口的BIT信息,回传给时序监控模块,并产生2路阵面电源控制、以及4路延迟放大模块和1路矩阵开关的控制时序。数据分配器的功能框图如图3所示。其主要设计包括多路光纤收发模块和FPGA电路。

(1)多路光纤模块设计

数据分配器分发的光纤通道有48路,为了实现功能及满足小型化和环境适应性等的要求,多路光纤模块选用中航光电的HTA8528/8529型12路并行光模块。多路光纤模块共4组,用于数据分配器向波控接口板发送T/R相位码和时序信号等。模块的中心波长为850 nm,提供总速率达75 GB/s的数据传输。单个光模块使用集成的MT式尾纤接口,大大减小互联尺寸,封装形式为LCC48,有12个独立并行通道。

(2)FPGA电路设计

图3 数据分配器功能框图

设计使用的主控制选用Xilinx公司XC7VX485T芯片。该器件拥有485K个逻辑单元、8000Kb内核RAM、56个高速GTP(高速串行收发器),最大700个I/O等资源,可以满足系统48路光纤通道的设计需要。电路设计中最主要的任务是GTP模块设计和光纤数据分发传输设计,编程工具是ISE14.7。

①GTP模块设计

数据分配器调用芯片自带的软核GTP模块来实现光纤数据的处理,软核的配置应用依据厂家提供的手册进行。设计使用的GTP软核数量有49个,其中1个用于接收时序监控模块传来的指令数据,另外48路用于数据分发。设计的GTP模块数据宽度为16 bit,经8B/10B编码后,并行数据宽度为20 bit,采用2.5 GB/s的速率传输。

② 光纤数据分发传输设计

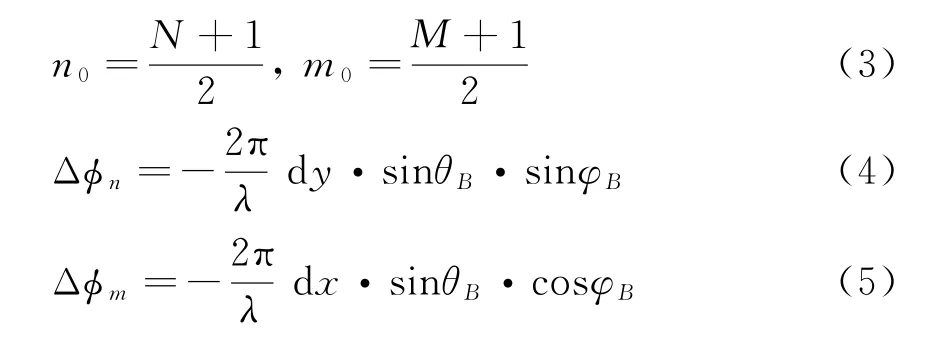

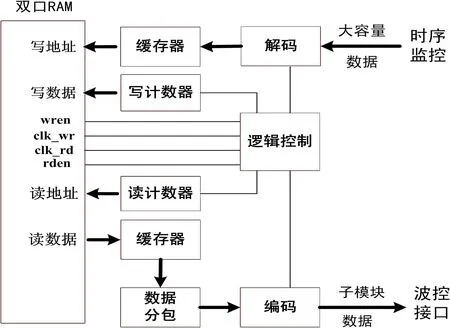

从时序监控模块传来的大容量数据和指令,经过解码和缓存后,首先按照指定规则存入双口RAM,而后根据时序要求顺序从RAM中读出。读出的数据先进行分组,再重新编码,经电光转换后发送至不同的波控接口。分发传输控制的逻辑图如图4所示。

电路中使用的双口RAM是一种可提供2组独立的控制线、地址线和数据线的存储器序列,其端口允许对存储器任一单元单独进行读/写访问,设计时RAM读操作快于写操作,保证了光纤数据的传输时间要求。

图4 分发传输控制的逻辑图

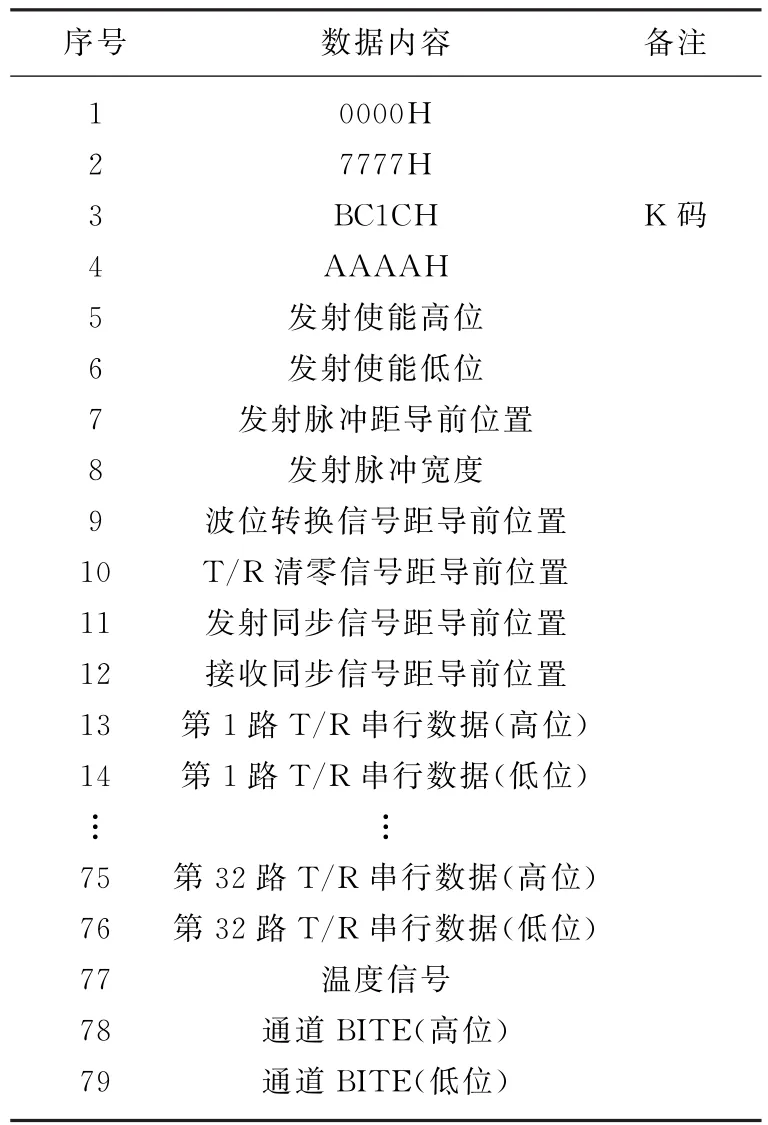

分组后的子模块数据还需通过特定的编码才能发给波控接口板,最终输出的子模块光纤数据包中除了有移相码、包头、包尾等信息外,还有采样频率、带宽等与数据处理有关的信息。表1就是数据分配器与波控接口板的子模块光纤数据传输协议。

表1 子模块光纤数据传输协议

2)波控接口板设计

波控接口板共设计为48块,位于SAM多功能板内部。每个波控接口板都通过1路光纤高速串行线,接收数据分配器送来的区段波控码和波形码,实现的功能有:解析SAM模块内每路T/R组件需要的移相码和衰减码,并将移相数据通过并串转换送至T/R的接口芯片;产生每路T/R组件需要的时序信号和开关信号,并将它们变换驱动后送至T/R的接口芯片;汇集每路T/R组件的BIT信息,打包后通过光纤回送给数据分配器。

(1)波控接口FPGA电路设计

波控接口板的主控制芯片选用了Xilinx公司XC7A200T型FPGA来进行设计。该型FPGA拥有200K的逻辑单元、2000Kb RAM、16个高速GTP收发器,最大500个I/O资源,配合外围的电平转换电路,可以满足数据处理和信号传输设计要求。

波控接口板中FPGA设计主要包含GTP收模块、GTP发模块和时序产生模块。GTP收模块解析数据分配器发送的光纤32路组件的相位码,并对它们进行并串转换。GTP发模块将SAM模块内部T/R组件回馈的BIT(机内信息检测)信息以及自身的BIT信息,通过光纤回送给数据分配器。时序产生模块根据接收到的波形码和导前信号,产生每路T/R组件需要的时序信号和开关信号。

(2)组件保护电路设计

T/R组件是天线系统中的关重件,其自保护能力比较弱,需要对它进行保护设计,波控对组件的保护主要通过以下方式实现。

① 功率电源开关控制

T/R组件的功率开关电源的打开时机,需要波控判断好其他系统状态都正常以后,才能由波控接口板执行电源的开关控制。

② 硬件时序保护控制

波控接口根据系统的工作模式,对T/R组件的功率开关脉宽进行限制,避免组件功率过高而损坏器件。

③ 上电过程电平保护

T/R组件对控制信号中最敏感的就是发射调制TRT信号,该信号要求在波控上电初始化的时候不能是高电平,否则组件会因功率过高而损坏。但由于波控的主控制FPGA芯片在上电配置期间,其IO输出的状态为不稳定态,所以必须要对其进行保护设计。设计时,首先将FPGA配置I/O电平控制PUDC接高电平,使配置期间所有的I/O处于浮空状态,然后将TRT的驱动芯片使能端接上拉电阻,输出接下拉电阻,确保配置期间TRT为低。

2 系统关键技术

波控系统中的关键技术是多路光纤传输技术。为满足小型化设计、一体化设计以及技术指标等的要求,波控设计使用了多组12合1光纤收发模块,实现了大容量数据的分发处理及时序控制任务。多路光纤传输技术的难度主要体现在大容量数据分发传输设计、多路高速通道布板设计、系统电源和时钟电路设计等方面。

1)大容量数据分发传输设计

波控设备中的光纤通道达48路,每路又分为收通道和发通道。高速通道中每个波位的数据长度达43 008 bit,这组数据中包含了多种模式、状态、频点、指向、带宽、移相码、位置、BIT等信息,其分发传输非常复杂,时序要求很高。波控在设计时,借助GTP软核,对多通道高速数据进行了编解码控制、相位对齐、串并转换、时钟激励、阻抗和电平匹配等措施,实现了快速准确的布相任务。

2)多路高速通道布板设计

由于设计中使用了大量的高速信号,波控在电路布板时,除了要进行信号分层设计外,还要对各路高速信号线进行屏蔽,充分考虑信号的走线,取最优最短的路径,并且避免信号间相互干扰。另外由于系统要求电源、微波、数字、光纤信号等进行一体化集成设计,设备电磁环境变得复杂,布局布线难度加大。在进行布板时,运用了多组电容、电感的滤波和信号屏蔽措施,满足了电磁兼容性要求。

3)电源和时钟电路设计

由于可编程电路及多种驱动电路芯片的大量应用,波控的电源达6个品种,全部由波控自己产生,为了保证电路的稳定性,电源设计时,不仅要考虑电源的带载能力,还要考虑不同电源的上电顺序、纹波要求、隔离要求,滤波电容和磁珠的使用位置、数量和容量等。另外由于高速数据通道多,时钟设计时要特别注意不同芯片之间的匹配电阻、电容和电平要求,其走线路径和屏蔽要求也非常严格。

3 结束语

采用分级架构设计的波控是实现中型及大规模相控阵雷达波控的有效途经之一。设计中采用光纤互联高速数据编解码控制技术,既实现了快速布相任务,又简化了阵面的走线,满足了快速灵活及小型化设计要求。系统中数据分配器单元的外形同SAM多功能板模块的外形大致相同,有利于阵面的总体结构设计。笔者依此思想设计的一套控制1 000多个移相单元的波控系统,经过一年多的验证,性能稳定可靠,完成了天线近场测试及雷达系统的外场联试,实现了对空中目标的观察。对于更大规模的天线阵面波控设计,只需要增加数据分配器单元及波控接口单元的数量即可,满足武器装备模块化的设计要求。

[1]陈俊,冯武.现代相控阵雷达天线波控技术研究[J].数字技术与应用,2014(2):64-67.

[2]段玲琳,段晓超.星载大型相控阵雷达波控系统设计研究[J].合肥工业大学学报(自然科学版),2014,37(3):319-322.

[3]张光义,赵玉洁.相控阵雷达技术[M].北京:电子工业出版社,2006:30-76.

[4]陈之涛,王雨阳,刘浩.一种发射通道校正技术的实现[J].雷达科学与技术,2012,10(3):332-335.CHEN Zhi-tao,WANG Yu-yang,LIU Hao.An Implementation of Calibration Method for Transmitting Channels[J].Radar Science and Technology,2012,10(3):332-335.(in Chinese)