基于超宽带采样保持器的数字接收机设计∗

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

软件无线电(SDR)是无线通信技术发展的重要方向。软件无线电的关键思想之一是将数据采集系统尽可能地向射频前端靠拢,因此直接射频采样技术逐渐成为数字接收机的重要发展趋势[1-2]。近年来,随着超宽带技术的发展,高速和宽带采样已经成为软件无线电的基本要求,但由于目前ADC器件的水平限制,采样率和带宽远远达不到实际应用的需求,因此直接射频采样技术在高速超宽带数据采集系统中的应用受到了很大的限制。

采样保持器(SHA)是ADC芯片的重要组成部分,采样保持器的性能直接影响着ADC芯片的转换速度和精度。本系统采用外置高性能采样保持器1821TH+ADC芯片的架构进行设计,弥补了原有ADC芯片模拟输入带宽不足的缺点,实现了超宽带信号的直接射频采样。

1 采样保持器

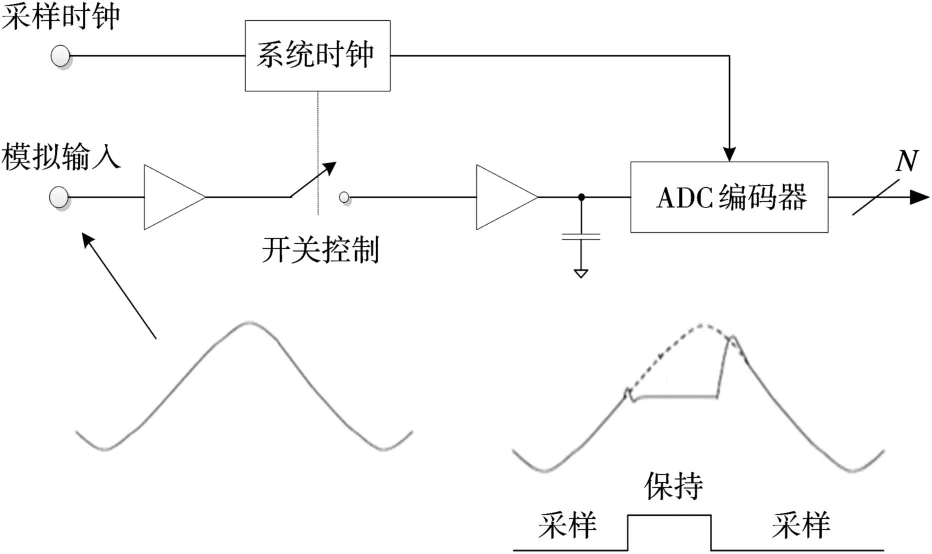

采样保持器的简易工作原理如图1所示[3]。采样保持器的作用是跟踪和保持模拟输入信号的电平值。其工作状态有采样状态和保持状态两种。采样状态和保持状态的工作周期等于采样时钟周期。采样开关导通时,为采样状态,此时采样保持器对模拟输入信号进行跟踪;采样开关断开时,为保持状态,采样保持器保持为断开瞬间的输入信号电平值。采样保持器的最大采样时钟由采样保持器的孔径抖动、带宽等因素决定[4]。

图1 采样保持器的工作原理

本系统中采用的采样保持器为Inphi公司生产的1821TH,最大采样率为2 GS/s。该芯片采用主从设计,包含两级采样保持电路。输入端可以是单端信号或差分信号,输出差分信号。主从两级采样保持器可以共用一路时钟,也可各自供应时钟。该采样保持器的模拟输入带宽对小信号可达18 GHz,对0.5 Vpp的信号可达15 GHz,对1 Vpp的信号可达12 GHz[5]。极宽的输入信号带宽,可以省去模拟下变频电路,降低设计复杂度,提高系统性能。

2 系统组成及工作原理

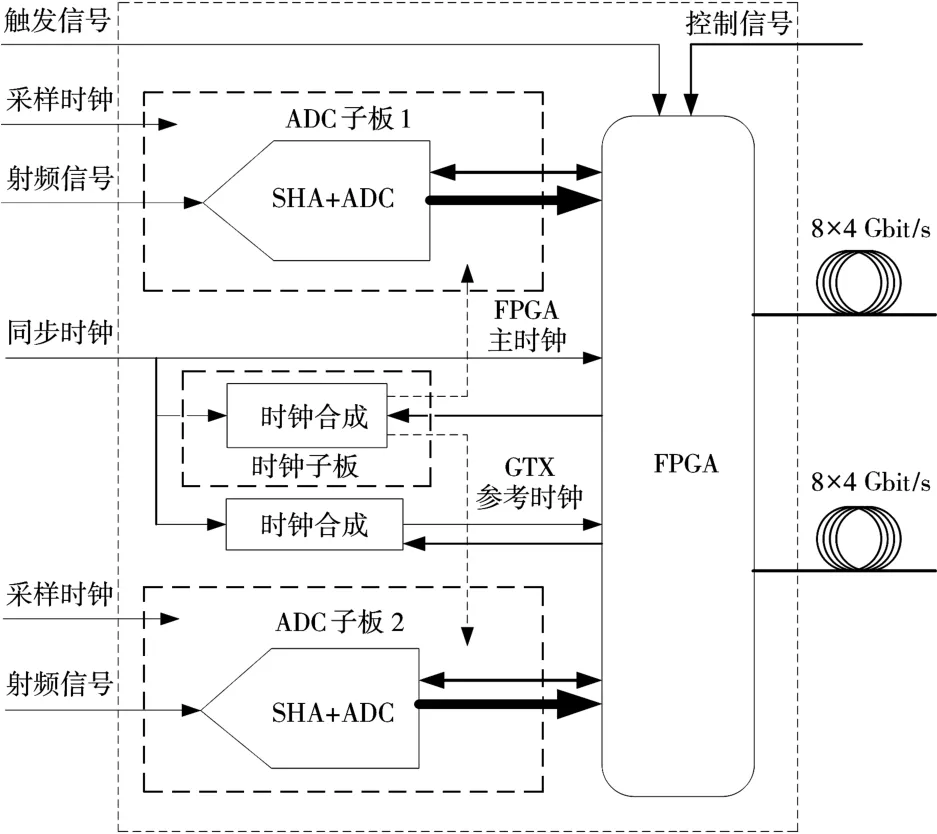

基于采样保持器的直接射频采样数字接收机是基于FMC架构进行设计的,其结构框图如图2所示[6]。FMC标准为ANSI标准,由FPGA厂家及其用户联合制订[7]。该接收机按照子母板架构进行设计,母板和子板之间通过FMC连接器相连。FMC母板为通用型电路板,FMC子板为功能性AD子板,另外预留一个时钟子板。在系统需求变化时,只需重新设计AD子板,降低了设计复杂度,节省了成本。

图2 基于FMC的数据采集系统框图

FMC母板包括一片Virtex-7和相应的配置电路、时钟管理模块、光模块、电源模块以及接口模块。在硬件上实现FMC子母板的电源供应和时钟供应功能、数据传输功能以及接口控制功能等。FPGA固件实现相关芯片配置、时钟信号管理、复位信号管理、数字下变频、数据缓存和传输等功能。由于FMC母板统一进行电源供应,可以输出3.3 V和1.8 V两种电压,因此,对于常规的数据采集设计,ADC子板不需额外进行电源电路设计。FMC母板上的时钟合成电路用于合成光纤传输的参考时钟,时钟子板对两个采样子板的采样时钟进行备份。通过FPGA配置,可以实现信号采样、数据处理和光纤传输的时钟全相参。

FMC母板上可以装载两个ADC子板,本系统只用到其中一个。直接射频采样数字接收机的ADC子板设计在第3节详细论述。

3 ADC子板设计

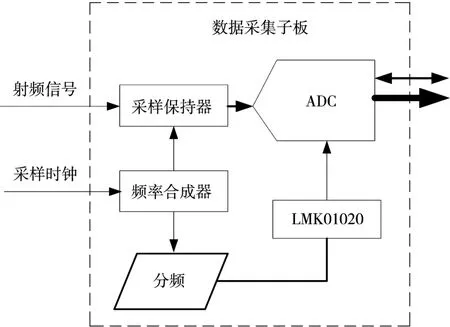

采用SHA+ADC架构的直接射频采样数字接收机通过一个FMC的ADC子板来实现,ADC子板的结构框图如图3所示。

图3 ADC子板的结构框图

从硬件上看,ADC子板可以分为数据通路和时钟通路。数据通路描述射频信号的处理流程。射频信号通过ADC子板的SMA连接器进入采样保持器,经过采样和保持,输出差分台阶信号,进入相对低速的ADC进行A/D变换,这样便弥补了低速ADC芯片无法采样高频信号的不足。ADC芯片采用国家半导体公司的8位双通道ADC——ADC08D1500。该芯片采样率最高可达1.7 GS/s。双通道ADC通过Time-Interleaved技术,采样率可以达到3 GS/s以上[8]。本设计中,双通道ADC的采样率均设置为1 GS/s,拼接后的采样率为2 GS/s。

时钟通路的功能是为数据采集子板的采样保持器和ADC供应时钟。频率合成器输出两路2 GHz的时钟信号,一路作为采样时钟供给采样保持器,另外一路送入分频器。频率合成器采用ADI公司的ADF4350,内置VCO,输出频带宽,可以覆盖137.5~4 400 MHz[9]。该路时钟经过二分频之后,进入LMK01020芯片。该芯片可以产生可控时延,用于调整采样点的位置。调整的基本原则是采样时刻对应输入台阶信号的中间附近。经过时延调整之后的1 GHz时钟信号送入ADC模块,作为ADC的采样时钟。

4 FPGA固件设计

本设计中的FPGA固件功能主要是时钟管理、复位信号管理、ADC芯片配置、时延芯片配置、数据解串和数据整理[10]。在实际应用中推广时,可以根据需求,增加数据传输和接口管理等功能,完成完整的固件开发。

另外,本设计采用Chipscope软件抓取FPGA中的信号进行实时查看,并可存取ADC数据到计算机进行频谱分析。

5 测试结果

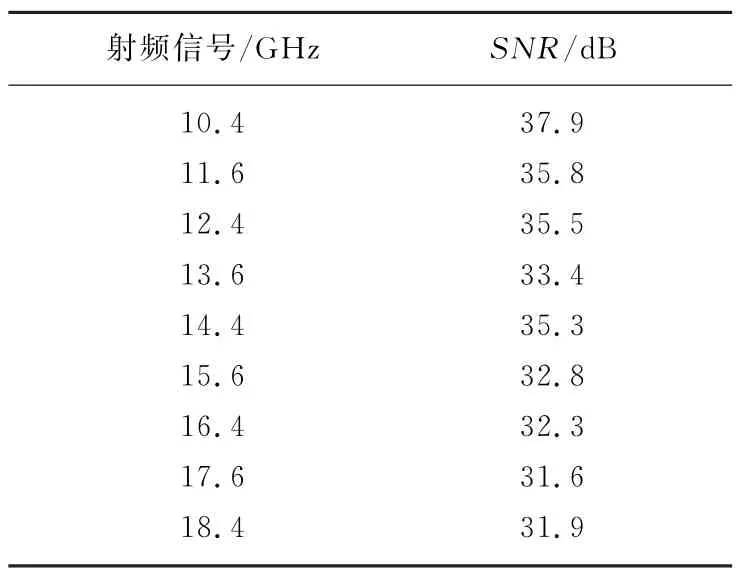

设计完成后,用信号发生器输入射频信号,进行数据采集,保存数据,用MATLAB对ADC数据进行频谱分析。数据采集过程中,对频率为0~18 GHz的射频信号进行了全面测试,本文中重点比较和分析频率高于10 GHz的高频信号。测试信号为点频。依次输入频率为10.4 GHz、11.6 GHz、…、18.4 GHz,且幅度为8 d Bm的信号,用2 GS/s采样率进行采集。测试结果如表1所示。

表1 不同频率射频信号的信噪比测试结果

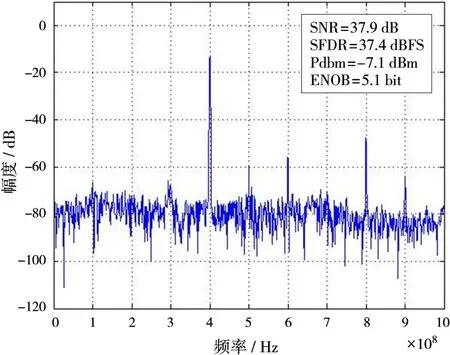

10.4 GHz射频信号输入时的频谱响应如图4所示。

图4 10.4 GHz射频信号输入的频谱响应

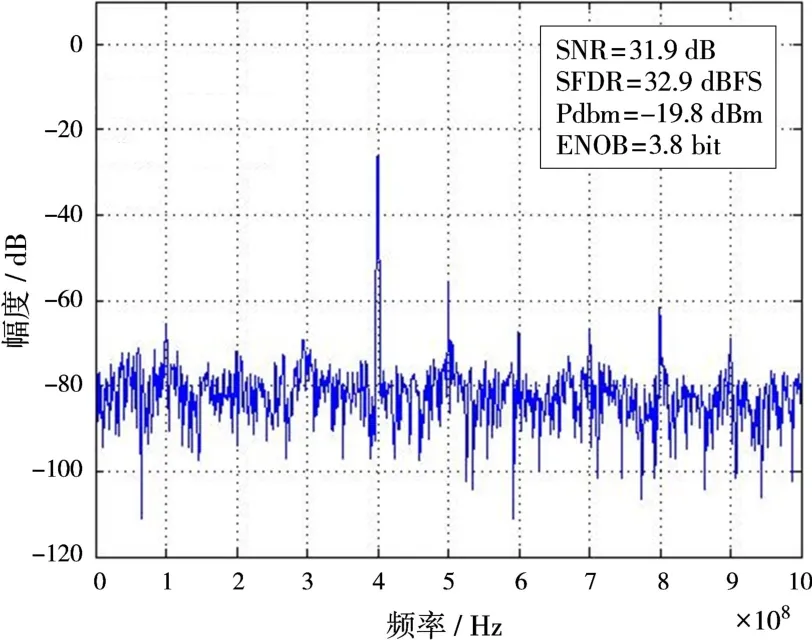

18.4 GHz射频信号输入时的频谱响应如图5所示。

图5 18.4 GHz射频信号输入的频谱响应

从表1可以看到,输入信号为10.4 GHz时,信噪比可以达到37.9 d B,信号频率逐渐增加到18.4 GHz时,信噪比也基本随之下降。信号频率小于15 GHz时,信噪比基本在35 d B以上,对8位ADC芯片而言,可以满足常规的数据采集设计需求。输入信号频率增加到15 GHz以上时,信噪比下降剧烈。对比图4和图5,信号频率为10.4 GHz时,输入信号功率约为-7.1 d Bm,而信号频率为18.4 GHz时,输入信号功率下降到-19.8 dBm。因为信号源带宽限制,信号功率下降明显,影响了信噪比的测试。由此,本设计实现了低速ADC对宽波段射频信号的直接采样。

需要说明的是,本文设计的数字接收机可以接受超宽带的射频信号输入,但由于采样保持器1821TH的最大采样率为2 GS/s,因此,输入射频信号的带宽不能超过1 GHz。

6 结束语

本系统采用高性能的采样保持器,基于SHA+ADC的架构,设计了一种支持超宽带信号输入的数字接收机,用低速ADC芯片实现了射频信号的直接采样。本文首先介绍了超宽带数据采集系统的组成和工作原理,然后重点介绍了宽带数据采集子板的硬件设计,简要介绍了FPGA的固件设计。测试结果显示,输入信号频率增加到14.4 GHz时,接收机信噪比仍可达到35 dB以上,可以满足常规数字接收机的系统需求,具有一定的应用价值。

[1]TSUI J.宽带数字接收机[M].杨小牛,陆安南,金飚,译.北京:电子工业出版社,2002:7-13.

[2]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:28-31.

[3]赵岩,敬守钊.高速采样保持电路设计[J].测试测量技术,2011(9):4-6.

[4]SHEINGOLD D.Analog-Digital Conversion Handbook[M].3rd ed.Englewood Cliffs,NJ:Prentice-Hall,1986.

[5]INPHI PROPRIETARY.1821 TH 18 GHz Bandwidth 2 GS/s THA Datasheet[EB/OL].2007-01-17.http:∥www.inphi.com/products-technology/multimarkets-test-measurement-military-aerospace/trackand-hold-amplifiers/1821-th-s01bga.php.

[6]向海生,马利祥,王冰.基于拼接采样技术的宽带数字接收机[J].雷达科学与技术,2014,12(4):450-453.XIANG Hai-sheng,MA Li-xiang,WANG Bing.A Wideband Digital Receiver Based on Time-Interleaved Sampling Technique[J].Radar Science and Technology,2014,12(4):450-453.(in Chinese)

[7]VITA.FMC Marketing Alliance[EB/OL].2010-02-18.http:∥www.vita.com/fmc.

[8]TEXAS INSTRUMENTS.ADC08D1500 High Performance,Low Power,Dual 8-bit,1.5 GSPS A/D Converter[EB/OL].2009-04-20.http:∥www.ti.com/lit/ds/symlink/adc08d1500.pdf.

[9]ANALOG DEVICES.Wideband Synthesizer with Integrated VCO:ADF4350[EB/OL].2008-11-08.http:∥www.analog.com/media/en/technical-documentation/data-sheets/ADF4350.pdf.

[10]张奕,谭剑美.DAM中多通道数字收发的设计与实现[J].雷达科学与技术,2012,10(3):320-323.ZHANG Yi,TAN Jian-mei.Design and Implementation of Multi-Channel Digital Transceiver in Digital Array Radar[J].Radar Science and Technology,2012,10(3):320-323.(in Chinese)