基于平均功率控制的中频逆变器主从并联系统研究

龙江涛,蔡环宇,何昕东,石健将

(浙江大学电气工程学院,杭州 310027)

基于平均功率控制的中频逆变器主从并联系统研究

龙江涛,蔡环宇,何昕东,石健将

(浙江大学电气工程学院,杭州 310027)

在航空航天等特殊应用领域里通常需要电源系统提供高质量、高可靠性的400 Hz中频交流电源输出,而逆变器的并联控制技术可实现冗余供电和大容量供电,是当今逆变电源发展的重要方向之一。首先,对逆变器主从并联系统的整体结构进行分析和设计以实现良好的信号传输和冗余控制;其次,针对单台中频逆变器模块,采用了基本PR控制器的电压电流双闭环控制策略以改善其输出特性;随后,对基于平均功率控制策略的逆变器主从并联系统进行系统分析,并在从机控制系统里引入虚拟阻抗以改善其输出特性;最后,通过仿真和实验验证逆变器并联系统结构和控制策略的可行性。

中频逆变器;主从并联;PR控制;平均功率控制

引言

400 Hz中频交流电源广泛用于航空、机场、船舶机车等交流供电系统中。由于应用场合较特殊,电源系统能否稳定持续供电至关重要,因此对交流电源的输出波形质量和系统可靠性提出了更高的要求。而逆变器并联控制技术可实现冗余供电和大容量供电,是上述要求的解决方案之一。

现有的电压源型逆变器并联控制方法按有无线互连线的区别划分为2种:无线并联技术和有线并联技术。无线并联技术一般使用无线下垂控制,此种控制方式具有无互联线和较易实现分布式并联的优势,但逆变器输出电压的幅值和频率会随着输出有功和无功功率的大小而波动,不适用于中频供电系统[1-2];有线并联技术主要分为集中控制方式、主从控制方式、分布式控制方式。集中控制方式由于没有冗余能力,一旦公共控制电路失效,整个并联系统瘫痪,因而使用范围很受限制;分布式控制虽然可以实现完全的冗余并联,但是其共享基准正弦波信号、基准电流信号以及相位信号的产生都有相当程度的误差,其动态响应也不够理想[3-4]。主从控制方式的逆变器并联系统输出电压幅值、频率精度仅取决于主模块,因而在设计逆变器时只需要将逆变器单机特性设计好即能实现较好的输出波形质量,若再加上适当的逻辑控制就可以实现冗余并联,极大提高并联系统可靠性。同时利用主从机通信的特点还可以实现不同容量逆变器并联时功率不均等分配。逆变器并联均流实现方法主要有瞬时电流均流法和平均功率法[5]。瞬时电流均流法通过各模块输出电流与参考电流的误差调整参考电压的,幅值和电流实现均流。由于逆变器模块间传输的电流信号一般为模拟信号,当有多机并联或逆变器模块距离较远时,均流信号很容易受到干扰[6-8];平均功率法则是利用得到的平均有功和无功功率来调节输出电压的幅值和相位,从而实现功率均分[9],由于其通信一般是基于通信协议的数字信号,因而具有较强的抗干扰能力。

本文首先针对逆变器主从并联系统的需要设计一套高可靠性的信号传输与可冗余逻辑控制方案;其次对单台中频逆变器系统进行分析和设计,通过基于PR控制器(比例谐振控制器)无静差控制控制,通过电压电流双闭环控制实现较好的控制效果;在单机的基础上对主从控制方式下的逆变器并联系统进行分析,并在从机控制系统引入虚拟阻抗以改善其输出特性;最后通过仿真和实验来验证上述设计的可行性和正确性。

1 主从并联系统整体结构设计

有线并联方案中逆变器间的互联信号传输的可靠性直接影响到并联的可靠性和均流效果,因而其整体结构设计至关重要。传统的有线并联方式里将同步时钟信号与均流信号分别传递,这就需要两套通信线,而且期间任何一套通信线故障整个系统即故障,大大增加了系统瘫痪风险。本文的设计思路是通过一定的信号处理将同步时钟信号与均流信号复合传输,可以简化逆变器间的互连线,提高系统可靠性。

1.1 逆变器并联系统整体结构

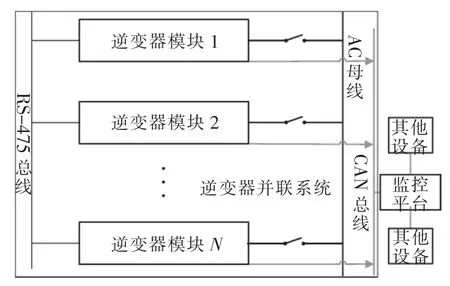

逆变器并联系统整体结构如图1所示。

图1 逆变器并联系统整体结构Fig.1 Whole structure of inverter parallel system

逆变器模块间是无差别的。逆变器模块均通过CAN通信协议芯片连接到监控平台上,通过接触器连接到AC母线上,通过RS-485通信协议芯片连接到RS-485总线上。监控平台作为人机互动的接口,通过监控平台可以向下属设备发送开机或停机指令,同时下属设备也向监控平台反馈运行状态信息。逆变器模块与AC母线间的接触器由逆变器模块分别控制。当模块启动后会检测AC母线电压是否正常,若正常即闭合接触器,控制环路中的均流环路自动运行。若任意模块故障,则可以通过断开接触器使故障模块脱离并联系统。逆变器模块间的信号传输是通过RS-485总线实现的。在运行过程中RS-485总线上由主机发送数据,从机接收数据,从而形成一主多从的数据收发系统。在这套通信系统里主机可任意指定,因而可以实现冗余式并联。

1.2 逆变器并联系统通信设计

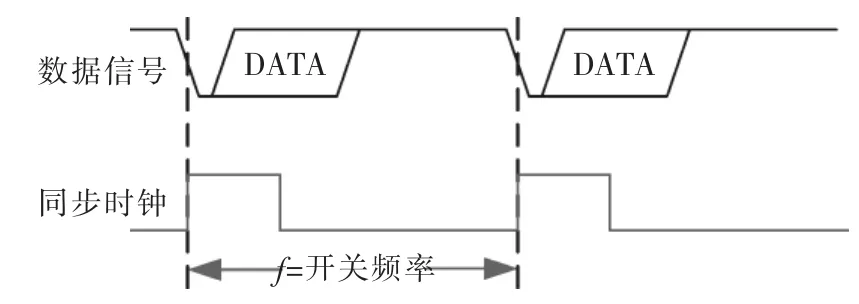

逆变器间的通信信号连线如图2所示。通过将同步时钟信号与均流信号复合传输使得只通过一对差分信号线即可满足通信要求。

图2 逆变器间的通信信号连线Fig.2 Communication signal connection of inverters

使用上述通信信号传输系统有以下优势:(1)各模块的信号传输机制具有一致性,使冗余并联成为可能;(2)将同步时钟信号与数据信号复合传输,因而逆变器模块间的通信线路只有一套,降低了通信互连线的数量,提高了系统的可靠性;(3)RS-485总线使用差分信号来传输数据,有较强的抗干扰能力;(4)隔离RS-485收发器芯片实现了控制信号与通信信号间的电气隔离,防止不同逆变器间的干扰信号耦合;(5)使用异步收发传输器UART协议作为上层通信协议,因DSP模块都自带有UART模块并可设定奇偶校验位,可有效保证接收到数据的准确性。

使用复杂可编程逻辑器件CPLD提取时钟信号的时序如图3所示。根据UART协议,发送数据信号时通信线上的电平会由高低电平变为低电平并维持一个通信波特率周期,同步时钟的上升沿由数据信号的下降沿产生,本文使用的逆变器模块开关频率为20 kHz,因而通信数据传输间隔亦为20 kHz,经过CPLD处理后会产生频率为20 kHz的同步时钟信号。错误的通信数据序列会使同步时钟信号的间隔发生变化,从而为冗余逻辑规则实现自动择主提供判断依据。

图3 同步时钟信号时序Fig.3 Synchronous clock signal timing

1.3 冗余逻辑规则设计

传统的主从并联控制在主机故障后并联系统即瘫痪,因而其可靠性和实用性大大降低。本文通过设定合适的冗余逻辑规则,使逆变器关联系统在任意模块发生故障后依然能可靠运行。其逻辑规则判断流程如图4所示。

图4 冗余逻辑规则判断流程Fig.4 Flow chart of redundant logic rule judgment

逆变器模块在启动时通过监听通信互联线上是否有同步时钟信号来区分主从机。如果并联系统中没有主机,则在限定的持续检测时间Td(约为1.1~1.5Tp,Tp为开关周期)内无同步时钟信号,从而设定为主机;如果系统中有主机,则在Td时间内必然会检测到一次同步时钟信号,从而设定为从机。逆变器模块在运行过程中将持续检测同步时钟信号以判断是否出现故障。常见的主从控制逻辑故障有2类:(1)逆变器并联系统里没有主机的故障;(2)逆变器并联系统里有2台或多台主机的故障。当主机故障退出时会发生第1类故障,这时从机在检测同步时钟信号时会等待超过1.2Tp,从而判定主机已故障,最先检测到这一状态的从机会作为主机向外发送同步时钟信号,从而使并联系统继续正常运行。发生第2类故障时,主机会检测到同步时钟信号时间间隔小于0.8Tp,从而判定并联系统上至少有2台主机,本机则退出主机状态并进入自动择主程序,若通信线路正常,则故障会消失,否则故障会依然存在,此时监控平台会在连续几个开关周期内检测到多台主机出现故障的存在,从而进行故障处理。在逆变器单个模块故障时,故障处理至多2个开关周期内各模块需要依照自身的信息调整参考相位,由于不同系统间的晶振频率差别很小,在短时间内只会产生微小的相差。

2 逆变器单机控制设计

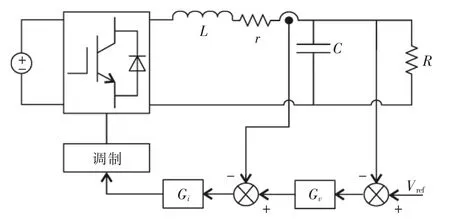

传统的PI控制器在输出直流控制系统里可以实现无静差控制,但用于逆变器控制系统时会存在稳态误差问题。中频逆变器控制系统中由于基波频率更接近剪切频率,其基波频率处增益较工频逆变器会更低,稳态误差会更大。因此希望使用对交流信号无静差的控制器,PR控制器正好能满足这一要求[10]。本文采用了基本PR控制器的电压电流双闭环控制策略以改善中频逆变器的输出特性:通过在电压单环基础上增设电感电流内环,利用电流内环快速性和抗干扰性来有效地抑制负载扰动影响[11],其反馈框图如图5所示。

图5 电压电流双环控制结构框图Fig.5 Block diagram of voltage current double loop control structure

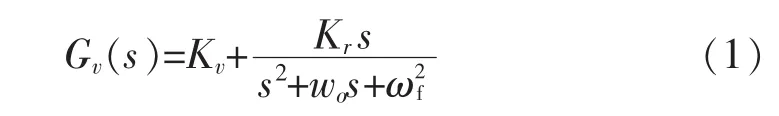

电压外环使用比例谐振控制器,其传递函数为

闭环设计中电流内环的速度要比电压外环快很多,使用比例环节即可有较好的控制效果。本文的电流内环使用单比例环节,其传递函数为

本文将负载电流io作为系统的一个外部扰动输入量进行建模,可得到控制模型控制框图如图6所示。

图6 基于PR控制器的电压电流双闭环控制框图Fig.6 Block diagram of voltage current double closed loop control based on PR controller

根据图6可以推导出参考电压扰动到输出电压扰动的开环传递函数,即

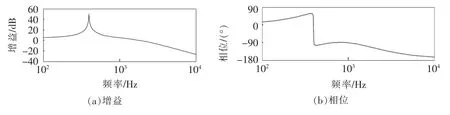

将电气参数和设计控制参数代入式中,可以得到典型的逆变器系统开环Bode图,如图7所示。

图7 逆变器控制系统开环Bode图Fig.7 Bode diagram of inverter control open-loop system

3 逆变器主从并联系统

3.1 逆变器等效模型

根据图6可以推导出逆变器系统输出电压在参考电压与负载电流双输入作用时的对应关系,即

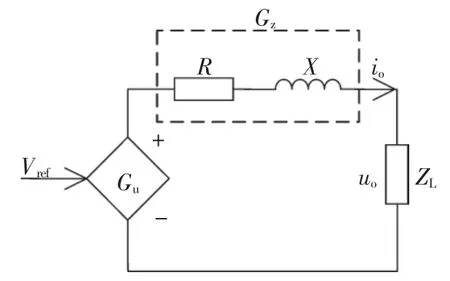

式中:Gu(s)为电压基准扰动到输出电压扰动的闭环传递函数;Gz(s)为输出电流扰动到输出电压扰动的闭环传递函数。

由图7可以看出,电压外环在使用PR控制器后逆变器系统在基频处的增益非常高。通过式(4)可以得出逆变器系统的戴维南等效电路如图8所示。图中等效电压源为Gu(s)Vref,等效电阻为Gz(s)。

通过计算可以得出Gu(s)和Gz(s)在基频处的确切值,即

图8 逆变器戴维南等效电路模型Fig.8 Model of inverter Thevenin equivalent circuit

由式(5)可得,Gu(s)近似为1,Gz(s)近似为0。结合逆变器戴维南等效电路模型可近似认为输出电压即为参考电压,且基本不会随负载变化而变化。

3.2 从机虚拟阻抗的引入

逆变器并联时其输出电压的幅值和相位略微不同时,较小的输出阻抗会引起逆变器之间较大的有功和无功环流。特别是在并联瞬间不同逆变器的输出电压幅值和相位很难保证完全一致。本文通过在从机引入虚拟阻抗来抑制并联时因输出电压不一致引起的环流问题,使逆变器并联时能平稳到达稳态[12]。虚拟阻抗的引入会对逆变器的输出阻抗产生影响。引入虚拟阻抗的逆变器控制模型框图如图9所示。

引入虚拟阻抗后等效参考电压变为

图9 加入虚拟阻抗的逆变器控制框图Fig.9 Block diagram of inverter control with virtual impedance

将式(6)代入式(4),得

一般地,引入的虚拟阻抗特性为感性或阻性。当其使用感性虚拟阻抗Rv时可近似为一超前环节,存在造成逆变器系统不稳定的问题;当其使用阻性虚拟阻抗Rv时可为一常数,存在带载情况下输出电压跌落的问题[13-14]。由于本文使用的是主从并联模式,并联系统输出电压由主机决定,因而可以直接使用阻性虚拟阻抗。通过引入虚拟阻抗使从机等效输出阻抗特性恒定,从而保证功率均分环可靠工作。

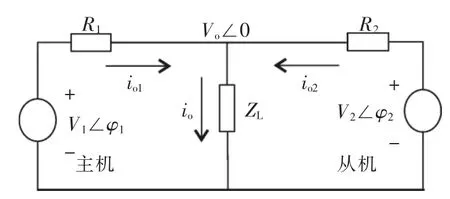

3.3 主从控制功率均分原理

由式(5)、式(7)可知,逆变器主机和从机的输出阻抗特性均近似为阻性。以2台逆变器主从机并联为例,其等效模型如图10所示。

根据上述模型可以推导出逆变器输出功率表达式,即

图10 逆变器主从机并联等效模型Fig.10 Equivalent model of inverters in master-slave parallel

由于逆变器等效电压源电压与母线电压的相位角φ1和φ2均很小,定义2台逆变器输出的幅值差和相位差分别为ΔVi和Δφi,则式(8)可以简化为

由式(9)得

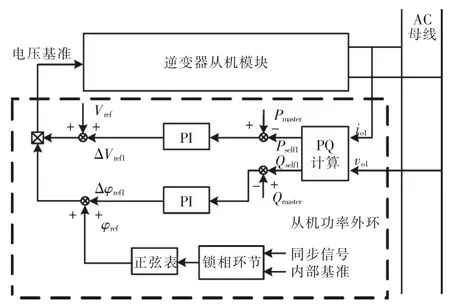

由式(9)、式(10)可知,逆变器的输出有功功率与电压幅值偏差正相关,无功功率与电压相位偏差负相关,可以通过调节从机输出电压幅值可实现主机与从机有功功率均分,调节从机输出电压相位可以实现无功功率均分。因此逆变器模块从机只需要在电压电流双闭环控制外加上功率外环来调整参考电压幅值和相位,即可以实现主机与从机功率均分。加入平均功率控制策略的逆变器从机控制框图如图11所示,图中并联控制中从机所需要的主机有功功率和无功功率数据由RS-485总线传输得到。

图11 加入平均功率控制策略的逆变器从机控制框图Fig.11 Block diagram of inverter slave machine control with average power control strategy

4 实验结果

为了验证上述方案的正确性和有效性,本文使用基于Matlab软件中的Simulink模块搭建了仿真模型,并使用基于TMS320F28335控制平台设计了2台功率为3 kW的三相四线T型三电平中频逆变器实验样机,并在此基础上进行了单机与并联实验。

表1 仿真与实验的样机参数Tab.1 Simulation and experimental prototype parameters

4.1 单机仿真与实验

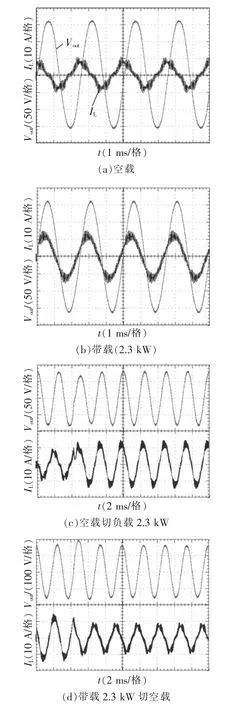

逆变器单机仿真波形如图12,其中实线为逆变器A相电感电流和输出电压波形,虚线为参考电压波形。通过使用PR控制器,输出电压与参考值之间的稳态误差得到完全消除,负载变化时的响应速度也很快。

图12 逆变器单机仿真波形Fig.12 Stand-alone Inverter simulation waveform

逆变器在空载、带载以及负载变化条件下的A相输出电压波形如图13所示。空载情况下输出电压THD为2.1%,带载情况下输出电压THD为1.4%。由负载突变实验可知,逆变器在负载变换时输出电压幅值相位基本稳定,动态响应性能良好。

图13 逆变器单机实验波形Fig.13 Stand-alone inverter eperiment waveforms

4.2 并联系统仿真与实验

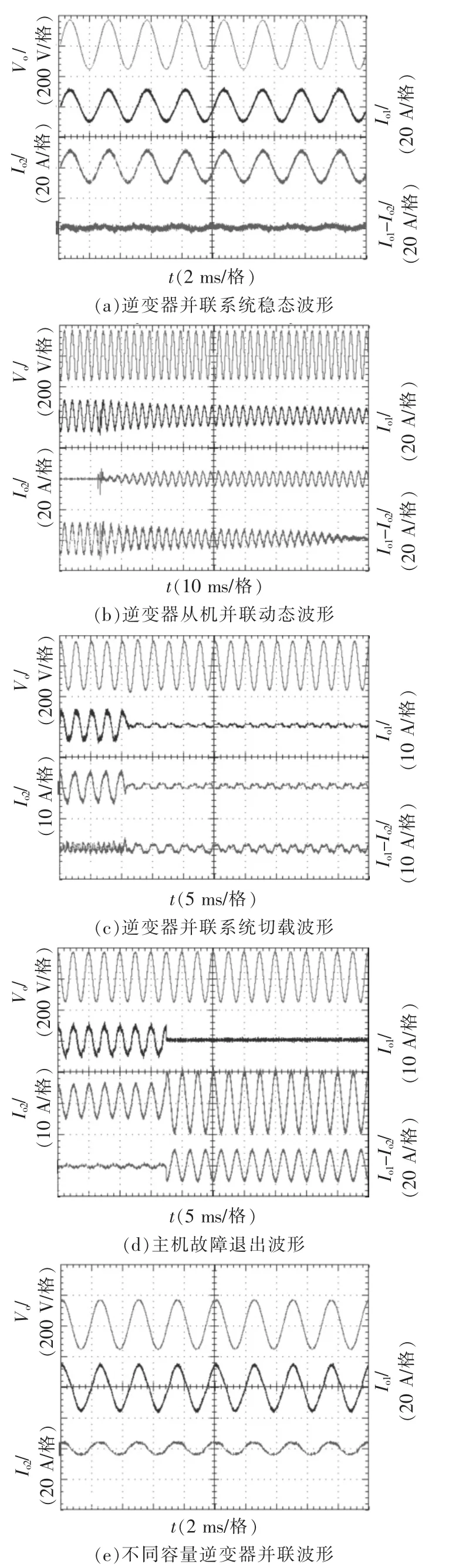

图14为采用基于平均功率控制的逆变器主从并联系统仿真波形。由上到下依次为A相的输出电压波形、主机和从机负载电流波形、主机和从机输出有功功率波形。由图14可见,并联系统的并联过程平稳,均流效果好。

图14 逆变器并联系统仿真波形Fig.14 Simulation waveforms of inverter parallel system

图15为逆变器并联系统的单相实验波形。图15(a)为逆变器并联系统带载4.6 kW稳态波形,图15(b)为逆变器主机带载2.3 kW后从机并联时的动态波形,由于均功率外环开始工作与继电器合闸时间不一致,因而并联后调节时间会略长。图15(c)为逆变器并联系统带载2.3 kW切空载波形。图15(d)为模拟主机故障退出时逆变器并联系统动态情况。图15(e)为模拟不同容量逆变器并联情况:并联系统总功率为4.6 kW时从机跟踪主机功率并限定最大输出功率1 kW时的实验波形。实验结果表明:逆变器并联系统输出电压良好;并联的稳态均流效果良好;并联的动态过程平稳,稳定性高;通过逻辑规则可以实现冗余并联;根据逆变器容量不同能够进行功率分配优化。

5 结语

本文主要研究了中频逆变器主从并联控制技术。首先,针对逆变器有线并联时互连线复杂繁多的缺点,通过将同步时钟信号和均流信号进行复合传输以减小通信互连线数量,同时设置合适的逻辑规则以实现主从模式控制下的冗余并联功能,提高并联系统可靠性;其次,针对单台逆变器模块使用基于PR控制器的电压电流双闭环控制实现对参考电压的无静差跟踪。在逆变器单机的基础上,对逆变器主从并联系统进行了环流分析,并验证了基于平均功率控制的逆变器主从并联控制策略可行性。最后,仿真和实验结果验证了整体结构设计的合理性以及单机和并联系统中控制策略的可行性与可靠性。

图15 逆变器并联系统实验波形Fig.15 Inverter parallel system experiment waveforms

[1]张尧.基于逆变器并联系统的网络控制技术及其相关问题的研究[D],杭州:浙江大学,2010.Zhang Yao.Research on Networked Control Technique and Correlated lssues Based on Inverter Paraller Operation System[D].Hangzhou:ZhejiangUniversity,2010(inChinese).

[2]王文杰,龙江涛,石健将.基于PR控制和平均功率控制的中频逆变器并联系统研究[J].电源学报,2013(03):5-12.Wang Wenjie,Long Jiangtao,Shi Jianjiang.Research on paralleled middle-frequency inverters system based on PR and average power control strategies[J].Journal of Power Supply,2013(03):5-12(in Chinese).

[3]方天治,阮新波,肖岚,等,一种改进的分布式逆变器并联控制策略[J].中国电机工程学报,2008(33):30-36.Fang Tianzhi,Ruan Xinbo,Xiao Lan,et al.An improved distibuted controlstrategy ofparallelinverters[J].Proceedings of the CSEE,2008(33):30-36(in Chinese).

[4]方天治,阮新波,肖岚.分布式三相逆变器冗余并联系统[N].南京航空航天大学学报,2012(06):840-846.Fang Tianzhi,Ruan Xinbo,Xiao Lan.Distributed redundant parallel three-phase inverters system [J].Journal of Nanjing University of Aeronautics& Astronautics,2012(06):840-846(in Chinese).

[5]汪东,邓焰,何湘宁,等.逆变电源并联技术的现状与发展[J].电力电子,2007(03):8-13.Wang Dong,Deng Yan,He Xiangning,et al.Present state and future development of parallel inverters technology[J].Power Electronics,2007(03):8-13(in Chinese).

[6]Quesada J,Sainz J A,Sebastian R,et al.Application of real-time fault-tolerant distributed control in parallel operation of inverters[C].IECON 2013-39th Annual Conference of the IEEE.2013.Vienna:471-476.

[7]Roslan,Azrik M,Ahmed K H,et al.Improved Instantaneous Average Current-Sharing Control Scheme for Parallel-Connected Inverter Considering Line Impedance Impact in Microgrid Networks[J].IEEE Transactions on Power Electronics,2011,26(3):702-716.

[8]Hongtao S,Yong K,Shanxu D,et al.Research on a novel digital parallel current sharing control technique of modularized UPS[C].ICEMS.2007.Seoul:106-109.

[9]于玮,徐德鸿,周朝阳.并联UPS系统均流控制[J].中国电机工程学报,2008,28(21):63-67.Yu Wei,Xu Dehong,Zhou Zhaoyang.Control strategy of paralleled UPS system[J].Proceedings of the CSEE,2008,28(21):63-67(in Chinese).

[10]Chunxi L,Chi S,Wenhua H.Proportional-resonant controller of high power 400Hz inverter in stationary frame[C].ICEMS 2008.Wuhan:1772-1777.

[11]刘韬,郝翔,杨旭,等.LCL滤波的三相并网逆变器电流双环控制策略[J].电源学报,2012(4):7-12.Liu Tao,Hao Xiang,Yang Xu,et al.Current dual-loop control strategy for three-phase grid-connected VSI with LCL filter[J].Journal of Power Supply,2012(4):7-12(in Chinese).

[12]Xiongfei W,Blaabjerg F,Zhe C.An improved design of virtual output impedance loop for droop-controlled parallel three-phase voltage source inverters[C].ECCE,2012.Raleigh:2466-2473.

[13]Hongtao S,Fang Z,Dong Z,et al.Adaptive implementation strategy of virtual impedance for paralleled inverters UPS[C].ECCE,2014.Pittsburgh:158-162.

[14]Zeng L,Jinjun L,Hao W.Output impedance modeling and stability criterion for parallel inverters with average load sharing scheme in AC distributed power system[C].APEC.2012.Orlando:1921-1926.

Research on Master-slave Paralleled Middle-Frequency Inverters’System Based on Average Power Control Strategies

LONG Jiangtao,CAI Huanyu,HE Xindong,SHI Jianjiang

(College of Electrical Engineering,Zhejiang University,Hangzhou,310027 China)

High quality and high reliability 400 Hz frequency AC power supply is strongly demanded in the field of aerospace,ships,radar,petroleum,metallurgy,communications switches and other power systems.The control technology of Paralleled inverters can make power supply more redundant and higher capacity,which is one of inverter's development trends.In the paper,the overall structure is designed for the Master-slave Paralleled Middle-Frequency Inverters’System to realize a redundant signal transmission and logic control.Voltage and current double closed-loop control strategies based on PR controller is used for a single inverter to improve its output characteristics.The paper establishes the mathematical model of the two paralleled inverters’system and designed a suitable scheme based on the average power control.Virtual impedance is added in the slave module’s control loop to improve the output performance.Finally,the validity of the designed system structure and control schemes are verified by the simulation and experiment results.

middle frequency inverter;master-slave parallel method;PR control;average power control

龙江涛

龙江涛(1989-),男,硕士研究生,研究方向为逆变控制,E-mail:lightna@zju.edu.cn;

蔡环宇(1990-),男,硕士研究生,研究方向为PWM变流器,E-mail:jlyz11bc hy@zju.edu.cn;

何昕东(1992-),男,硕士研究生,研究方向为开关变换器,E-mail:hxd5626 83202@163.com;

石健将(1969-),(通信作者)男,博士,教授,博士生导师,研究方向为电力电子变换器、特种电源,E-mail:jianjiang@zju.edu.cn。

10.13234/j.issn.2095-2805.2015.2.1

:TM 344.1

:A

2014-07-05

国家自然科学基金项目(51277162)

Project Supported by National Natural Science Foundation ofChina(51277162)