基于FPGA的高速数据流差错注入器设计

邓彬伟,刘崇汉

(1.湖北理工学院 电气与电子信息工程学院,湖北 黄石435003;2.南方卫理公会大学 物理系,德克萨斯州 达拉斯75275)

0 引 言

在高辐射下的高速传输问题则是目前国内外,特别是高能物理实验方面要解决的关键问题之一[1-3]。欧洲核子中心的LHC (大型强子对撞机)项目正面临这一挑战[4,5]。LOC即芯片链路 (link-on-chip)是针对LHC ATLAS项目中更新的每FEB2 100Gbps数据带宽的光纤链路设计项目的一个概念[6,7]。其中,LOCic是针对ATLAS液氩量能器前端电子单元的一个两通道耐辐射低功耗高速串行传输器[8]。它针对前端系统的AD 采样数据进行组帧,接着通过高速串行化单元后使用光纤进行每通道高达5Gpbs的传输。由于在强微粒子辐射环境下发送数据时,数据流中会发生数据位上的连续多位差错和数据流位滑动错误,因而在后端需通过解码和数据恢复处理。针对以上情况,本文基于Stratix II GX FPGA 设计了模拟以上差错现象的差错注入器,用于后端数据解码和恢复系统的设计与测试。整个差错注入器通过按键控制和模拟可预置突发的数据流中1位和多位差错、数据流的1次和多次1位左或右移位滑动。在Stratix II GX FPGA开发板上采用高可靠的SignalTapII[9,10]进行大量测试和实验,结果表明差错注入器有效可行。

1 LOCic FPGA 系统简介

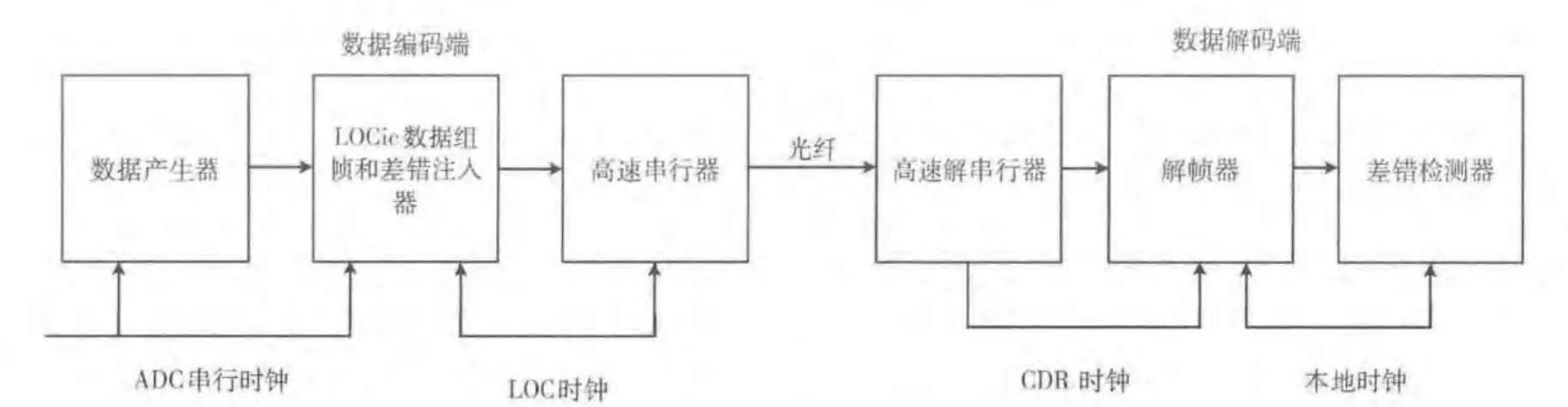

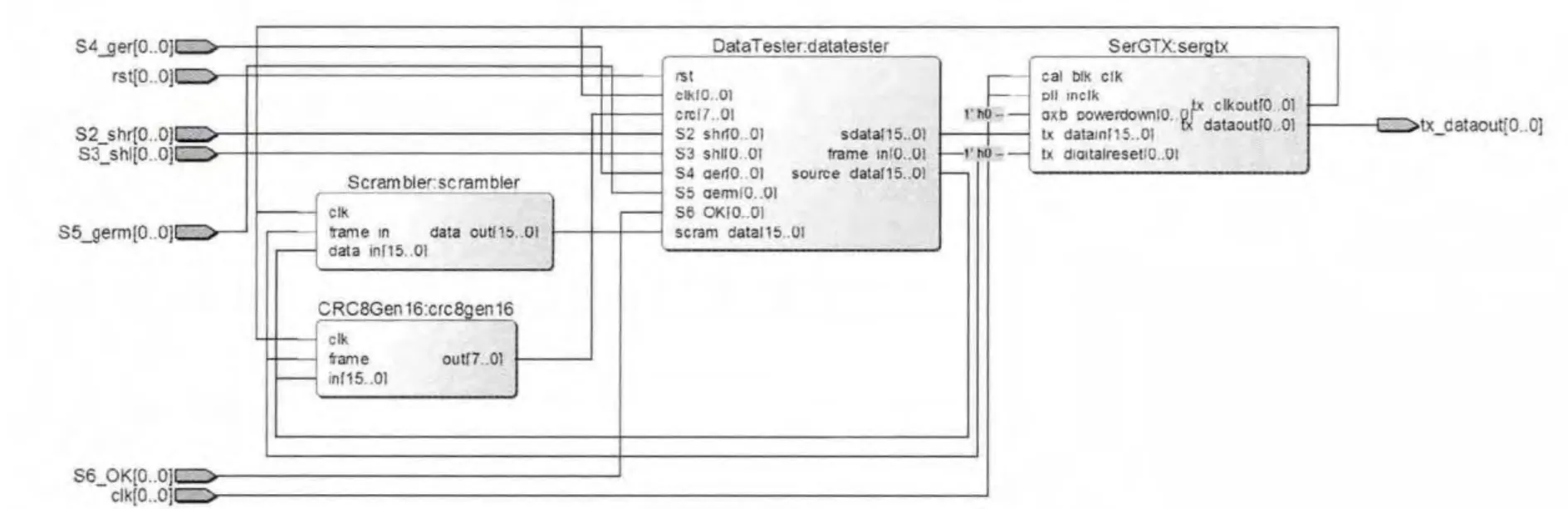

图1给出了LOCic FPGA 系统总图。LOCic FPGA 整体系统由ADC 数据产生器、数据帧生成和数据差错注入器、高速串行器组成数据编码端,通过高速光纤进入数据解码端,由高速解串行器、解帧器和差错检测器等组成。本文专门针对数据差错注入器部分的设计与实现及测试过程进行介绍。全文将从LOCic数据帧格式、模拟数据生成原理与设计,FPGA在板测试、SignalTapII测试结果分析等几方面展开。图2给出带差错注入器的数据编码端在FPGA中实现的RTL。

图1 LOCic FPGA 系统总图

图2 FPGA 数据编码端RTL

2 差错注入器的总体设计

图3给出了差错注入器功能总图。差错注入器包括原始数据流产生器、数据流n位差错产生器、1~15位数据左移滑动1位产生器、1~15位数据右移滑动1位产生器、数据左移滑动16位产生器、数据右移滑动16位产生器和差错控制按键组成。

图3 差错注入器功能

3 Statix II GX 开发板Stratix II GX

开发板采用Stratix II GX EP2SGX90EF1152C3FPGA,LE有90960个,16个传输器通道,传输速率可高达6.375Gbps,PLLs 8个,用户IO口650个,板上25MHz和156.25MHz时钟上,6个用户定义的S1-S6按键式开关等功能[11]。

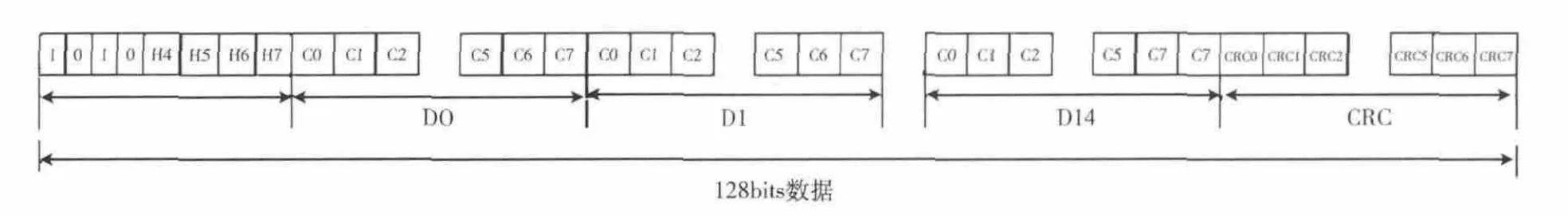

4 数据帧格式

LOCic数据帧格式如图4 所示。其中帧头由固定的1010定界并后跟H4-H7相关伪随机码进行同步,然后是八路14位AD 数据,最后是8位CRC帧尾。因而一帧由8位帧头、112位数据和8位CRC帧尾的128位组成。

5 差错注入器

5.1 模拟数据的生成

为便于在ALTERA的SignalTap II中分析数据流,采用了4位二进制数从0b0000~0b1111组成的64位数据序列从中每次取112位做为数据循环产生,这112位加上8位header和8位CRC值构成一个数据帧每一个时钟产生16bits。

采用如上的模拟数据是基于以下三点:

(1)在进行数据解码端设计、调试和测试时需要对二进制位流进行分析,需要有一定的数据规律便于状态机的设计与实现。

(2)当没有采用scrambler时,以高达5Gpbs的速率在GTX 中传输如果出现过多的连续的1或0,高速串行传输不能工作。

(3)每7个字中插入帧头和CRC 组成的帧使得帧中的数据有一定长度并有周期变化也有利于帧界区分进行调试。

5.2 模拟差错的设计原理

(1)产生1-128bit差错

直接根据按键设置值对源帧数据流的数据相应位取反实现。

(2)1~15位数据左、右移滑动1位产生器

图4 LOCic的数据帧格式

从一个时钟16位位宽数据构造成一个时钟为32位位宽的数据。实现在一个时钟内1~15位中任意位的1位滑动。构造32位数据是因为在产生数据左或右移时需要预测前1~15位数据。

(3)通过对时钟上的数据延时实现数据的16 位右移滑动。

(4)通过对产生数据流的提前操作和控制实现数据流16位左移滑动。

5.3 模拟差错的具体设计

(1)拼接32位位宽数据

data32[31:00]<={data[15:0],data32[31:16]};(2)1-128bit差错产生

通过S3,S4按钮设置StartCnt寄存器值和PosCnt寄存器值产生需在数据流中产生差错的起始位和结束位置,并通过S6 按钮触发操作。在代码实现上通过2 个嵌套的case语句来实现。

(3)1位左或右移滑动

通过S2和S3按钮来分别产生左、右移触发,每按一次数据流就发生一次1位移位。并使用ShiftCnt寄存器记录移位值。相应操作采用case语句针对ShiftCnt的值来确定从data32中那一位的数据开始取16位做为数据输出。

(4)数据16位右移滑动

时钟上的数据延时在实现上实际就是在ShiftCnt值出现从0xf到0x0变化时,保持上一操作不变即相当于在2个时钟上执行了一次操作,来实现数据16右移滑动。如表1所示当在数据D1发生16位右移滑动时,在第1,2这2个时钟均出现D1,这样在相同时钟时刻数据流中的数据相对原数据右移16位。

表1 数据16位右移滑动时数据流情况

(5)数据16位左移滑动

为简单起见把连续7个16位数据及帧界 (即8位CRC和后一帧的8位帧头)看成一个整体128位每个16位对应一个时钟。表2 给出了数据16 位左移滑动时的数据流情况。由数据流的变化,需要在组帧时,提前给出下一个域的数据,同时在填加帧界时刻也需要提前。在FPGA 实现上通过组帧计数寄存器和控制域寄存器的变化来实现16位超前前移。

表2 数据16位左移滑动时的数据流情况

6 测试结果

6.1 软硬件环境

硬件:Stratix II GX 开 发 板。软 件:Quartus II 12.1 64位。

6.2 相关参数说明

未按键注入差错时的LOCic FPGA 系统的SignalTapII波形如图5 所示。未移位之前因电路时序原因原始数据source-data与差错注入后将送入GTX 进行串行化处理的数据流sdata相差5个时钟。

SignalTapII:波形图中寄存器说明如下:

Source_data:按数据帧格式生成的原始数据流

Sdata:差错注入后将送入GTX 进行串行化处理的数据流

图5 未按键注入差错时的LOCic FPGA 系统的SignalTapII波形

StartCnt:由S4按键设置的产生差错的起始位置位。

PosCnt:由S5按键设置的产生差错的结束位置位。

ShiftCnt:左移或右移滑动操作后显示的数据移位变化值。

Shift_counter:接收端移位控制寄存器。

Synch_status:接收端系统工作状态 (数值2 表示数据同步)。

Dataout:解码并恢复后的数据流。

6.3 数据1位左移滑动测试

左移滑动前的数据情况如图6 (a)、 (b)所示。图6(b)中,1153 时钟source_data 为1100010010000000,5个时钟后的1158时钟的sdata也为1100010010000,其它相应位的source_data与sdata相一致,此时ShiftCnt为2h。当发生数据1位左移滑动后的SignalTapII波形如图6 (c)、(d) 所 示。 在 1153 时 钟 时 刻 source _data 为1101010110010001,5个时钟后的1158 时钟位的sdata为110101011001000,ShiftCnt为1h,sdata数据流从原来的相对source_data滞后2bit,变为滞后1bit,即相对原sdata数据流左移滑动了1bit。

图6 数据1位左移滑动测试

6.4 数据1位右移滑动测试

右移滑动前的数据情况如图5所示。1bit右移滑动后的SignalTapII波形如图7所示。

图7 (b)中1153 时 钟 时 的 数 据source_data 是1001111010100000,后5个时钟的sdata即1158 时钟时的数据为1100111101010000,其第一位来自1157时钟中的数据最后一位,自身的最后位进入到1159时钟的数据中的第1位。可以相应比较source_data和sdata数据流,可看到sdata相对应的source_data在串行时间上迟滞了1位。

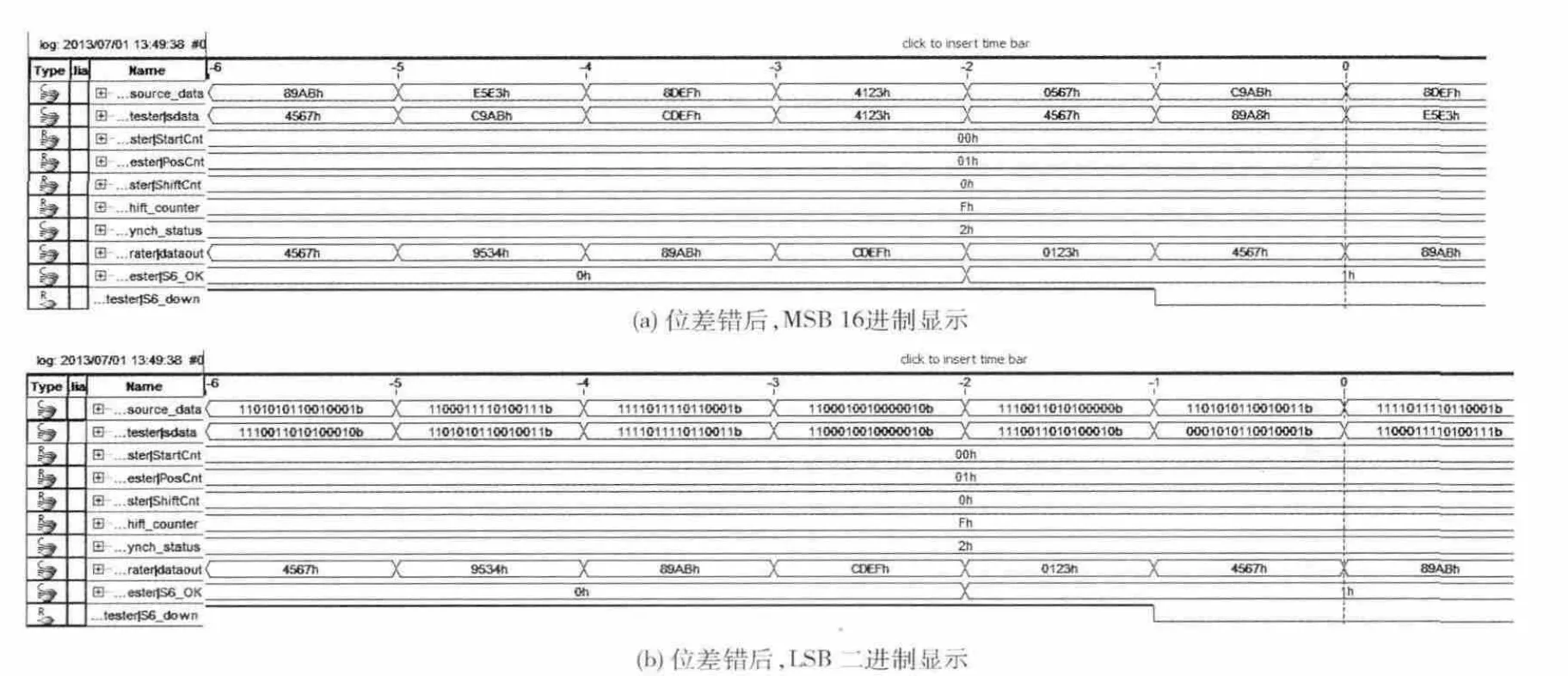

6.5 位差错测试

采用按键S6触发捕获方式来观察。图8 (a)中source_data在-6时钟时的数据是89AB,触发0-1位两位错(StartCnt=0,PosCnt=1)时,在5个时钟后的sdata的数据为89A8,在图8 (b)中对应S6_down下降沿到达的第一个时钟 (-1时钟)时的对应的sdataLSB 的2进制显示的确0-1位发生了变化。

6.6 5G 眼图

图9中给出了在FPGA LOCic中加入差错注入器后在20GHz带宽的DSA72004数字示波器上通过高速串行器高速串行输出的5G 眼图。

7 结 论

通过基于Stratix II GX FPGA 实现了模拟因电子辐射引起的差错的状况,采用SignalTapII验证了差错注入器设计的正确性,并为后端同步系统设计提供了支持,为整个的LOCic系统及解码的开发打下了基础。

图7 数据1位右移滑动测试

图8 位差错测试

图9 系统运行时的高速串行输出的眼图

8 结束语

基于FPGA 的高速数据流差错注入器的设计,通过针对高辐射环境下引起的高速传输中数据发送端位差错和位滑现象的FPGA 实现,为LHC的ATLAS的液氩量能器的前端数据读出系统的数据恢复和解码设计提供了设计、测试与调试基础。通过基于硬件的SignalTapII进行验证差错注入器设计充分证明了差错注入器电路设计的正确和可行性。目前其LOCic有关ASIC 部分即将流片,其接收解码端也初步完成[12]。由于在差错注入器部分设计重点放在差错的注入方面,在FPGA 资源利用率、代码结构及优化方面还需进一步改进。

[1]YANG Zhengjia,LIU Yingjie.Design and implementation of high-speed signal acquisition and storage and optical fiber transmission system [J].Application of Electronic Technique 2012(9):8-11 (in Chinese).[杨振家,刘颖杰.高速信号采集存储及传输系统的设计与实现 [J].电子技术应用,2012 (9):8-11.]

[2]ZHOU Nan,WANG Zhigang.Design of fibre optic high-speed transmit-receive module of data acquisition card [J].Optical Communication Technology,2011 (12):28-31 (in Chinese).[周楠,王志刚.数据采集卡光纤高速收发模块的设计 [J].光通信技术2011 (12):28-31.]

[3]Liang Futian,Chen Jinghong,Deng Binwei,et al.A 65-nm-CMOS-process-based 10-Gbps VCSEL driver [C]//Topical Workshop on Electronics for Particle Physics Perugia,2013.

[4]Moreira P,Christansen J,Wyllie K.The GBTX Link interface ASIC V1.7draft [EB/OL]. [2011-10-26].http://cern.ch/proj-gbt.

[5]Chen Hucheng.Readout electronics for the ATLAS LAR calorimeter at HL-LHC [C]//Technology and Instrumentation in Particle Physics,2011.

[6]Ye Jingbo.A serializer ASIC at 5Gbps for detector front-end electronics readout[J].Journal of Physics:Conference Series,2011,293 (1):1-6.

[7]Gong D.A 16:1serializer ASIC for data transmission at 5Gbps[C]//Presented at the Topical Workshop on Electronics for Particle Physics,2010:20-24.

[8]Liu Tiankuan,Gong Datao,He Mengxun,et al.A low-latency,low-overhead,quick resynchronization line code for the optical data links of the ATLAS liquid argon calorimeter upgrade [C]//Topical Workshop on Electronics for Particle Physics Oxford,2012.

[9]YING Fangqin.Research of real-time monitoring method of internal signal in FPGA [J].China Modern Educational Equipment,2011 (1):70-71 (in Chinese).[应芳琴.基于FPGA的内部信号实时监测方法研究 [J].中国现代教育装备2011(1):70-71.]

[10]GUO Baofeng,HAN Zhuangzhi.Research of system debugging technology based on embedded logic analyzer SignalTapII[J].Microcomputer Applications,2011 (10):53-47 (in Chinese).[郭宝锋,韩壮志.基于嵌入式逻辑分析仪Signal-TapII的系统调试技术研究 [J].微计算机应用,2011 (10):53-57.]

[11]Cao T,Chang J.Design and verification of a bit error rate tester in Altera FPGA for optical link developments [J].Journal of Instrumentation,2010,5:1-5.

[12]Li Xiaoting,Chen Jinghong,Deng Binwei,et al.Optical data transmission ASIC for the ATLAS liquid argon calorimeter upgrade[C]//Topical Workshop on Electronics for Particle Physics Perugia,2013.