深亚微米制程中栅氧化层的缺陷改善方案

李占斌

(上海华虹宏力半导体制造有限公司,上海 201203)

深亚微米制程中栅氧化层的缺陷改善方案

李占斌

(上海华虹宏力半导体制造有限公司,上海 201203)

随着近年来半导体技术的快速发展,半导体集成电路发生了翻天覆地的变化。其中半导体制程技术中的栅极氧化层形成技术在器件中的作用也越来越重要。栅极氧化物的厚度也随着线宽的减小而越来越薄,在90纳米的工艺中栅极氧化层的厚度不到20埃。因此随之而来的问题是:由于在形成栅极氧化层的过程中,晶圆从室温进入高温制程炉管或从高温制程炉管载出到室温的过程中的温度的巨大变化导致微小颗粒的生成,从而带来栅极氧化层的致命缺陷,最终导致产品电性不稳定,良率和可靠性降低的问题。我们称这种高温热氧化层缺陷为有源区域栅极氧化层损伤的缺陷。本文解决的就是在实际的90纳米以下制程中逻辑和闪存工艺中碰到的颗粒缺陷问题及其解决方案。

深亚微米制程 栅极氧化层 颗粒缺陷 解决方案

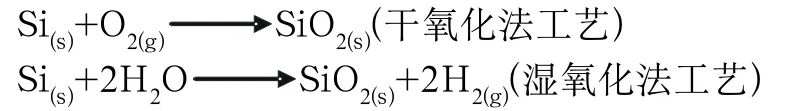

IC行业所用的炉管目前主要是直立式的(水平式的炉子多用在八寸以下的晶圆工厂),按使用压力不同分为常压炉管和低压炉管。常压炉管主要用于热氧化制程、热退火、BPSG热回流、热烘烤、合金等诸方面。低压炉管则主要用于LPCVD沉积工艺,包括多晶硅的形成、氮化硅的形成、HTO和TEOS等;HTO和TEOS都是用来生成二氧化硅的。常用的栅氧化层在常压炉管制程工艺中形成,分为湿氧氧化法和干氧化法两种工艺方法,对深亚微米制程中栅氧化层的形成,还有一种更先进的制程技术,称为快速热氧化制程。在晶圆产品进出炉管时用快速升降温度的方法减少温度剧烈变化对产品的影响,减少颗粒缺陷生成的机会,以达到提高产品稳定性的要求。本文重点研究的是针对常压炉管在深亚微米制程中栅氧化层形成过程中颗粒缺陷形成的机理及相应的缺陷改善方案。

1 常压炉管氧化工艺

硅表面上总是覆盖着一层二氧化硅,即使是刚刚解理的硅,在室温下,只要在空气中暴露就会在表面上形成几个原子层的氧化膜。当我们把硅晶片暴露在高温且含氧的环境里一段时间之后,硅晶片的表面会生长(Grow)一层与硅附着性良好,且具有高度稳定的化学性和电绝缘性的二氧化硅——SiO2。正因为二氧化硅具有这样好的性质,它在硅半导体元件中的应用非常广泛。根据不同的需要,二氧化硅被用于器件(Device)的保护层和钝化层,以及电性能的隔离,绝缘材料和电容器的介质膜等。二氧化硅除了可以用硅晶片加热的方法来制备外,还可以用各种化学气相沉积(Chemical Vapor Deposition)来获得,如LPCVD(Low Pressure CVD)及PECVD(Plasma Enhance CVD)等。选择哪一种方法来制备二氧化硅层,与器件的制程(Process)有相当大的关系。本文主要我们介绍热氧化制程方法(Thermal Oxidation)中栅氧化层(Gate oxide)的形成。

1.1 氧化层的生长

当硅置于含氧气的环境下,氧分子将通过一层边界层(Boundary Layer)到达硅的表面,并与硅原子反应生成SiO2[1]。如图1所示。当原来纯净的硅表面长出SiO2之后,以形成的SiO2层阻止了氧化剂与Si表面的直接接触。氧化剂以扩散方式通过SiO2层到达SiO2—Si界面与硅原子反应,生成新的SiO2层,使SiO2膜不断增厚。SiO2与Si的界面逐渐由Si表面向下推进,每长出d厚度的SiO2,便需耗掉0.44d厚度Si。[2]

图1

1.2 栅极氧化层的形成

氢氧合成氧化:它是指在常压下,将高纯氢气和氧气通入氧化炉内,使之在一定温度下燃烧生成水,水在高温下汽化,然后水汽与硅反应生成SiO2,氢和氧的化学反应方程式为2H2+O2-->2H2O,为了安全起见,通入石英管的氢气和氧气之比必须小于2:1,即氧气处于过量状态,氢氧合成氧化实质上是水汽和氧气同时参与的氧化过程[3]。由于在氧化层生长过程中避免了湿氧氧化时水汽带来的污染,利用氢氧合成氧化制备的氧化层除具有生长速率高、氧化层质量好外,它还具有生长速率容易控制、均匀性和重复性好等特点。这种氧化方法已在现代集成电路工艺中得到广泛应用。以上介绍的热氧化方法均为采用化学反应的高温热氧化,除此之外,在半导体集成电路工艺中,还可以采用化学气相沉积等方法制备氧化层,化学气相沉积的最大优势是低温,采用该方法可以在200~800度范围内生长出各种厚度的氧化层,这种方法制备的氧化层薄膜质量略差,不适合作高质量要求的栅极氧化层。

1.3 SiO2在集成电路制造中的应用

在集成电路工艺中,氧化硅层的主要作用有:

(1)在MOS集成电路中,SiO2层作为MOS器件的绝缘栅介质,这时SiO2层是器件的一个重要组成部分,器件对作为栅极介质的SiO2层的质量要求极高,器件的特性与SiO2层中的电荷以及它与表面硅层的界面特性等都非常敏感。SiO2作为栅介质是SiO2最重要的应用,但当器件进入到深亚微米或亚0.1um之后,栅介质的厚度将小于2nm,这时栅介质则需要新的高介质常数的绝缘介质代替[4],根据目前的发展趋势,氮氧化硅石一种比较好的栅介质材料。(2)利用硼、磷、砷等杂质在SiO2层中的扩散系数远小于在硅中扩散系数的特性,SiO2可以用作选择扩散时的掩蔽层,对于离子注入,SiO2(有时与光刻胶、Si3N4层一起使用)也可以作为注入离子的阻挡层。(3)作为集成电路的隔离介质材料。(4)作为电容器的绝缘介质材料。(5)作为多层金属互联层之间的介质材料。(6)作为对器件和电路进行钝化的钝化层材料。

1.4 栅极氧化层的特性

氧化层的重要特性有很多,以下将针对其中几项重点加以说明。

1.4.1 电性(图2)

图2 电荷在氧化层内的分布[5]

影响热氧化层(Thermal Oxide Layer)电性的电荷来源主要有:

(1)界面陷阱电荷Qit(Interface Trapped Charge)。这种电荷的产生是由于界面处氧化过程引起的未饱和键(Dangling Bond)和Si与SiO2不连续性引起的。适当的退火(Anneal)和选用<100>晶片可降低其浓度。

(2)固定氧化层电荷Qf(Fixed Oxide Charge)。在距离Si-SiO2截面约30A.的SiO2里,通常带正电,是由于SiO2中存在过剩的Si原子引起的。高温退火(Anneal)和加速氧化层的冷却(Cooling)可以降低Qf。选用<100>晶片,Qf较小。

(3)移动性离子电荷Qm(Mobile Ion Charge)。来自氧化层内的存在的碱金属离子(Na+,K+等)。来源于石英材料,化学品以及操作人员污染。掺HCl氧化可有效地减小Qm,但由于HCL有极强地腐蚀性,现在多用反式—二氯乙烷(Trans-LC)等含氯的化合物。

(4)氧化层陷阱电荷Qot(Oxide Trapped Charge)。这类电荷没有特定的分布位置,主要是因为晶片制造过程中其他工艺,如离子注入(Implant),干法刻蚀(Dryer etch),溅射(Sputter)等引起的电子和空穴被氧化层内的杂质或未饱和键所捕捉(Trapped)所造成的。带正电或负电则不一定。利用退火工艺也可降低这类电荷。

1.4.2 应力(Stress)

SiO2与Si的热膨胀系数(Thermal Expansion Coefficient)不同,当晶片在高温下(通常在800℃以上)进行热氧化并恢复到室温状态后,由于Si的热膨胀系数比SiO2的高,SiO2层将承受一股来自Si衬底的压缩应力(Compressive Stress)。如果工艺控制不当,这股压缩应力会使晶片表面发生弯曲(Warpage),并使衬底表面产生缺陷(Defect)。所以氧化工艺中的温度控制与调整必须十分注意,特别是晶片载入与载出炉管(Furnace)时的速度不能太快,以免晶片表面受热不均匀而产生变形或弯曲。应力是常压炉管产生颗粒缺陷的主要原因之一。

1.4.3 氧化层针孔(Pin Hole)

氧化层的应用越来越朝缩小的方向发展,特别是深亚微米(Deep Sub-micrometer)的工艺,栅氧化层(Gate Oxide)发展到只有40或更薄的厚度。由于氧化过程中的微尘(Particle)、杂质或氧化缺陷,都让氧化层留下一些针孔。这些氧化层的针孔是栅氧化层漏电流(Leakage)的根源。

减小这类的针孔密度,只有让氧化炉管内的微尘及杂质降低,并且在氧化前将晶片加以清洗,保持晶片表面的洁净。

1.4.4 氧化层密度

SiO2的密度可由折射率(Refractive Index)来反映。典型值是1.46。热氧化温度升高,长出的SiO2的折射率会随着下降,但下降值很小。通常这种SiO2密度特性,可以通过HF +H2O溶液刻蚀的速率来检验。当生成SiO2的工艺不同,SiO2的密度会随之改变,刻蚀速率也跟着改变。由此我们可以知道SiO2的化学组成是否有变化。这不但表示其电性以及机械性质也受到影响之外,也会对接下来的氧化层刻蚀的刻蚀终点造成误差。所以,热氧化层的刻蚀速度应定期的接受检查。SiO2有极高的化学稳定性,不溶于水,只能和HF作用。

2 常压炉管常见的缺陷类型

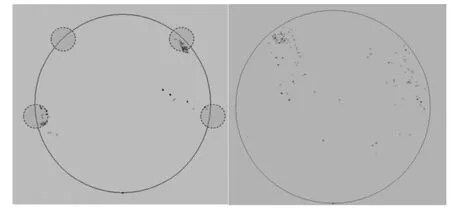

(1)前制程清洗设备处理的缺陷,晶圆表面没有处理干净或晶圆片被前清洗设备有particle造成的,典型的颗粒图形如(图3)。

图3

(2)晶圆经前制程清洗设备处理后,在晶圆边缘出现特殊颗粒的图Water mark,主要有清洗设备的干燥槽没有处理完全造成的,接触点位置有水痕残留,出现典型的颗粒图形如(图4)。

图4

(3)晶圆片本身质量问题带来的缺陷,也可称为原生缺陷,通常称为COP(Crystal Originated Particles)。这种缺陷最初是由于观测工具的落后,无法识别缺陷的凹凸,被命名为一种颗粒,.这种类型的缺陷对产品品质的影响较小,不会对制品的良率产生大的影响。出现典型的颗粒图形位于晶圆的中心位置如(图5)。

图5

(4)氧化炉管本身晶舟与晶圆接触并在生产过程中出现的缺陷,颗粒图形如(图6),这种类型的颗粒形成主要是由于晶圆在进出高温炉管过程中,高低温变化与晶圆与晶舟的接触变形有关。此种缺陷是造成栅极氧化层不稳定性,良率低的主要原因之一,也是本文重点研究的内容。比较典型的颗粒图形如(图6),常见的S E M(Scanning Electron Microscope)照片如(图7)。

图6

图7

3 栅氧化层中颗粒缺陷的形成机理及改善方法

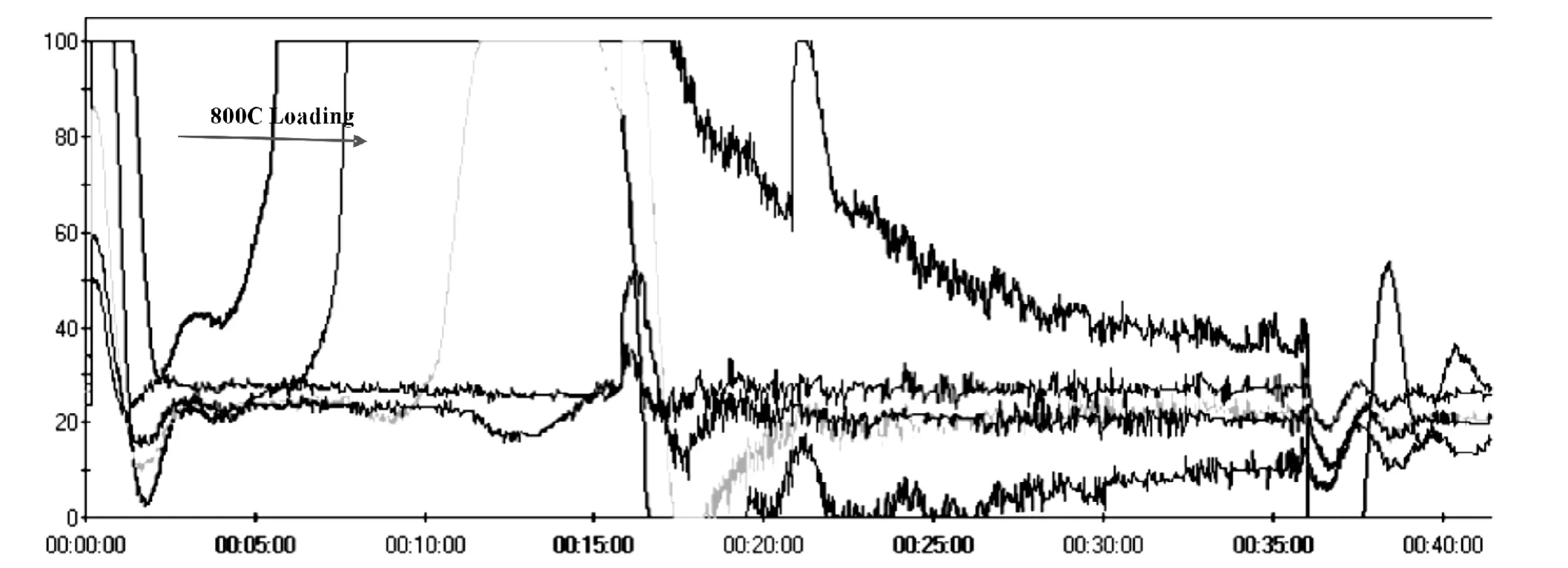

石英晶棒位置缺陷常出现在晶舟进出反应腔体的高低温交界处,由于出现较大的温差变化导致晶圆变形。如(图8)与(图9)所示为晶舟800℃进入炉管时加热器的功率变化曲线,可见加热器的功率因晶圆在晶舟上由室温进入高温800℃的炉管时温度的剧烈变化导致功率由正常的30%迅速增长到满载的变化,这种变化导致晶圆的细微变形,造成了晶圆内部缺陷的生成。如(图10)为晶圆在晶舟上因温度的巨大变化导致缺陷形成机理的示意图。

图8

图9

图10 颗粒缺陷应用解决方案分析

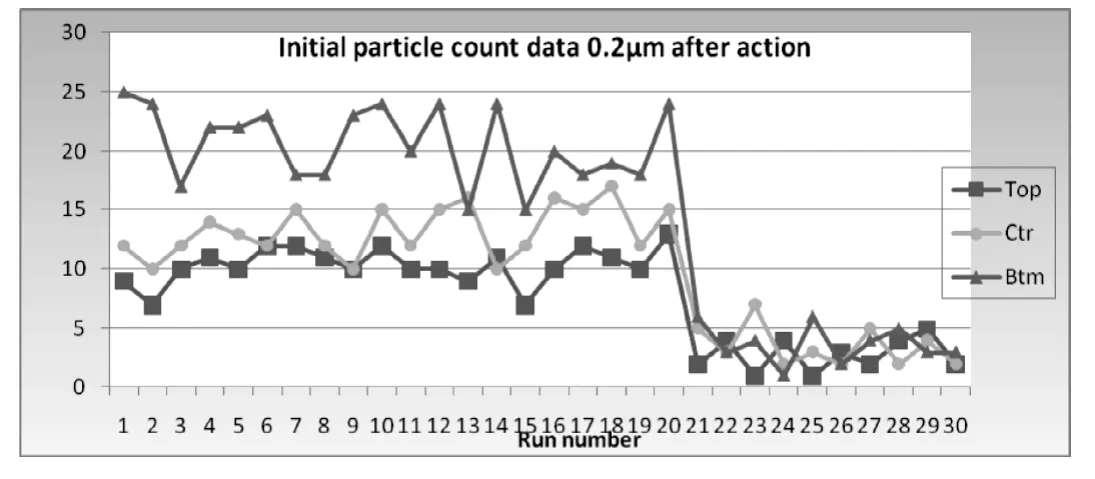

(1)降低晶舟进出反应腔体的温度,经过试验证明,较低的晶舟载入速度降低了晶圆出现轻微变形的缺陷,同时减少了由于加热膨胀导致的应力变形风险。当然载入温度不是越低越好,更低的载入温度进入到反应腔体后需要更长的时间加热到栅氧化反应需要的温度更长,也会带来负面影响,会影响制品的稳定性,增加了制品在整个制程中的时间。实验证明,600℃~700℃的制程载入温度对改善颗粒缺陷有明显作用,同时最终产品的良率与稳定性达到更高的质量要求。

(2)改变晶圆片与晶舟的接触方式,减少晶圆片与晶舟之间可能产生的震动。例如由传统的四轴晶棒改为三轴晶棒,或者改为面式接触的半圈型接触石英晶舟,通过减少制品的接触震动来改善颗粒缺陷。

(3)上述两种改善缺陷的方法可以应用到一起,改善的效果会更加明显,如(图11)所示为降低到700℃载入温度与改变石英晶棒数量后的颗粒改善图标。

图11

4 栅氧化层缺陷解决方法展望

炉管虽然存在升降温速度比较慢的问题,但因为它属于批处理工艺,一次可处理一百片或一百五十片。因此,在未来IC行业中仍将占有不可替代的作用。其发展方向为提高升降温速度,提高热均匀性,减少制程反应时间,提高设备利用率等诸方面。目前在应用的0.13深亚微米以下制程中用到了超薄栅氧化层快速热处理工艺。从升降温的方法较大地改善了制程处理的时间。

[1]B.E.Deal and A.S.Grove,Journal of Applied Physics, Vol.36,1965.

[2]Silicon processing for the VLSI era volume 1,process technology,STANLEY WOLF Ph.D.

[3]张兴,黄如,刘晓彦.微电子学概论.北京大学出版社,2000.

[4]王阳元,关旭东,马俊如.集成电路工艺.高等教育出版社,1991.

[5]Silicon processing for the VLSI era volume 3,the submicron MOSFET,STANLEY WOLF Ph.D.