陶瓷封装电路恒定加速度试验失效仿真分析

杨轶博,丁荣峥,孙少鹏,张顺亮

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 概述

恒定加速度试验是考核高可靠集成电路结构强度的重要手段,该项试验可暴露冲击和振动试验不一定能检测出的机械结构类型缺陷[1]。其通常用来考察陶瓷封装封盖、键合引线系统、芯片粘接及外壳结构强度等。

恒加试验失效通常由三类因素所导致:

(1)结构强度、工艺设计不合理;(2)封装工艺缺陷;(3)试验不当引起的问题。

采用AutoCAD二维绘图软件结合工程经验设计陶瓷封装在国内还较普遍,但随着集成电路多功能、高集成、高性能方向的快速发展,封装结构复杂程度提高(如双腔、多腔、堆叠封装等)。设计导致结构强度不足的问题往往在考核试验后才能被发现[2]。

封装设计必须引入模拟仿真手段,这不仅在国际和国内高端封装企业取得了成功,更是机械、电力、航空、航天、船舶等高端制造业普遍采用的设计手段。结合工程实际的模拟仿真可充分论证封装设计方案,消除早期设计存在的各种缺陷;亦可对部分工序进行模拟,优化工艺参数,降低工艺样品设计-试验-验证分析的成本并缩短研发周期;还可结合机械结构试验和结构失效情况,对封装电路进行失效分析,找出失效原因及失效机理。

本文针对陶瓷封装电路CQFP256在20 000 g恒加试验中出现的瓷体开裂情况,利用Ansys Workbench平台软件,模拟电路恒加试验条件,并结合电路失效情况进行仿真结果分析,找出瓷体开裂的原因并优化改进,解决了该款电路结构失效问题。

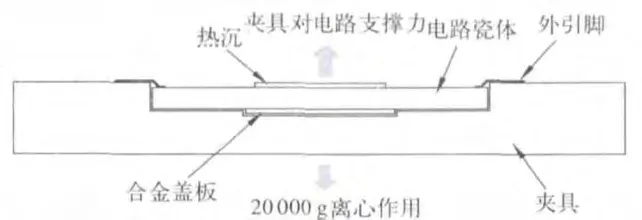

2 恒定加速度试验及电路失效情况

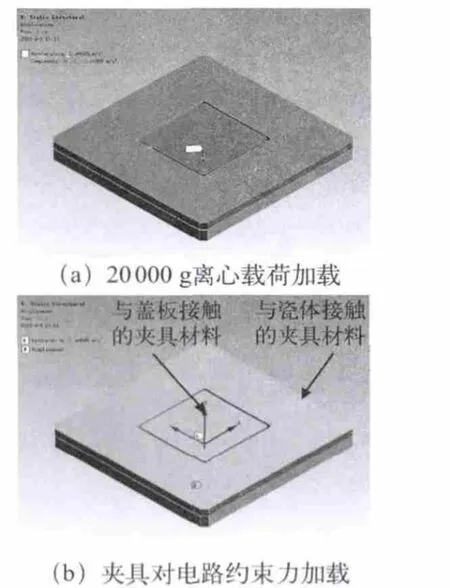

试验选5只CQFP256封装电路,按GJB548B方法2001.1条件D(20 000 g)进行试验。夹具材料为聚四氟乙烯,夹具设计留出两个凹槽,使陶封电路装入夹具后,瓷体和盖板受到夹具约束。在恒加试验过程中,夹具为电路提供支撑力,以抵消20 000 g离心作用。电路与夹具装配情况如图1所示。

图1 电路与夹具装配及恒加试验受力情况

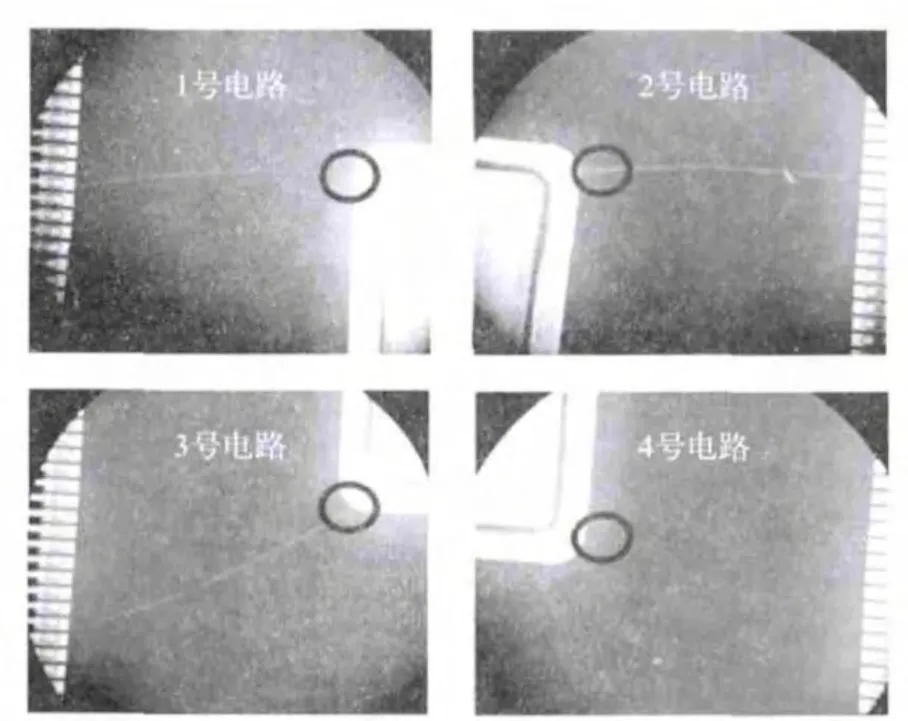

试验后,5只电路均出现瓷体开裂,裂纹位于热沉四个顶角中的某一角处的陶瓷上,贯通整个瓷体。带热沉的瓷体面裂纹周围有白色粉末;带盖板的瓷体面裂纹周围无白色粉末,详见图2。

图2 4只CQFP256瓷体开裂照片(圈出部分为裂纹源)

显然,裂纹产生是由于20 000 g恒加动载荷在陶瓷材料内部产生过大的应力,超出了陶瓷材料抗拉强度或抗弯强度。

3 恒加试验模拟及仿真分析

采用Ansys Workbench平台软件进行模拟仿真。利用“Geometry”模块建立CQFP256的三维简化模型,利用“Static Structural”模块模拟试验条件进行材料加载、网格划分和求解计算。

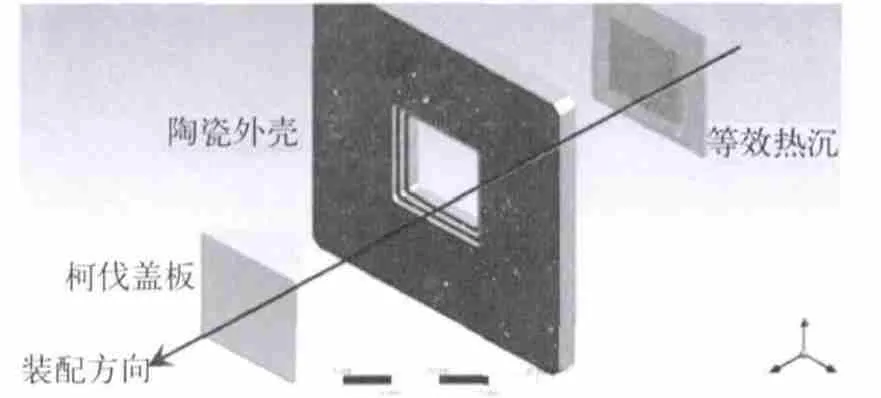

3.1 封装电路结构

电路采用CQFP256封装形式,芯片与热沉互连采用高温导电胶粘接形式,并用引线键合方式与陶瓷完成互连,热沉嵌入陶瓷外壳中,盖板用金锡合金熔封于陶瓷外壳上。电路整体采用气密性封装形式。封装装配结构如图3所示。

图3 CQFP256封装装配结构示意图

3.2 理想试验条件仿真及分析

3.2.1 电路仿真建模

为了后续仿真过程减小网格划分和仿真计算量,对电路进行简化,简化依据和结果如下:

(1)Φ30 μm键合丝和0.15 mm/0.22 mm外引脚(本身已受到夹具支撑)相对于盖板、热沉和瓷体的质量,可忽略不计,故对瓷体开裂几乎无贡献作用,省略不建模;

(2)芯片与外壳是紧密结合的整体,试验中也未分离,将芯片和导热胶的质量合并至热沉上,而不独立建模。

CQFP256恒加试验简化的电路模型如图4所示。模型中包含柯伐盖板、陶瓷外壳和加入芯片和导电胶质量的等效热沉。

图4 CQFP256电路简化模型

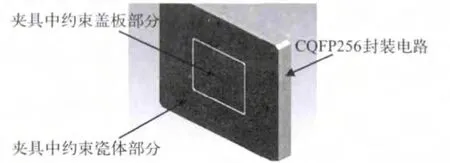

3.2.2 电路与夹具装配建模

理想试验条件下,电路放入夹具后,瓷体、盖板分别与夹具完全贴合。尽管在试验过程中,陶瓷外壳与聚四氟乙烯夹具由于材料弹性模量不同,产生变形量有差异,导致部分紧贴部分分离,但仿真软件的求解器会根据所设置条件在计算过程中体现出这一物理过程,因此不必人为干预。

瓷体尺寸略小于夹具内腔尺寸,因此在平面方向上无约束(电路可在腔体中晃动),夹具仅为电路提供反向支持力。为减小网格划分和仿真的计算量,对夹具进行简化,仅保留与瓷体和盖板接触的部分,电路-夹具装配简化模型如图5所示。

图5 电路-夹具装配简化模型

3.2.3 仿真设置

建立仿真分析流程[3],再将建立的模型数据导入仿真模块“Static Structural”。建模和仿真流程如图6所示。

图6 电路恒加仿真流程

(1)材料参数赋值

赋予各组件材料参数。各组件材料参数如表1。

表1 各组件材料参数

(2)网格划分

对所有组件进行网格划分,采用四面体网格划分方式,对失效区域附近进行网格加密,以增加计算结果精度。图7为隐去夹具只显示电路的网格划分结果。

(3)离心载荷和支撑约束加载

20000g离心载荷及夹具对电路的支撑约束力加载后的情况如图8所示。

(4)仿真结果分析

完成以上设置后,Ansys Workbench自动进行计算,并给出结果。

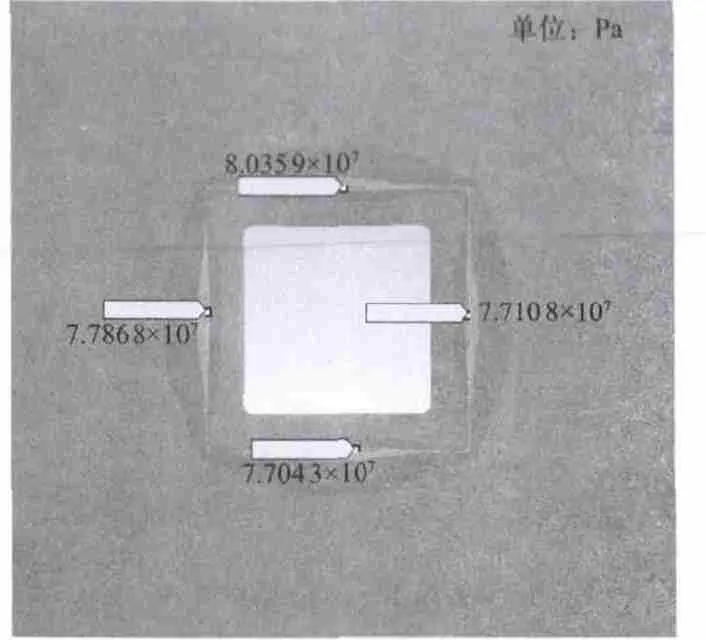

陶瓷为脆性材料,因此需用最大主应力理论作失效判据[4]。只查看陶瓷区域的最大主应力,其最大值出现在热沉一面的陶瓷区域,约为80 MPa(如图9)。

图7 网格划分结果

图8 离心载荷和支撑约束力加载

图9 理想试验条件下陶瓷上最大主应力分布(带热沉一面)

CQFP256陶瓷材料抗拉强度约为150 MPa,抗弯强度约350 MPa[5],远大于80 MPa的计算结果。对比图1与图9,可以看出最大主应力出现的位置与失效开裂位置不符。因此认为,在理想试验条件下,即夹具与电路完全贴合接触的情况下,瓷体不会开裂失效。

仿真结果与实际电路失效情况完全不符,因此我们须考察非理想试验条件下的应力分布情况。

3.3 非理想试验条件下仿真及分析

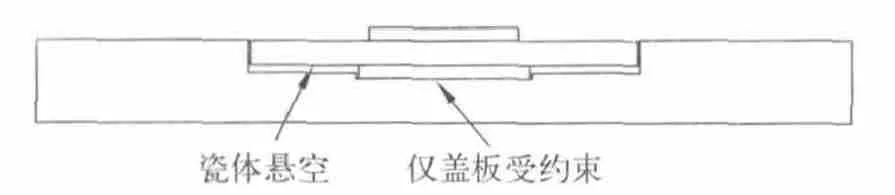

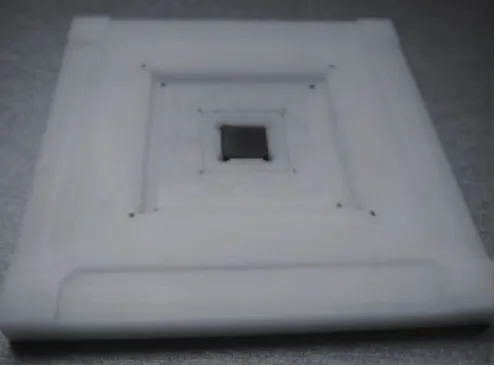

实际夹具与外壳接触部分目测有内腔铣刀痕迹,边角处也未完全铣掉。

用激光测量显微镜测量其平整度等尺寸,发现留给盖板的夹具腔体较浅,与盖板接触的夹具部分(图11中黑色区域)将盖板顶起,导致瓷体悬空,如图10所示。恒加试验夹具实物如图11所示。

图10 实际电路-夹具装配示意图

图11 实际夹具照片

在理想试验条件的模型基础上进行修改,删除与瓷体贴合的夹具部分,即删去图5中夹具约束瓷体的部分。其余不变。

仿真流程与3.2节中内容相同。采用相同的仿真流程,完成材料参数赋值、网格划分、离心载荷和支撑约束力加载,进行仿真计算。

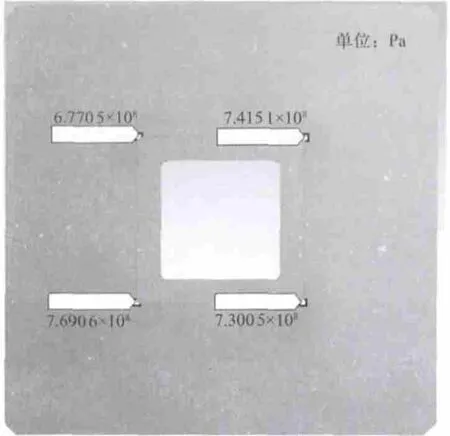

计算完毕,查看瓷体最大主应力情况,发现其最大值位于热沉四角附近的陶瓷上,与实际瓷体开裂情况一致。此外,最大主应力值约为770 MPa,远大于陶瓷的抗拉强度(150 MPa)和抗弯强度(350 MPa)。这表明,在盖板受约束而瓷体悬空的非理想情况下(实际试验情况),陶瓷必然发生开裂,如图12所示。

4 夹具改进及试验验证情况

根据仿真结果暴露的问题,针对性地对试验条件进行改进。在夹具表面预先铺一层塑性物质,而后将电路放入夹具中。恒加试验过程中,瓷体悬空部分和夹具腔体之间的空隙被塑性材料填满,整个电路几乎完全受到支撑力作用,接近3.2节所述的理想试验条件。改进后,4只CQFP256封装电路重新进行了20 000 g恒加试验,全部通过考核验证,未出现任何机械结构失效问题。

图12 非理想试验条件下瓷体最大主应力分布(带热沉一面)

5 结论

利用Ansys Workbench专业结构设计仿真软件,对陶瓷封装电路恒定加速度试验中结构失效进行了模拟和仿真分析,准确分析出热沉四角附近瓷体开裂的原因,从理论上详细阐明了结构失效的机理。并根据仿真分析结果,提出了问题解决的措施,节约了成本,缩短了产品改进周期。陶封电路恒加试验失效分析、仿真分析与设计优化,可对电路封装结构失效分析产生普遍的理论指导意义。

[1] 微电子器件试验方法和程序[M]. 2005.

[2] 刘勇,梁利华. 微电子器件及封装的建模与仿真[M]. 北京:科学出版社,2010.

[3] 姜涛. Ansys Workbench培训手册[Z]. 2011.

[4] S P Timoshenko. 弹性理论[M]. 北京:清华大学出版社,2007.

[5] IWASAKI, AICHI. NTK HTCC Package General Design Guide [Z]. 2008.