QPSK调制解调系统设计及FPGA实现

(杭州电子科技大学通信工程学院,浙江 杭州310018)

0 引 言

四相相移键控(Quadrature Phase Shift Keying,QPSK)数字调制技术,因其具有频谱利用率高、频谱特性好、抗干扰性能强、综合性价比高等突出优点而成为目前卫星、微波和有线电视上行通信中最常用的一种调制方式[1]。现场可编程门阵列(Field Programmable Gate Array,FPGA)具有功能强大,可反复编程修改,开发工具智能化等特点,用FPGA实现调制解调电路,能大大缩短系统电路的体积,提高电路稳定性,且比专用芯片具有更大的灵活性和可控性[2]。本文基于FPGA 硬件描述Verilog 语言,设计了一种QPSK调制解调系统实现方案。经FPGA 硬件测试,该方案具有较好的可行性。

1 QPSK调制系统分析与设计

为便于基带信号发送传输,需将信号从基带信号频谱搬移到一个更高的频段上。QPSK 信号的载波具有4种可能的离散相位状态,串行输入信号经过QPSK系统调制后得到的调制信号可表示为:

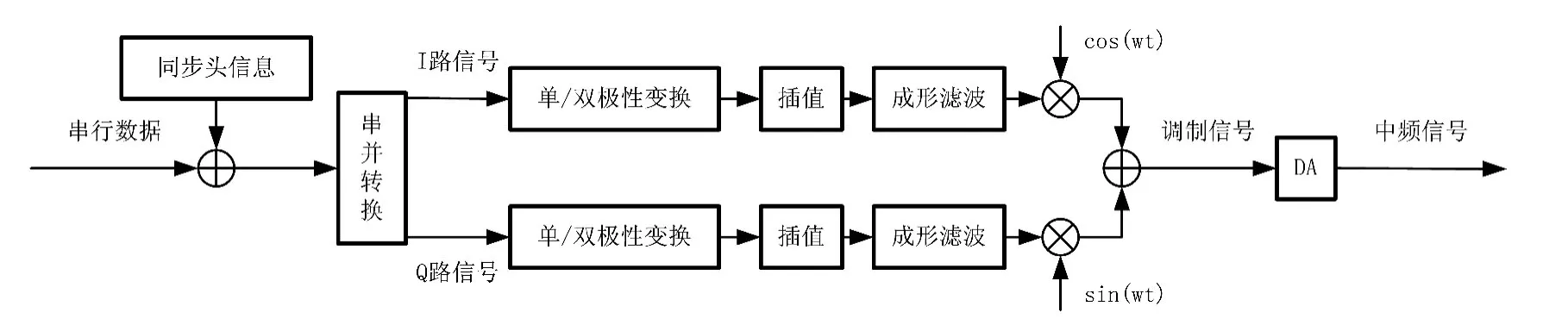

式中,I(t)= ±1和Q(t)= ±1代表经过串并转换后得到的两路正交信号,ωc为载波频率。本文完整的QPSK调制系统设计框图如图1所示。

图1 QPSK调制系统框图

在信号调制前,对每一帧有效输入信号预加一段定长的同步头信息。增加同步头信息的目的一方面是辅助解调端解决相位模糊问题,另一方面也是解调端判定有效解调输出帧同步的重要标志。而后将接收信号串并转换及符号映射得到I、Q 两路正交双极性信号。

为降低成形滤波器处理基带信号而造成码间串扰的影响,可对双极性信号在一个周期内进行插值补零。假设输入序列为x(n),输出序列为yL(n),对x(n)插值后信号的时域与频域关系如式(2)、(3)所示。根据式(3),插值后基带信号频谱的周期变为原来的1/L,也即频率扩大了L倍。从而使距离很近的基带信号频谱拉开,增大了频谱的过渡带,有利于提高成形滤波器的滤波效果。

基带信号的频谱范围比较宽,因此需要在发送端将信号通过成形滤波器进行限带处理。本设计采用满足奈奎斯特第一准则的均方根升余弦滚降滤波器,其频域响应如下:

式中,T为输入脉冲信号周期,α为滚降系数。借助Matlab的FDATOOL 工具,由FIR 窗函数求得均方根升余弦滚降滤波器系数,并调用ISE 软件自带的FIR 知识产权(IP)核来生成所需的数字成形滤波器。类似,由DDS 知识产权(IP)核来生成所需频率的载波信号,将正交载波分别与经过成形滤波器处理后的信号相乘叠加得到最终的调制输出信号,并由专用DA 数模转换处理模块将数字信号转换为模拟信号发送到传输信道。

2 QPSK 解调系统分析与设计

QPSK 解调的目的是将原始基带信号从高频调制信号中分离出来。本文不考虑载波频偏的情况,只对载波相偏进行分析。QPSK 解调系统主要由载波同步,位同步抽样判决和相位模糊纠正3个模块构成。其中载波同步是QPSK 解调系统的核心部分,载波同步设计的好坏直接关系到基带信号能否正确解调。本文采用基于Costas 环[3-5]的QPSK 载波同步跟踪算法进行设计。QPSK 解调系统的实现框图如图2所示。

图2 QPSK调制系统框图

2.1 载波同步模块设计

简要分析由Costas 环实现载波同步的过程。设解调端经AD 处理后得到的信号为:

式中,ωc为输入信号载波频率,ψ为输入信号载波相位。NCO 产生的本地跟踪载波信号分别为cos(ωct+φ)和sin(ωct+φ),其中φ为本地载波相位。经过乘法器和匹配滤波器模块处理后得到的两路基带信号可表示为:

将SI,SQ两路信号经过鉴相模块处理后得到的差值控制信号为:

由式(8)可知,影响鉴相器输出的只有输入信号的载波相位和本地恢复载波的跟踪相位。同时可见在0 2范围内存在4个相位跟踪稳定点。环路滤波器对鉴相输出信号进一步处理并输入到NCO模块,促使NCO 对本地载波进行不断调整,直到实现载波同步。

载波同步系统由图2虚线框中的各模块构成。匹配滤波器采用与发送端的成形滤波器具有相同传输特性的均方根升余弦滤波器来滤除带外噪声,并与发送端的成形滤波器构成最佳基带传输系统。根据四相松尾环模型来设计鉴相模块[6-7]。环路滤波器的作用主要是滤除鉴相器输出相差信号中的高频分量,起到平滑滤波的作用,本设计采用2 阶数字环路滤波器[8]。

2.2 位同步抽样判决模块设计

匹配滤波后得到的是连续信号,为了将连续信号转化为基带脉冲信号,需要对其进行位同步抽样判决处理。本设计采用了一个比较简便的方法:首先设定一个峰值门限,当信号处于稳定情况下才会达到此门限,对达到门限的连续信号进行峰值点判决。由于输入的是规则周期信号,因此在每个周期内对峰值点进行数据采集。为了使信号更加可靠,采取峰值点附近多个信号进行累计符号判决,大于符号门限则判定为1,否则判定为0。

2.3 相位模糊纠正模块设计

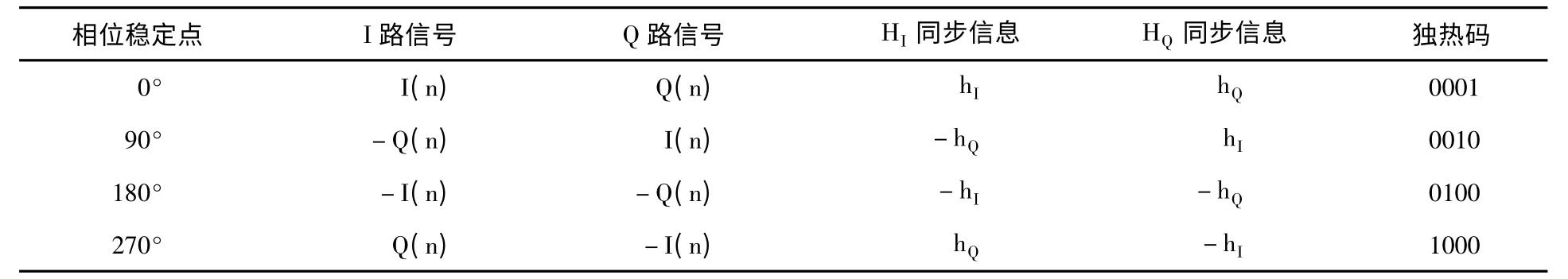

通过Costas 环实现载波同步会存在4个相位稳定点如表1所示,但是只有处于0°稳定点时输出的才是正确信号,其余3个为相位模糊点。由于调制前每一帧基带信号已预加了一组同步头信息,因此预设了一个匹配门限,并对接收信号做4 路并行比特位与判决,用4 bit 独热码对匹配结果进行标记。当其中一组I、Q 路信号分别与HI、HQ同步信息位与后的累计值达到匹配门限时,根据独热码标记对信号做相应处理,同时如果有独热码信号触发就意味着接收端检测到了有效信号,从而有效实现了数据帧同步。

表1 相位模糊对照表

3 QPSK系统仿真与FPGA实现

本设计采用两块KC705-FPGA 开发板进行调制解调系统的板级测试,分别用于信号调制和解调,并通过两块FMC150 外扩功能板实现信号的数模与模数转换以及调制解调测试信号的传输。实验采用帧长为2 048 bit,码率为0.96 MHz的测试信号,辅助同步头信息为64 bit,基带载波频率为1.92 MHz,采样频率为15.36 MHz,由Matlab 产生64 阶滚降系数为0.25的成形/匹配滤波器系数。环路滤波器系数C1、C2计算分别为0.34和0.022 75。

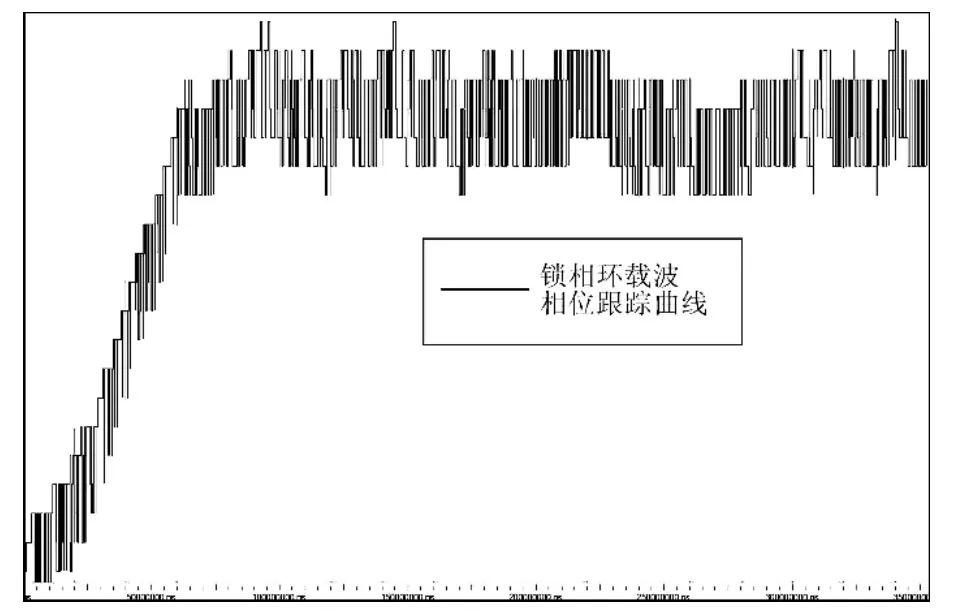

由于QPSK调制系统较为简单在此不再赘述,以下着重分析解调系统仿真及实现效果。-6 dB 信噪比下Matlab 载波同步仿真图如图3所示,由图3可见载波频率在初始阶段振荡明显,经过初始阶段跟踪之后频率逐渐趋于稳定,跟踪曲线在1.92 MHz 实际载波频率范围内小幅振荡,实现了载波同步。Modelsim 载波相位跟踪时序仿真图如图4所示,初始相位设置为0°。结合波形轨迹发现,经过初始阶段跟踪,相位参数在一个较小范围内小幅振荡趋于稳定,与Matlab 理论仿真效果一致。抽样判决仿真图如图5所示,每个波形包络包含16个点,通过包络曲线与判决方波对比可见,经峰值点左右10个符号累计判决,波峰判决为0,波谷判决为1,实现了信号的转换。

图3 Matlab 载波跟踪仿真图

图4 Modelsim 载波跟踪仿真图

图5 Modelsim 抽样判决仿真图

该QPSK系统ChipScope 硬件板级测试时序效果如图6所示。其中flip_angle、head_angle_flag、data_out、douta和right_num 分别代表相位翻转信号、输出标志信号、解调基带信号、原始基带信号及校验计数信号。在head_angle_flag为1时对时序进行触发,从捕捉到的信号可见,flag_angle为0010表明出现了90°相位模糊,触发相位模糊纠正模块工作,从硬件时序中截获的前30 bit 解调基带信号与ROM 中预存的基带校验信号对比发现数据同为(110110011101101001111011111010),则解调信号与原始信号吻合,right_num 信号的规则累计输出也对此结论进行了验证。

图6 ChipScope QPSK调制解调系统时序图

上述软件测试表明:QPSK调制解调系统各模块工作正常,载波同步、位同步抽样判决和相位模糊纠正性能达到预期目标,对随机基带调制信号实现准确还原。最后,经多次上板测试,验证此方案设计合理可靠,符合实际硬件环境,能满足实践应用需求。

4 结束语

本文基于KC705-FPGA 开发板,通过FPGA 硬件编程对QPSK调制解调系统进行了完整系统设计,提出了一种工程可实现的QPSK系统设计方案。通过Matlab和Modelsim系统功能仿真及ChipScope硬件板级时序分析证明此设计方案各模块性能可靠,在本文测试环境下对基带调制信号进行准确地解调还原,具有较好的应用前景。

[1]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,2006:283-290.

[2]田耘,徐文波,张延伟.无线通信FPGA 设计[M].北京:电子工业出版社,2009:358-366.

[3]吴华明,苏雁泳,刘爱军.锁相环与锁频环在数字Costas 环中的应用[J].科学技术与工程,2010,19(10):4 645-4 650.

[4]陈荣,管吉兴,张喜明.数字Costas 环的设计与实现[J].信号与信息处理,2010,40(3):24-26.

[5]许志鹏,崔琛,余剑.基于锁频环与锁相环相结合的载波跟踪技术[J].电讯技术,2012,52(4):558-561.

[6]吴大维.一种QPSK 解调器(松尾环)的研制[J].电讯技术,1990,30(4):22-26.

[7]赵秋明,孙志磊,欧阳宁.QPSK 载波同步算法研究及FPGA实现[J].电视技术,2012,36(11):100-103.

[8]张安安,杜勇,韩方景.全数字Costas 环在FPGA 上的设计与实现[J].电子工程师,2006,32(1):18-20.