高性能DSP软核中DMA控制器的设计与验证

郑 挺,李 勇

(国防科学技术大学 计算机学院,湖南 长沙,410073)

0 引 言

银河飞腾-迈创,简称 “飞腾-迈创”(英文YHFT-Matrix,简称FT-Matrix)是由国防科大计算机学院微电子与微处理器研究所研发的具有自主知识产权的面向无线通信、视频和图像处理的高性能浮点DSP软核。数字信号处理器(DSP)的主要任务是完成大量实时数据计算,它强大计算能力的发挥离不开高效的数据供给,设计一个可高效搬移数据的部件——直接存储器访问控制器 (DMAC),对DSP性能的提升具有重要意义。

本文针对该DSP软核的应用特点,提出了一种灵活高效的DMAC方案。为保证设计的正确性,本文用两种方法对设计进行了验证:传统的模拟验证方法和目前国内外研究热点之一的基于SVA (system verilog assertion)的验证方法。它们的验证能力互补,将它们结合起来验证,可充分发挥各自的优点。

1 IP核体系结构简介

YHFT-Matrix内核是基于超长指令字 (very long instruction word,VLIW)的单核与多核动态切换的体系结构并运用了单指令流多数据流 (single instruction multiple data,SIMD)、单指令流多线程 (single instruction multiple threads,SIMT)技术,其独特的双指令流多线程 (double instruction multiple threads,DIMT)模式支持操作系统和应用算法的同时运行。

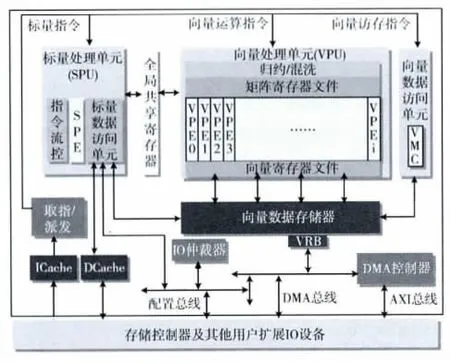

IP核的整体结构如图1所示,该结构主要包括统一的取指、派发部件、标量处理单元、向量处理单元、向量存储及控制部件、指令缓冲器 (Icache)、数据缓冲器(Dcache)及直接存储器访问控制器 (DMAC)。其中,直接存储器访问控制器 (DMAC)是DSP的核心数据传输引擎,它的性能的高低对芯片的整体性能具有重要影响。

图1 FT-Matrix IP核总体结构

图2 DMA控制器的整体结构

2 DMA控制器的设计

为满足以3G/4G无线通信为代表的高密集度计算对数据供给的要求,设计了两个可快速在核内外搬移数据的通用通道和用于与外部通信的4个AXI通道。为满足对DSP仿真调试的需要,设计一个与ET (Emulation/Test)部件连接的通道。为加快数据的搬移速度,设计了多总线、集中式仲裁的结构。

2.1 DMA控制器的整体结构和各通道实现的功能

DMA控制器的结构如图2所示。DMA控制器包括通用通道1、通用通道2、AXI(advanced extensible interface)主机发送通道、AXI主机接收通道、AXI从机发送通道、AXI从机接收通道、ET专用通道7个物理通道和5套总线。

(1)通用通道:可将片外存储器中的数据搬到片内存储器,再将运算结果由片内存储器搬到片外存储器,同时可通过外设总线实现各部件参数的批量配置或读取。

(2)AXI主机发送通道:DMAC作为AXI主机主动从VM、ASRAM (asynchronous RAM)或DDR (double data rate SDRAM)读取数据,并将读到的数据转发给AXI从机。

(3)AXI主机接收通道:DMAC作为AXI主机主动向AXI从机发出读请求,并将从AXI从机接收到的数据写至VM、ASRAM或DDR中。

(4)AXI从机发送通道:DMAC作为AXI从机被动接收AXI主机读burst信息,并将从VM、ASRAM或DDR读到的数据返回给AXI主机,本通道在与AXI主机进行burst信息握手成功后,自动进行数据的传输,因而需要使用本通道时,只需要配置AXI主机方,不需要配置DMAC方。

(5)AXI从机接收通道:DMAC作为AXI从机被动接收AXI主机写burst信息,接收AXI主机写数据,并转发给VM、ASRAM或DDR。本通道与AXI从机发送专用通道一样,在与AXI主机进行burst信息握手成功后,自动进行数据的传输,因而需要使用本通道时,只需要配置AXI主机方,不需要配置DMAC方。

(6)ET专用通道:用于接收ET部件的请求,并对存储空间进行读写操作。若为读,它将读到的数据返回给ET部件。若为写,它将ET部件的写数据写往相应部件。

(7)总线仲裁:DMAC可以访问5套总线,分别为DMA总线、VM总线和外设总线、AXI主机总线和AXI从机总线。其中AXI主机总线和AXI从机总线为DMA和AXI主机之间的专用总线,DMA总线主要为EMIF(external memory interface)和ET部件服务,VM总线为DMAC和VM之间的专用总线,而外设总线则是DMAC访问片上存储器映射寄存器空间的通道。

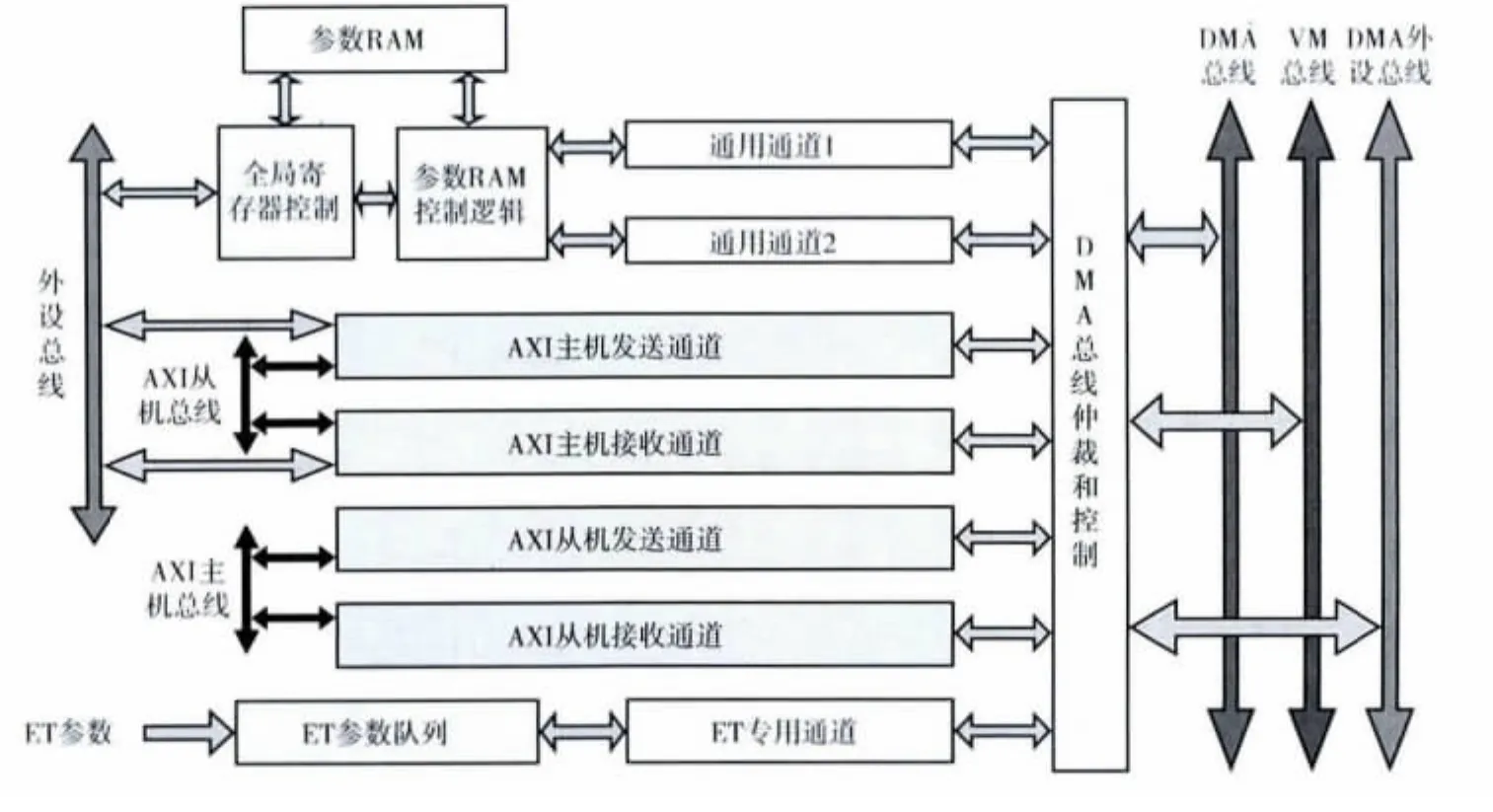

图3 DMA控制器和其他部件的接口

2.2 DMA控制器参数化设计

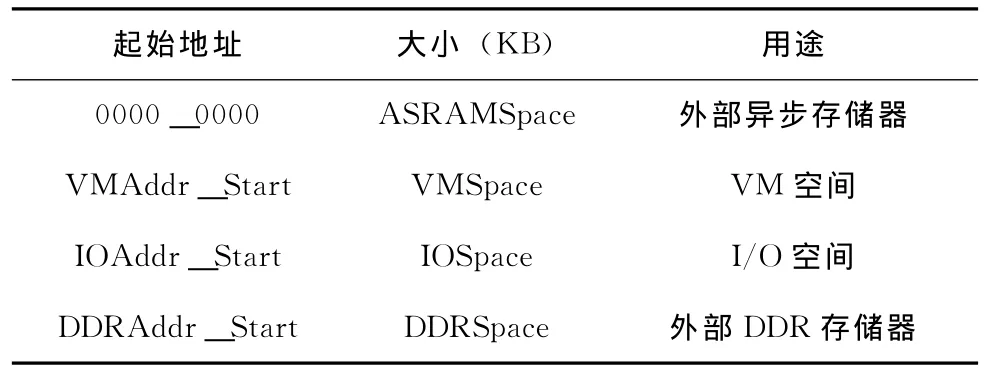

IP核的全局地址空间分配方案见表1。其中,ASRAM、VM、I/O空间和DDR的大小均可自己定义,I/O空间又可分配许多小空间。由此导致地址不固定的问题,而DMAC是根据地址向相应部件提供数据的,因此需要将地址进行参数化处理。

表1 全局地址分配

Verilog HDL语言提供了编译预处理命令`define[1],宏定义`define的语法为:`define宏名 字符串`define命令可以定义在模块里,也可定义在模块外,它的作用范围为定义命令之后到源文件结束。

参数化的DMAC需要定义的参数有:

`define ASRAMSpace

`define VM_Start_Addr

`define VMSpace

`define ETAddr_Start

`define DMAAddr_Start

`define DDRAddr_Start

`define DDRSpace

2.3 DMA控制器和其它部件的接口

DMA控制器和其它部件的接口如图3所示。

其中,向量数据流重整理缓冲器 (vector rearrange buffer,VRB)是为了解决DMAC (32位)和 VM (512位)之间带宽不匹配而设计的存储器,大大减少了DMAC访问VM的次数,使VM可以更好的为向量运算单元的数据访问操作提供支持,提高了系统性能。DMAC可通过EMIF访问片外存储器 (ASRAM和DDR)。

2.4 DMA控制器与外部接口协议介绍

DMAC的两个通用通道和ET专用通道遵循内部通信协议,AXI从机发送通道和AXI从机接收通道遵循标准的AMBA AXI协议,AXI主机发送通道和AXI主机接收通道遵循简化的AMBA AXI协议。以下仅对AXI协议作简要介绍。

AXI协议是ARM公司为适应SoC技术的发展,面向高性能、高频率的系统设计而适时推出的的新一代高速总线互连协议。

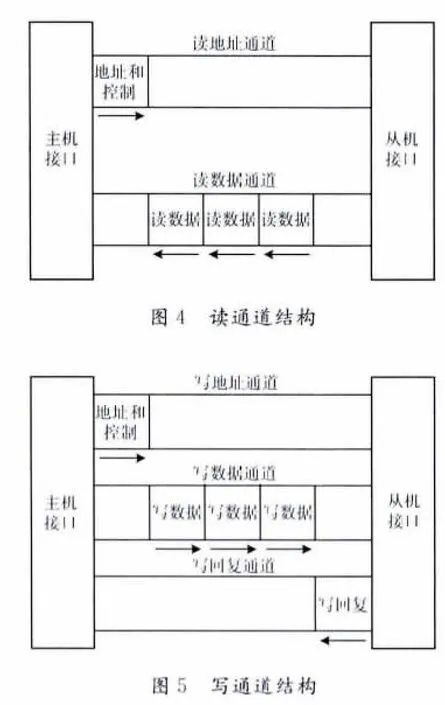

AXI协议[2]是基于突发传输的,读写分开的通道结构降低了直接存储器访问的开销。读通道由读地址通道和读数据通道构成,如图4所示。写通道由写地址通道、写数据通道和写回复通道构成,如图5所示。这5个独立的通道通过VALID和READY完成握手,当这两个信号同时为高才开始传输。

2.5 DMA控制器的特点

DMA控制器主要有如下特点:

(1)后台操作:传输数据的过程中CPU不参与,提高了系统效率;

(2)多种启动方式:CPU直接启动、外部同步事件启动、通道链接启动;

(3)多种同步方式:单元同步、源帧同步、目的帧同步、块同步;

(4)传输数据大小灵活:可按字节、半字、字传输;

(5)地址修改方式多样:源和目的地址可按固定、自增、自减、索引 (有符号数)方式修改;

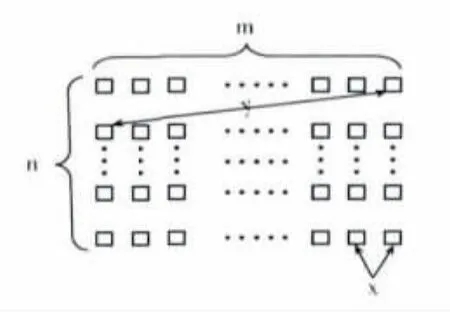

(6)支持二维传输:如图6所示,所需搬运的所有数据可以分成n帧,每帧帧内的数据间隔为x(这可以看成第一维),任意紧挨着的两帧中,前一帧的最后一个数据和后面一帧的第一个数据地址间隔为y(这是第二个维度)。一般地,所需搬运的数据有两种地址间隔,就需要用到二维传输;

图6 二维传输

图7 测试平台的结构

3.1.2 模拟验证验证过程

验证采用自底向上的验证方法,选用Cadence公司的NC-Verilog模拟器,通过观察波形和查看日志文件进行验证。验证流程如图8所示,其中覆盖率统计的是代码覆盖率。

(7)搬移数据能力强:配置一次,最大可搬移 (2n-1)*2n个数 (n为计数器宽度)。

3 功能验证

功能验证是指证明设计实现的电路模块的功能和设计规范中规定的功能是否一致的过程。在目前的SoC设计中,功能验证占整个设计流程的50%~80%,并且随着SoC规模和复杂度的增加,这个比例还可能增加,功能验证已成为SoC设计流程的最大瓶颈。

目前的功能验证方法主要有:模拟验证、形式化验证、基于断言的半形式化验证、仿真验证、软硬件协同仿真验证等。本文只对模拟验证和基于断言的验证进行研究。

3.1 模拟验证

模拟验证是传统的验证方法,是动态验证。它的优点是简单、使用灵活且不受设计规模的限制,目前仍然是主要的功能验证方法。缺点是随着设计规模的不断增大和复杂度的不断提高,要手工编写的测试激励非常庞大,验证所耗费的时间越来越难以忍受并且只能证明设计有错而不能证明无错。

3.1.1 测试平台的搭建

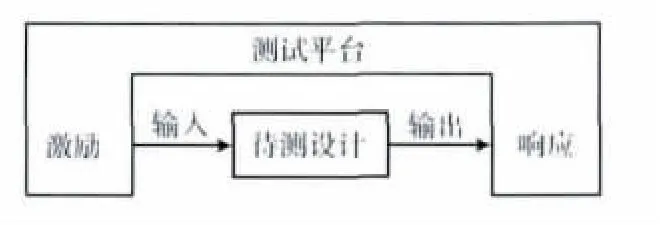

测试平台 (Testbench):通常指用来为设计产生特定的输入序列并观察响应的一段模拟代码。

测试平台的结构如图7所示:测试平台为设计提供输入信号,并监视设计的输出信号。其中输入激励在模块级是用硬件描述语言Verilog编写,在系统级是用汇编语言 (通过自主研发的开发环境将汇编语言转化为机器码)编写。

图8 模拟验证流程

其中,由于4个AXI通道是为用户预留的,可挂载遵循本设计协议的任何AXI设备,没有连接特定的部件,故系统级的验证成为了一大难点。为在系统级进行验证,我们将DMAC自身的AXI主机发送通道和AXI从机接收通道对接,AXI主机接收通道和AXI从机发送通道对接。

在进行大批量的数据传输时,我们编写了数据自动比较程序,大大提高了验证效率。

3.1.3 代码覆盖率

代码覆盖率是一种评估选取的测试激励好坏和执行被测设计程度的方法,也是衡量验证完备性的重要指标。它包括块 (block)覆盖率、表达式 (expression)覆盖率、翻转 (toggle)覆盖率和有限状态机 (FSM)覆盖率。

各覆盖率的作用如下:

块覆盖率:用于监视源代码的语句块的执行情况。

表达式覆盖率:用于提供条件表达式怎样执行的信息。

翻转覆盖率:用于测量设计活跃性,如未用到的信号、常量信号等。

有限状态机覆盖率:用于监视控制逻辑块的执行情况。

由于翻转覆盖率是度量设计活跃性的,与被测设计的功能无关,因此不做统计。

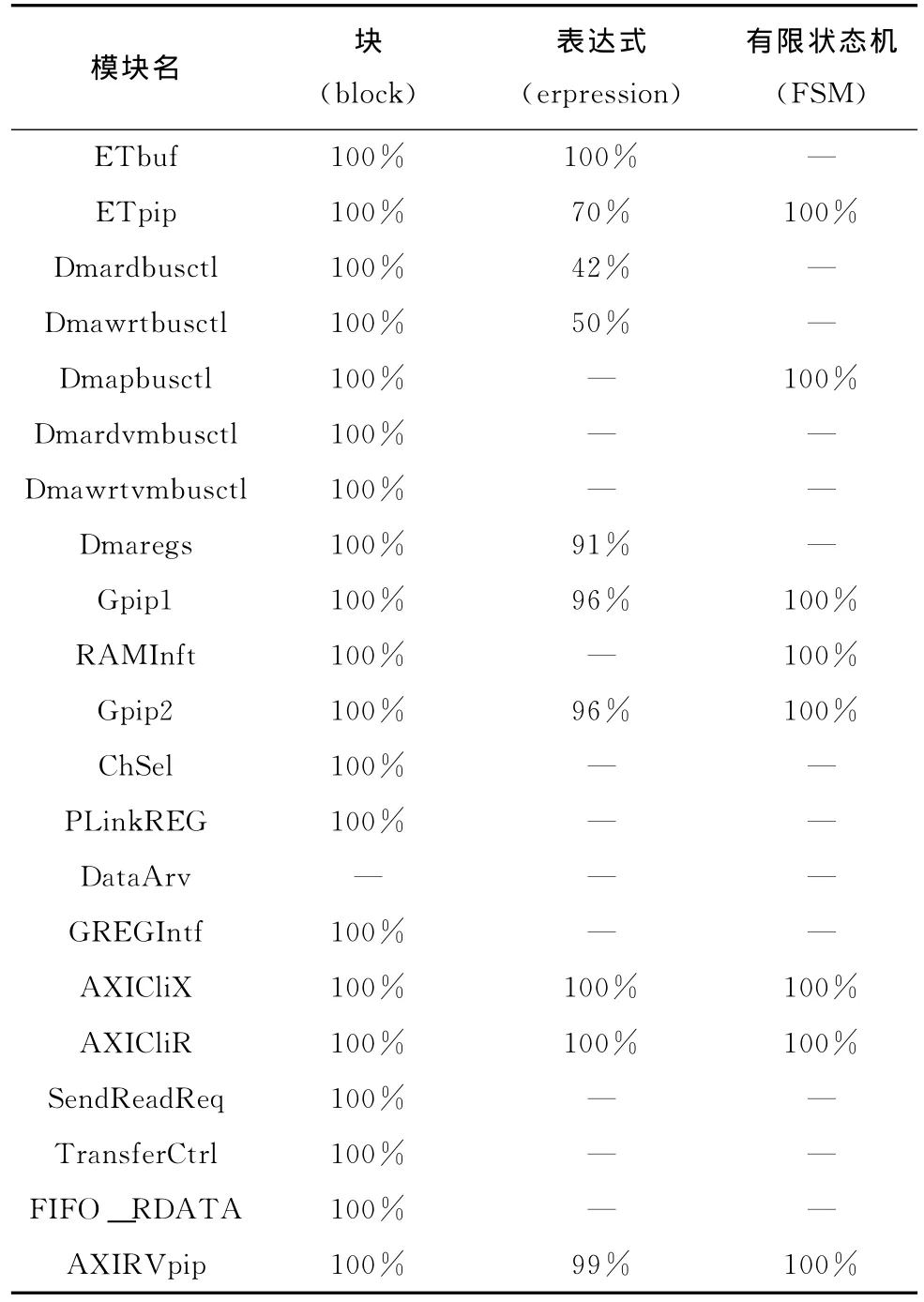

主要模块的代码覆盖率统计见表2。

表2 代码覆盖率

其中,表达式覆盖率未达到100%是由于覆盖率统计工具ICC列出的组合不存在。

3.2 基于断言的验证

断言是对设计的行为的描述,是一段代码。

基于断言的验证方法是半形式化验证方法。半形式化验证方法是一种混合形式验证方法,即模拟和形式验证相结合。模拟难以对整个状态空间搜素,形式验证不能处理大的设计。把两者结合起来就可以弥补相互的不足之处。

3.2.1 断言语言选择

目前,在集成电路设计中广泛使用的断言语言有:开放验证库OVL(open verification library)、属性描述语言PSL(property specification language)、SystemVerilog Assertion (SVA)[3,4]。

OVL是由Accellera组织推出的断言库,这个库是由数量有限的参数化的断言模板组成,用户只能被动地选择配置参数来实现自己想要的断言,难以满足实际中复杂多变的应用需求[5]。PSL是从IBM开发的Sugar这门属性语言演化而来的一种语言,验证能力虽然强大,但验证人员要使用它必须付出巨大的学习开销。

SystemVerilog语言是业界新兴的工程语言,它是对IEEE Std1364-2001Verilog Standard的一个扩展,其由Accellera标准组织维护并提交标准化,在2005年12月被标准化为IEEE P1800-2005。它作为统一的设计和验证语言,提供强大的面向对象编程技术,支持约束随机的产生,覆盖率统计分析和断言验证,被誉为下一代芯片设计和验证语言[6]。SystemVerilog作为一个IEEE标准语言,得到了Synopsys、Mentor Graphics和Cadence三大EDA工具提供商的一致支持,已成为设计和验证工程师的首选语言[7]。SVA是SystemVerilog语言的子集,能够满足验证需要,且简单易用,因此,我们选用SVA作为本课题的断言验证语言。

3.2.2 断言的优缺点

断言主要有以下优点:

(1)复用性好:传统验证方法中模块级验证和系统级验证所使用的激励是用不同的语言编写的,它们之间无法重用。而断言即可用于模块级,也可用于系统级,复用性好。若断言是参数化的,则还可以在不同的项目中复用。

(2)增加了功能覆盖率统计机制:传统验证方法的代码覆盖率可由覆盖率统计工具自动完成,功能覆盖率却无法自动统计。而在基于断言的验证中,覆盖率可通过和覆盖率属性 (cover property)或覆盖率组 (covergroup)进行描述,当断言被执行时,相应的功能就被覆盖到了。

(3)可缩短验证时间:Verilog是一种过程语言,不能很好地描述时序,而要检测时序,需要编写大量代码,而用SVA可用很短的代码实现,断言减少了编写代码的时间。另外,当设计有错误时,得花大量时间追溯错误发生的位置,而在基于断言的验证中,一旦断言监测到错误,工具就会报出出错的具体位置,大大节省了调试时间。

SystemVerilog断言 (SVA)虽可以完美的描述和控制与时序相关的问题,但却不适用于检测数据转换、计算和顺序错误[8]。

3.2.3 SVA的分类

SystemVerilog语言定义了两种断言:即时断言 (immediate assertions)和并发断言 (concurrent assertions)。

(1)即时断言:即时断言是基于模拟事件的语义,必须放在过程块的定义中,它们本质不是时序相关的,测试表达式被立即求值且只能用于动态模拟。

一个即时断言的例子如下:

always_comb

begin

a1:assert(a|b);

end

(2)并发断言:并发断言是基于时钟周期的,可以放到过程块(procedural)、 模块(module)、接口(interface),或者一个程序(program)的定义中[9],在时钟边沿根据调用的变量的采样值计算测试表达式且可以在静态(形式的)验证和动态验证 (模拟)工具中使用。

一个并发断言的例子如下:

a2:assert property (@ (posedge clk)a|->b);

区别即时断言和并发断言的关键词是 “property”。在验证过程中,大多使用并发断言,即时断言很少使用。

3.2.4 基于断言的验证过程

SVA包含assume、assert和cover这3个指令[10]。其中assume用于对环境进行假定,形式化工具用它来产生带约束的激励;assert用于监视它描述的设计的属性;cover用于监视覆盖率属性。SVA可以嵌入到设计代码中,也可放在单独的文件中。

我们选用Mentor Graphics公司的形式化验证工具Questa Formal进行验证,在验证之前,估测待测设计的规模完全在工具高效运行的范围 (25万门)之内。基于断言的验证流程如图9所示,我们采用 “灰盒”的验证方法,重点对控制逻辑、接口协议和总线仲裁进行了验证。

图9 基于断言的验证流程

3.2.5 验证结果

在验证过程中发现了一个功能缺陷和一个语法错误,对设计进行修改后,重新进行了验证,未发现新错误,达到了预期目标。

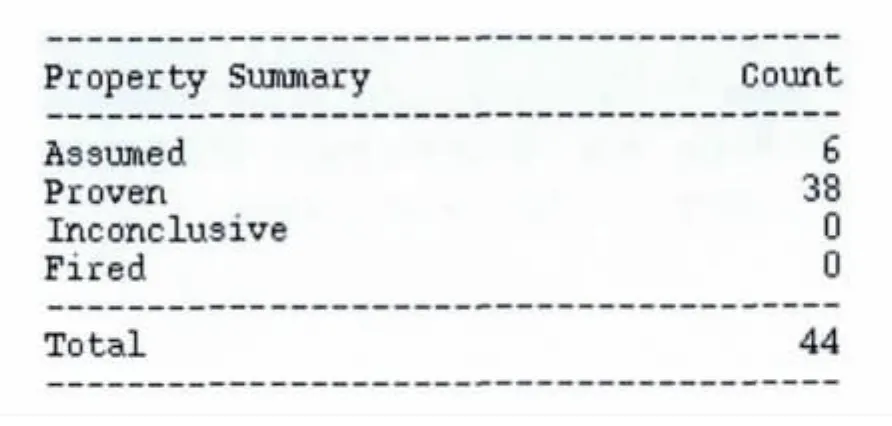

Questa Formal软件最终统计的断言属性检查结果如图10所示。

图10 断言属性检查结果

4 性能分析

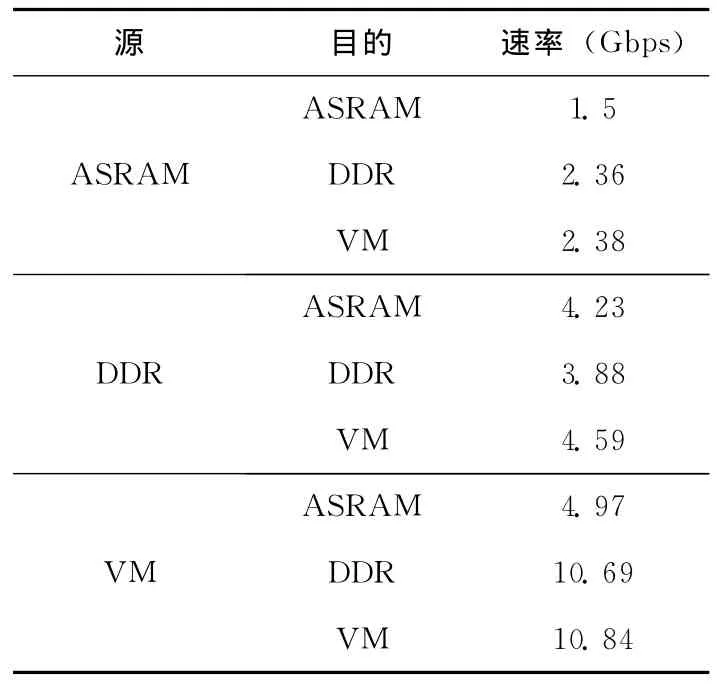

DMAC的数据传输速率统计如表3所示,结果表明设计的DMAC完全能够满足内核运算的需要。

表3 DMAC传输速率统计

5 结束语

本课题是在国家 “核高基”重大专项基金的支持下完成的。本文针对应用需求设计了可高效搬移数据的部件——DMA控制器,除对传统的模拟验证方法进行研究外,还重点对先进的基于断言的功能验证方法进行了研究。

传统的模拟验证方法目前仍是功能验证的主要方法,它能在设计的前期和早期发现大量和明显的错误,但随着设计规模的增大和复杂度的提高,已经越来越不能满足验证需求。

基于断言的验证方法与传统的验证方法相比,复用性好,增加了功能覆盖率统计机制,可缩短验证时间,并且能够发现传统验证方法无法发现的错误,提高验证质量。其缺点是能够验证的设计规模有限,得与模拟验证方法结合使用。

[1]XIA Yuwen.Digital system design tutorial for verilog [M].2nd ed.Beijing:Beijing University of Aeronautics and Astronautics Press,2008:106-107 (in Chinese).[夏宇闻.Verilog数字系统设计教程 [M].2版.北京:北京航空航天大学出版社,2008:106-107.]

[2]ARM IHI 0022D,AMBA AXITMand ACETMprotocol specification [S].2011.

[3]LIANG Lihua.Assertion-based verifieation researeh and Application [D].Dalian:Dalian Maritime University,2008:11-12(in Chinese).[梁丽华.基于断言的功能验证方法研究及其应用 [D].大连:大连海事大学,2008:11-12.]

[4]LIU Xuheng.The research of system verilog assertion-based verification method for nand flash controller[D].Hefei:Anhui University,2011 (in Chinese).[刘旭恒.基于SVA的 NFC验证方法研究 [D].合肥:安徽大学,2011.]

[5]Software Version 2.6,Accellera standard OVL V2library refe-rence manual[S].2011.

[6]ZHONG Wenfeng.Design and verification language of next generation chip:SystemVerilog (verification)[DB].http://www.cnki.net,2008 (in Chinese).[钟文枫.下一代芯片设计与验证语言:SystemVerilog (验证篇)[DB].http://www.cnki.net,2008.]

[7]ZHONG Wenfeng.SystemVerilog and functional verification[M].Beijing:China Machine Press,2010:20-35 (in Chinese).[钟文枫.SystemVerilog与功能验证 [M].北京:机械工业出版社,2010:20-35.]

[8]Janick Bergeron,Eduard Cerny,Alan Hunter,et al.Verification methodology manual for SystemVerilog[M].XIA Yuwen,YANG Lei,CHEN Xianyong,et al transl.Beijing:Beijing University of Aeronautics and Astronautics Press,2007:27-85 (in Chinese).[Janick Bergeron,Eduard Cerny,Alan Hunter.SystemVerilog验证方法学 [M].夏宇闻,杨雷,陈先勇,等译.北京:北京航空航天大学出版社,2007:27-85.]

[9]CHENG Gang.Research of functional verification based on system verilog [D].Guangzhou:South China University,2010:28-29(in Chinese).[程刚.基于System Verilog的功能验证方法研究 [D].广州:华南理工大学,2010:28-29.]

[10]IEEE Std 1800TM-2009,IEEE Standard for SystemVerilog-unified hardware design,specification,and verification language[S].2009.