基于NIOS II 处理器的HDLC 控制器IP 核设计

张显才,秦振杰,马 宁

(空军预警学院 黄陂士官学校,湖北 武汉 430345)

HDLC(High-level Data Link Control)[1]协议是通信领域中使用最为广泛的一种协议,是面向比特的数据链高级控制规程,具有很强的纠错能力,易于同步传输。目前有许多专用HDLC 协议控制器,这些控制器虽使用简单,但使用缺乏灵活性,很难适应不同版本的HDLC 协议,而且通道数目有限,内部FIFO 容量较小,无法适用于大数据容量或者多通道数据通信等情况下应用[2]。

NIOS II 处理器是ALTERA 公司的SOPC 解决方案,是一个运行于FPGA 系统之上的32 位RISC 处理器。这个处理器中的所有外设都以IP 核的形式封装于SOPC BUILDER中,可根据设计需要进行重复添加或删除。本设计采用ALTERA 公司Cyclone III 芯片EP3C16Q240 实现了内部FIFO容量为1 kB 的HDLC 控制器IP 核的设计。

1 HDLC 协议的基本原理

HDLC 协议也称链路通信规程,是由国际标准化组织制订的面向比特的同步数据链层协议[3,4]。HDLC 协议不依赖于任何一种字符编码集,数据报文可透明传输;在全双工通信时,不必等待确认即可连续发送数据,具有较高的数据传输效率。采用“0”比特插入删除技术,使得其具有较好的透明传输特性。数据帧均采用CRC-16 校验,传输可靠性高。以上这些优越性,是HDLC 协议广泛应用于数据链通信的重要因素,是通信可靠性的重要保证。

1.1 HDLC 帧结构

HDLC 协议对每次传输的数据位数无最大长度限制,非常适合于大数据量传输的场合。数据传输以帧为单位,HDLC 协议的帧格式如表1 所示。

表1 HDLC 帧格式

一个完整的HDLC 协议数据帧由帧起始字段,地址字段,状态控制字段,信息字段,帧校验字段以及帧结束字段6个部分组成。HDLC 协议规定,必须以一个标志字段起始,并且以同一个标志字段结束,这个标志字段用二进制数表示为“01111110”,即为十六进制数”7E”。帧起始字段和帧结束字段之间为一个完整的信息单位,称为一帧数据。在接收方,正是通过检测“01111110”来确定一帧数据的开始与结束。在帧与帧间的空载期,可发送连续的“01111110”作为填充。地址字段和状态控制字段的长度为1 个或2 个字节,主要用于标识发端设备的地址编码以及控制及状态信息。信息字段为所要传输的数据,数据长度可变。帧校验字段主要用于对所传输的数据进行检错。

1.2 “0”比特插入/删除技术

HDLC 协议规定,每帧数据以“01111110”作为标识符,以确定帧的起始和结束。但所要传输的数据中可能存在与帧起始(帧结束)字段相同的数据。为了防止在接收端误判,HDLC 协议在发送端采用了“0”比特插入技术。其基本原理是,在发送完帧起始字段后,只要已经连续发送了5 个“1”,就在其后面插入一个“0”,直到发送完校验字段,最后再发送帧结束字段。在接收端即采用了“0”比特删除技术恢复原始数据。“0”比特插入/ 删除技术也使得HDLC 协议具有良好的透明传输特性。

1.3 CRC 校验

HDLC 协议采用CRC-16 算法对地址字段,状态控制字段及信息段数据进行校验,插入的“0”不在校验范围内。

2 HDLC 控制器IP 核设计

整个IP 核设计包含HDLC 发送模块,HDLC 接收模块和Avalon 总线接口模块3 个主要部分。其顶层设计框图如图1所示。设计中,采用FIFO 存储器作为发送数据和接收数据缓冲器。借助于FIFO 的状态标志信息(空标志)来控制后续电路的工作。

在发送状态下,NIOS II CPU 首先将需要发送的数据进行组帧,即加入CRC 校验以及其他的地址及控制信息,然后通过Avalon 总线接口,将一个完整的HDLC 数据帧写入到数据发送FIFO 中。在数据写入之前或者完整的一帧数据发送完毕以后,FIFO 存储器的空标志信号有效,此时,并/串转换器的输入数据为HDLC 协议帧起始字段数据,即为十六进制数”7E”,并且此时,“0”比特插入模块不起作用。在工作时,每发送完成一次帧起始字段数据,都要检测FIFO 存储器的空标志是否有效,如果为无效,则表示存储器中有待发数据,则应从存储器中读出一个数据送入并/串转换单元,并使能“0”比特插入模块。

图1 HDLC 控制器IP 核框图

在接收状态下,帧起始检测单元检测HDLC 协议帧起始标志,这个帧起始标志标识着一个新数据帧的开始,同时也标识前一数据帧的结束。因此这个帧起始标识可以起两种作用,其一:作为接收模块的全局清零信号;其二:作为系统中断信号,通知CPU 读取接收数据。

2.1 关键模块设计仿真

2.1.1“0”比特插入/删除模块

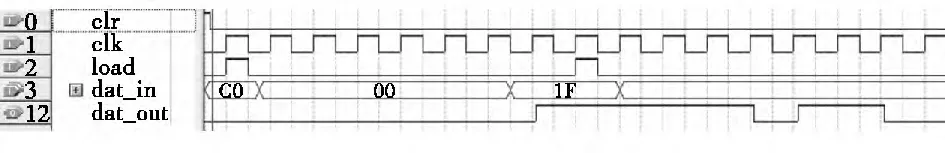

HDLC 协议规定,只要发端在已经连续发送5 个“1”的情况下,就需要插入一个“0”,以确保所发送的数据不会与帧起始字段(“7E”)相同,从而保证接收电路的帧起始检测单元不会出现误判。“0”比特删除模块是其逆过程。图2是“0”比特插入模块的仿真波形图。图中显示了连续2 个并行输入数据分别为十六进制数C0 和1F 情况下,数据的输出情况。dat_in 信号是模块的并行数据输入信号,load 信号是并行数据的加载信号,clr 是模块的清零信号,dat_out 信号为模块的输出。图3 为“0”比特删除模块的仿真波形图。图中显示的串行输入数据为已插“0”数据时,并行数据输出的情况。Clr 信号为模块清零信号,clk 信号为串行同步输入时钟,dat_in 为满足HDLC 协议的串行数据输入,dat_out 为并行解码输出数据。

图2 “0”比特插入模块仿真波形

图3 “0”比特删除模块仿真波形

2.2 Avalon 总线接口设计

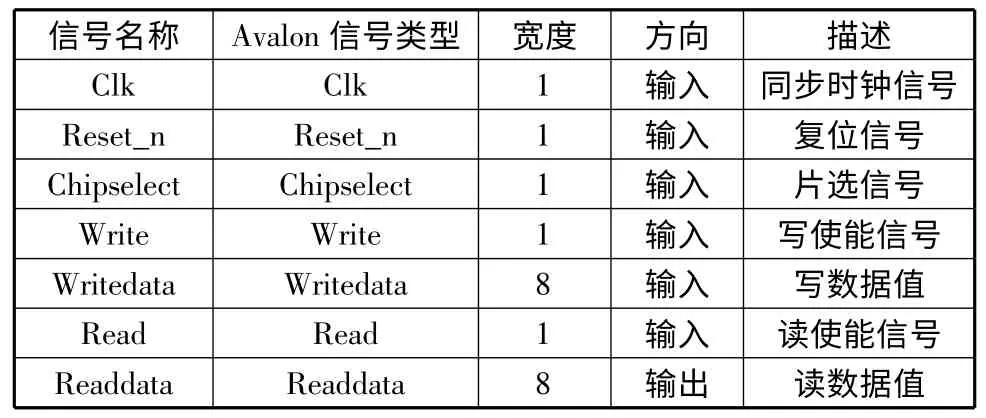

Avalon[5]总线为HDLC 控制器IP 核提供了一个标准的Avalon 从端口,通过此端口,按照从端口的传输协议,对IP核中的收/发缓冲器FIFO 进行数据读出或者写入。相关的Avalon 接口信息如表2 所示。

表2 Avalon 接口信号

3 设计验证

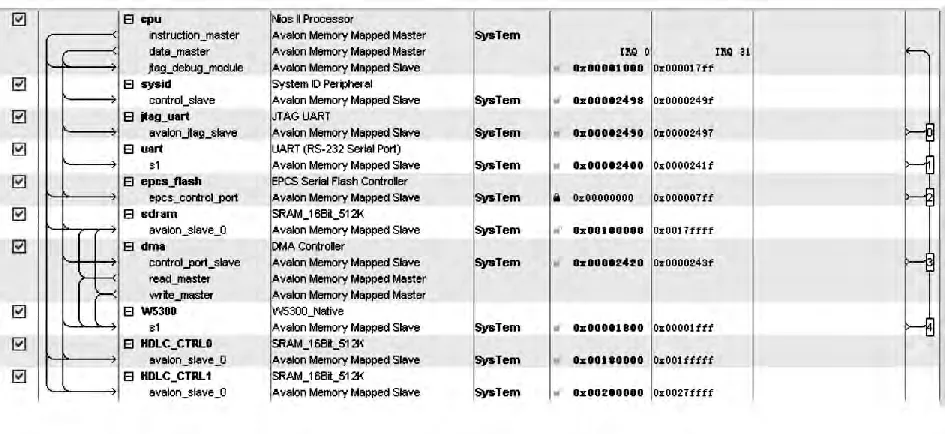

图4 所示为在SOPC BUILDER 添加二个HDLC 协议控制器的顶层设计图。此设计实现了TCP/IP 协议与HDLC 协议转化功能。在设计中,通过重复添加HDLC 控制器IP 核,以实现多通道HDLC 通信。在图4 的设计中,添加了二个HDLC 控制器IP 核,实现了双通道HDLC 协议转换功能。

图4 SOPC BUILDER 设计图

4 结束语

笔者成功地将此IP 核应用于某雷达情报组网系统设计中。设计实践表明,采用此IP 核,系统设计灵活,内部数据缓冲区的大小可以根据需要灵活设定,而且在FPGA 内部资源允许的范围内,可以通过添加多个此IP 核,实现多通道输出。

[1]ISO.International Standard 3309 Data Communication-High-level Data Link Control Procedures-frame Structure[S].ISO,1982.

[2]陈金华.基于HDLC 协议的RS485 通信设备的研制[J].测控技术,2010(6) :98-101.

[3]陈晨.基于FPGA 的高速同步HDLC 通信控制器设计[J].电子设计工程,2010(8) :175-178.

[4]李晓娟.基于FPGA 的HDLC 设计实现[J].现代电子技术,2007(6) :35-37.

[5]杜晓.基于NIOS II 处理器的SVPWM IP Core 设计[J].电子科技,2011(12) :72-74.