基于FPGA的监测接收机中DDC的设计与实现

曾 建,冯晓东

(重庆邮电大学 电信业务支撑系统研究所,重庆 400065)

随着通信技术的发展,无线电监测在军事和民用上都显示了其重要作用。数字下变频DDC(Digital Down Conversion)是无线电数字监测接收技术中的一种关键性技术,传统DDC大部分采用专用芯片来实现,而专用DDC芯片存在兼容性差、灵活性低等缺点[1]。由于软件无线电 SDR(Software Defined Radio)技术的快速发展,通过引进软件无线电技术来设计开发覆盖多频段、兼容多个通信体制的无线电数字监测接收机是未来无线电监测的主流[2]。本文根据某微波数字监测接收机功能需求,设计一个数字中频带宽可灵活设置的DDC方案。

1 数字下变频的设计方案

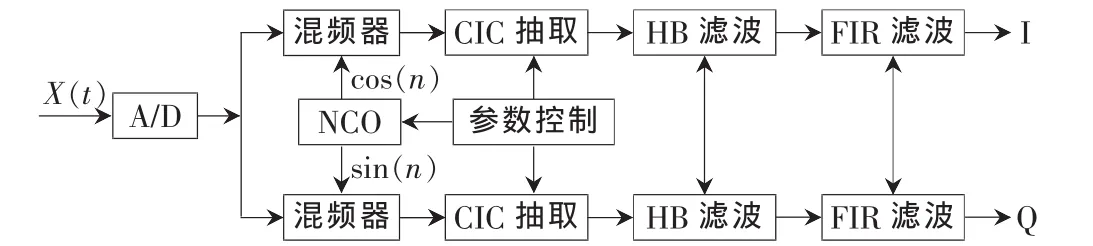

数字下变频器主要包括数控振荡器NCO(Numerically Controlled Oscillator)、数字混频器和数字滤波器3部分[3]。根据某微波数字监测接收机的功能需求,基于Spartan-6系列XC6SLX150T型号的FPGA芯片,设计一个模拟中频输入为75 MHz、采样频率为60 MHz、数字中频带宽最大为20 MHz的可灵活设置的数字下变频器。文中DDC数字滤波器组由3类数字滤波器以级联的方式组合起来,分别是积分级联梳状CIC(Cascaded Integrator Comb)滤波器、半带 HB(Half-Band)滤波器和 FIR滤波器[4],DDC结构如图 1所示。

图1 数字下变频原理结构示意图

2 数字下变频设计

2.1 数控振荡器设计

数控振荡器(NCO)是DDC中的复杂模块,也是影响DDC性能的重要因素之一。NCO的目标是产生一对频率可变的数字正弦或余弦信号,如式(1)所示:

其中,fLO是 NCO的本地振荡频率,fs是 ADC的采样频率。

在FPGA中,NCO可以采用查表法、实时计算法和CORDIC法等多种方法实现。由于FPGA中的资源有限,本文采用资源利用率较高的查表法来实现NCO,其工作原理是根据NCO的相位计算出相应的正弦值,然后以该相位值作为地址将对应的正弦值存到ROM中,当DDC中每输入一个待下变频的采样数据,NCO就自动增加一个×2π的相位增量,然后以相位累加值为地址,并将存放在该地址的正弦信号值送到数字混频器中与采样信号相乘,得到I/Q两路相互正交的信号[5]。

根据采样定理可知,ADC采样时会将75 MHz的中频信号左右搬移60 MHz的整数倍,即产生频率为(75±60×N)MHz的镜像信号,此时可以选择其中任意一个镜像信号来完成解调。文中选择15 MHz的镜像信号,即NCO产生一个频率为15 MHz的正弦信号与频率为15 MHz的镜像信号在混频器中混频,得到的差频信号就是基带信号。

在实现NCO时,影响NCO性能的主要因素有NCO的相位截尾误差和正弦信号的幅度量化误差,产生这两种误差的原因是正弦信号的相位和幅度在FPGA中是由宽度有限的存储单元来保存的,因此NCO中相位增量的有效数据位数有限,正弦信号的幅度在量化时也会产生一定的误差。为了降低误差对NCO性能的影响,本文设计的NCO相位增量的有效数据位数为32位,NCO输出有效数据位数为20位的正弦和余弦信号,NCO的频率分辨率为0.05 MHz,线性动态范围为120 dB。

2.2 积分级联梳状滤波器设计

随着现在无线通信中数据的传输速率越来越高,CIC滤波器在该领域中的应用显得更加重要。CIC滤波器的结构比较简单,占用的FPGA资源较少,工作速度快,因此它适合工作在高速采样的情况中,而且CIC滤波器的灵活性好,所以CIC滤波器常作为DDC滤波器组中的第一级滤波器。

单级CIC抽取滤波器包括积分部分和梳状部分[6],积分部分是一个反馈系数为1的单极点IIR滤波器,其传输函数如式(2)所示:

梳状部分是一个FIR滤波器,其传输函数如式(3)所示:

式中D为延迟因子,M为抽取因子。因此单级CIC滤波器的传输函数的幅频响应如式(4)所示。

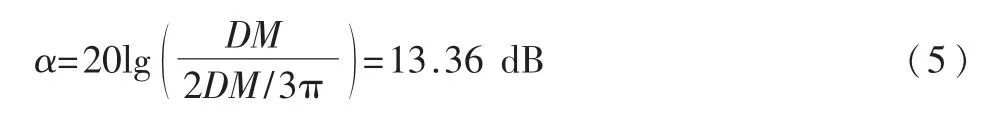

由式(5)可知,单级CIC抽取滤波器的旁瓣电平较高,阻带衰减较小。为了满足接收机的大动态范围的性能要求,实际中常采用多个单级CIC滤波器级联起来降低旁瓣电平,以获得较高的阻带衰减。根据单级CIC抽取滤波器的原理结构可知,包含N级CIC滤波器级联的系统的传输函数可以用式(6)来表示:

本文将5个单级CIC抽取滤波器级联起来构成5级CIC抽取滤波器,并将该5级CIC抽取滤波器抽取因子M设置为25。实际应用中,当数据速率较高时,微分延迟因子D一般设置为1或者2[6],文中将D设置为1。则5级CIC抽取滤波器的系统传输函数如式(7)所示:

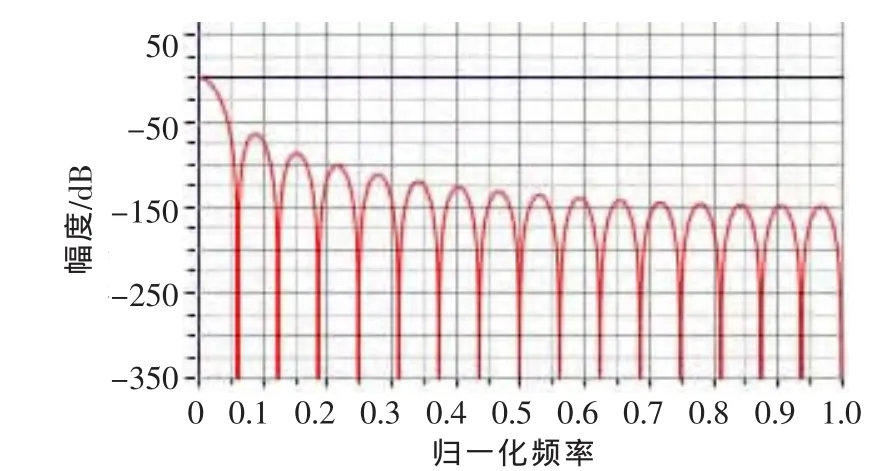

该CIC滤波器的幅频特性如图2所示。

图2 5级CIC抽取滤波器幅频特性

根据式 (7)可知,5级CIC抽取滤波器的阻带衰减为66.8 dB。

当DDC的数字中频带宽为6 kHz时,此时对I/Q信号做2次CIC抽取滤波处理,即数字混频器输出数据率为60 MS/s的I/Q信号进行625倍抽取滤波,则CIC抽取滤波器组输出信号的数据率为96 kS/s。当DDC的数字中频带宽为20 MHz时,I/Q信号不进行CIC抽取滤波处理,即数据率仍为60 MS/s。

2.3 半带滤波器设计

半带滤波器用于将离散系统的工作频率分成两个对等的部分,它的运算复杂度低,适用于实现M=2N倍抽取,而且效率较高。由于接收机在处理通信信号时对线性相位的要求较高,所以本文采用线性相位特性相对较好的FIR半带滤波器。

为了使半带滤波器具有线性相位特性,其系数必须具有偶对称性,即它的系数要满足 h(n)=h(N-1-n),其中N为FIR半带滤波器的阶数,除中心点n=+1外,所有 h(n)的偶数次系数都必须为零[6]。正因如此,在实现FIR半带滤波器时,它所占用的FPGA资源少,利于实时高效地实现数字信号处理。

当DDC的数字中频带宽为6 kHz时,半带滤波器输入数据率为96 kS/s的I/Q信号。为了进一步降低信号的数据率,文中将两个抽取率2的半带滤波器级联起来,以实现对信号的4倍抽取,此时I/Q信号经半带滤波器组抽取处理后,数据率变为24 kS/s。

当DDC的数字中频带宽为20 MHz时,根据监测接收机的功能需求,文中将I/Q信号通过一个抽取率为2的FIR半带滤波器,则半带滤波器输出I/Q信号的数据率为 30 MS/s。

2.4 FIR滤波器设计

由于半带滤波器的过渡带较宽,矩形系数较差,不适合作为DDC中多级滤波器的最后一级,因此本文设计了一个矩形系数较好的FIR滤波器,使DDC能够输出较好的波形。

当DDC的数字中频带宽为6 kHz时,FIR滤波器实现2倍抽取和波形整形功能。为实现该功能,文中设计一个67阶的FIR滤波器。经FIR滤波器处理,I/Q信号的数据率变为 12 kS/s。

当DDC的数字中频带宽为20 MHz时,为进一步降低I/Q信号的数据率,文中设计一个实现64/75倍抽取的2 048阶FIR滤波器,数据率为30 MS/s的I/Q信号经过高阶FIR滤波器处理后,其数据率变为25.6 MS/s。

3 DDC测试及结果

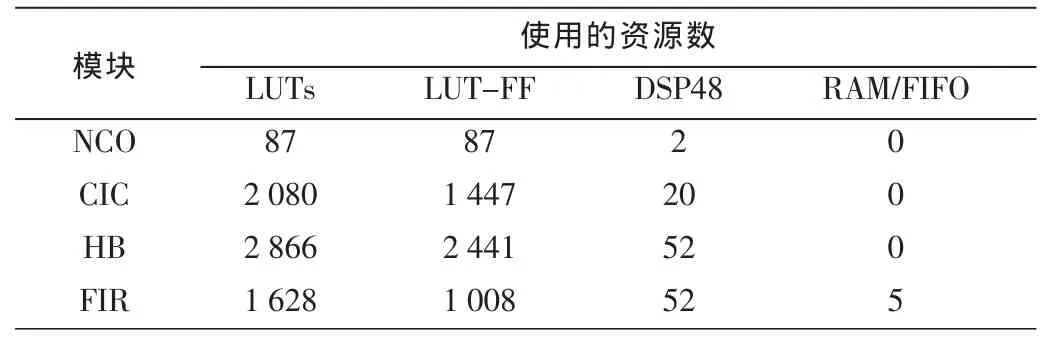

使用ISE14.3工具将DDC的Verilog HDL程序进行综合、布局布线得到DDC中各个模块的资源使用情况,如表1所示。

表1 DDC中各模块的资源使用情况

测试环境:用R&S公司SMA100型号的信号源产生75 MHz的中频模拟正弦信号,信号源输出模拟信号的功率为0 dBm。用模数转换器AD9265以60 MHz的频率对中频模拟信号进行采样,该ADC的采样精度为16 bit[7]。上位机与FPGA是通过网口通信,上位机发送指令设置DDC参数,然后对采样数据做DDC处理后发送给上位机,具体测试结果如下:

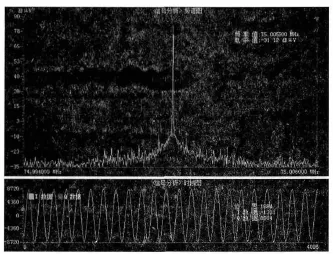

当DDC的数字中频带宽为6 MHz时,得到I/Q两路信号的波形以及对I/Q信号做1 024点快速傅里叶变换FFT(Fast Fourier Transform)运算得到的频谱如图3所示。其中上部分是频谱,下部分是I/Q信号,此时I/Q信号的无杂散动态范围SFDR (Spurious Free Dynamic Range)为 91.26 dB。

图3 6 kHz带宽时的I/Q信号波形及频谱

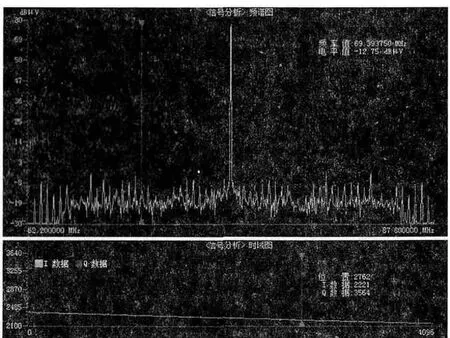

当DDC的数字中频带宽为20 MHz时,采样信号做DDC处理后得到I/Q两路信号的波形以及对I/Q信号做1 024点FFT运算后得到的频谱如图4所示,此时I/Q信号的SFDR为83.26 dB。

图4 20MHz带宽时的I/Q信号波形及频谱

综上所述,本文设计的数字下变频方案具有数字中频带宽、可灵活配置以及可处理宽带信号和窄带信号,并且能获得较大的线性动态范围的特点,可代替传统的专用DDC芯片,能够满足无线电数字监测接收机的频谱管理和无线电测向等功能需求,为现代无线电监测提供了一种高性能的数字监测接收机数字下变频的解决方案,具有广泛的应用前景。

[1]赵远鸿,宋学瑞.基于FPGA的数字下变频设计与实现[J].电子技术应用,2009,35(2):54-56.

[2]粟欣,许希斌.软件无线电原理与技术[M].北京:人民邮电出版社,2010.

[3]陈斌,杜仲,周世君,等.一种基于 FPGA的数字下变频算法设计[J].电视技术,2011,35(13):22-24.

[4]冯振伟,武小冬.基于FPGA的数字中频接收机设计与实现[J].通信技术,2010,43(4):17-19.

[5]严家明,李瑾,胡楚锋.基于正交混频的数字下变频技术研究[J].计算机测量与控,2009,17(1):200-202.

[6]西瑞克斯(北京)通信设备有限公司.无线通信的MATLAB和FPGA实现[M].北京:人民邮电出版社,2009.

[7]REV A.Analog Devices,16-Bit,125MSPS/105MSPS/80MSPS 1.8V Analog to Digital Converter AD9265[R]. 2009.