基于Cortex-M3的以太网硬件设计

李泓渊

0 引言

随着计算机网络化的日趋普及,网络几乎出现在我们生活的每一个角落。在众多的互联网技术中,以太网由于技术成熟、性能良好、联网成本低等优势,成为最流行的计算机网络技术之一。另一方面,嵌入式系统在工业控制、自动化仪器仪表及智能家电等领域得到了大量的应用。如何使嵌入式系统接入到以太网网络便成了嵌入式工程师不得不思考的一个问题。

事实上,人们已经提出了一些可行的嵌入式系统以太网硬件设计方案。大部分的硬件方案中,根据性能与成本的要求,一般使用 32位微处理器作为系统的主控芯片,如ARM7[1,2]、ARM9[3]等。另一些低成本设计方案中,考虑到移植协议栈时的大容量RAM需求以及以太网性能的需要,选择高性能8位单片机作为主控芯片,如AVR ATMega64[4]或 C8051F020[5]等。此外,也可以使用 FPGA[6]作为嵌入式系统的主控芯片。然而,无论使用哪种方案,都需要根据处理器的片内外设的不同而选择不同的以太网芯片方案。

若处理器中不包含任何以太网外设,则必须使用包含MAC和PHY的以太网控制器,如Silicon Labs的CP2200、Davicom的DM9000;如果单片机或微处理器的外设只包含MAC,如ST的STM32F107、NXP的LPC1788等微控制器,则在系统中需要使用一片含有 PHY的芯片,如 TI的DP83856A。

以上这些方案,无论怎么搭配,都需要2片芯片。相比于单芯片方案,这样的设计中,布线都较复杂。不仅如此,最终成品的PCB面积也往往比较大。这会产生一些问题,比如,复杂的布线不仅导致了设计和制造成本的增加,而且过多的芯片外部连线更容易受到干扰从而降低系统工作的可靠性。另一方面,较大的PCB面积也会导致生产成本的进一步增加。

在本方案中,将使用基于 ARM Cortex-M3内核的LM3S6100微控制器,单芯片配合外围元件器,实现嵌入式以太网接入的硬件设计。

1 LM3S6100微控制器

LM3S6100是一款32位的RISC处理器,使用的是32位的ARM Cortex-M3 v7M架构。事实上,这是一款非常适合应用于嵌入式以太网的微控制器。以下是与设计有关的一些硬件特性:

(1)支持硬件除法和单周期乘法;

(2)内部包含64KB的单周期Flash以及16KB的SRAM

(3)集成ARM SWD的JTAG接口;

(4)根据不同的配置,具有10到30个能够5V耐压的可配置GPIO ;

(5)3个通用定时器模块,每个由2个16位定时/计数器组成;

(6)兼容IEEE 8023-2002规格的10/100M以太网控制器;

(7)片上低压差稳压器,带有用户可编程的2.25V至2.75V输出。

在这里,由于受篇幅的限制,对于LM3S6100的特性,只列举了与本设计相关的部分。

本设计使用的 LM3S6100芯片的封装为 100个引脚的LQFP封装。关于芯片以及以太网的主要设计方案参考了LM3S6100的数据手册[7]。

2 LM3S6100核心电路

2.1 电源电路

不同于使用ARM7或ARM9微处理器的嵌入式系统,在使用LM3S6100微控制器时,不需要分别对内核和外设提供不同的电压。由于该微控制器中集成了片上低压差稳压器,因此,在使用LM3S6100微控制器的电路中,只需要提供3.3V的电压即可。在本系统中,电源电路原理图如图1所示:

图1 电源电路原理图

在该电源电路中,使用了Sipex的SP6201低压差稳压电源芯片将5V直流输入电压转换为3.3V直流输出电压。电源输入端和输出端分别对地接 10uF的滤波电容 C33和C34,这些电容分别降低了输入电压与输出电压的干扰,起到了稳定电压的作用。图1中的VDD是输出的3.3V直流电压的标号。

在本文中,模拟地和数字地根据经验而被尽可能地合理设计以使模拟信号与数字信号间的相互干扰最小。为了简化描述,本文原理图中出现的标号及本文的描述不区分模拟地和数字地。

此外,对于2.5V内部LDO输出,芯片的第7脚和第62脚分别对地接1个2.2uF和1个100nF的电容。

2.2 复位电路

由于LM3S6100是低电平复位的,因此,正常工作时,复位引脚需要接一个上拉电阻到系统高电平,即 3.3V。同时,为了使系统在上电后有一定的延时以满足其他外设的初始化需要,上拉电阻对地接一个100nF的电容。该电容的另一个作用是使复位引脚的电位不会发生突变,因而,不会由于该引脚上的干扰信号而发生错误的复位,从而有效地提高了系统的稳定性。复位电路原理图如图2所示:

图2 复位电路原理图

在图2中,按键K1提供了手动复位的功能。

2.3 时钟电路

在LM3S6100中有一个内置的振荡器,频率为12MHz。然而,这个振荡器的误差较大,达到了正负30%。考虑到以太网对于时钟准确性的要求,本设计使用了外部石英晶体振荡器作为系统主时钟的输入。

通过该处理器内置的 PLL,能够将倍增后的主振荡器(在本方案中为石英晶体振荡器)的频率作为系统的时钟信号。因此,石英晶体振荡器的频率不需要很高就能满足要求。本设计使用了 6MHz的石英晶体振荡器。时钟电路如图 3所示:

图3 时钟电路原理图

该图中,C25和C26为两个18pF的匹配电容,起到了稳定晶体振荡器频率的作用。

2.4 SWD接口电路

值得注意的是,为了进一步减小系统的PCB面积,本设计没有采用在 ARM 微处理器系统中常用的 20引脚的JTAG接口方案。在本系统中,SWD接口被用来替代传统的设计方案。

实际中,SWD接口只需要 4根连线就可以实现对LM3S6100的仿真与程序烧写的功能。本系统的SWD接口电路设计如图4所示:

图4 SWD接口电路原理图

图4中,R4和R5的作用是使得SWDIO和SWCLK引脚在空闲时上拉到高电平。SWD接口的第 1号引脚连接LM3S6100的复位引脚。

3 以太网相关电路

LM3S6100片内集成的兼容 IEEE 8023-2002规格的10/100M 以太网控制器为整个以太网相关电路的设计提供了极大的方便。由于该控制器已经包含了MAC和PHY,所以,一个隔离变压器、一个RJ45接口,以及一些外围元器件,就能够完成以太网电路部分的设计。

考虑到集成隔离变压器的RJ45接口能够进一步减少最终的PCB面积,本设计使用了汉仁公司的HR911105a型号的RJ-45接口,如图5所示:

图5 HR911105A RJ-45接口原理图

在LM3S6100的引脚中,与以太网有关的引脚名称分别为 ERBIAS、GNDPHY、VCCPHY 、LED0、LED1、XTALNPHY、XTALPPHY、MDIO、RXIN、RXIP、TXON和TXOP。

ERBIAS引脚是一个12.4kΩ的1%精度的电阻,该电阻被PHY内部使用。本设计中,该引脚接地。

GNDPHY和VCCPHY引脚分别是PHY的地和电源,分别接地和3.3V电压。值得注意的是,VCCPHY的每一个引脚需要对地接100nF的电容以提高引脚电压的稳定性。

LED0和LED1引脚分别串联一个1KΩ的限流电阻后分别连接到RJ45接口的GLED+和YLED+脚。GLED-和YLED-引脚接地。

XTALNPHY和XTALPPHY引脚分别是25MHz石英晶体振荡器的输出与输入端。这部分电路与图3的时钟电路类似。不同之处在于,这两个引脚需要连接一个25MHz的石英晶体振荡器而非6MHz。这部分电路原理图如图6所示:

图6 以太网时钟电路原理图

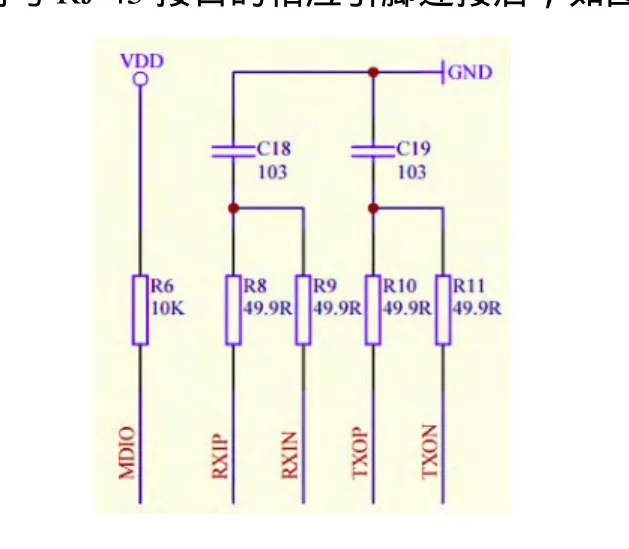

其余的引脚都与以太网的PHY有关。在本设计中这几个引脚分别与RJ-45接口的相应引脚连接后,如图7所示:

图7 PHY引脚连接原理图

此外,RJ-45接口的2个隔离变压器的中心抽头RX-CT和TX-CT引脚分别对地连接10nF电容后接3.3V电源。

4 总结

本论文列举了一些传统的以太网硬件设计方案,对存在的问题进行了讨论,并提出了一种基于LM3S6100微控制器的嵌入式以太网硬件方案。本文详细描述了LM3S6100的核心硬件电路以及与以太网有关的电路。基于本文所提出的以太网硬件方案已经成功设计制造出样品。该样品测试正常,工作稳定可靠。

[1]王钦玉,马维华.基于LPC2292的嵌入式Ethernet-CAN转换器[J].南京航空航天大学学报,2007,39(5):607-611.

[2]陈红彦,费凌,郑亮等.基于RTL8019的ARM和PC机间的TCP/IP通信[J].工业控制计算机,2010,23(8):57,89.

[3]袁安富,夏生凤.基于ARM和Linux的DM9000网络接口设计及驱动实现[J].计算机工程与科学,2011,33(2):27-31.

[4]张宇翔,刘伟,郭敏等.基于AVR高性能单片机的以太网接口设计[J].现代电子技术,2009,32(3):81-84.

[5]王天杰,原明亭.基于C8051F020的以太网远程监控系统的设计[J].化工自动化及仪表,2007,34(5):36-39.

[6]卢珞先,任立志.基于FPGA的网络接口设计与应用[J].电测与仪表,2008,45(12):56-58.

[7]TI公司.Stellaris LM3S6100 Microcontroller Data Sheet[R].http://www.ti.com.cn/cn/lit/ds/symlink/lm3s6100.pdf