基于时间数字转换器的数字输出电子式互感器校验系统

范 洁 ,程含渺 ,季欣荣 ,陈 刚 ,周 玉 ,陈 霄 ,易永仙

(1.江苏省电力公司电力科学研究院,江苏 南京 211103;2.华中科技大学 电气与电子工程学院,湖北 武汉 430074)

0 引言

随着智能电网的推广建设,具有数字输出的电子式互感器被大量应用于数字化变电站。为了确保测量准确性,需要定期对已投运的电子式互感器的准确度进行校验。根据电子式互感器现场校验规范,新投运的电子式互感器校验周期为1 a,实际可能更短[1]。因此需要研究数字输出电子式互感器校验系统。

针对数字输出电子式互感器校验系统的相关研究已经有很多,且取得了一定成果。早在1999年,瑞典CHALMERS大学的Jon Ivar Juvik等人就研究出了一种数字量输出的互感器校验仪[2]。2004年,加拿大的B.Djokic等人研究出了数字量输出电子式互感器校验仪,兼容 IEC60044-7/8、IEC61850-9等协议[3]。国内近几年对数字输出电子式互感器校验系统也进行了研究。文献[4]和文献[5]提出了基于高精度采集卡构成的电子式互感器校验系统,但该系统不能克服由于采集卡触发采样和开始采样非严格同步(以下简称非同步)造成的相位测量误差,使得校验系统整体准确度等级受到角差测量准确度制约。文献[6]和文献[7]提出的同步方式能有效克服采集卡非同步造成的相位测量误差,但其缺陷是同步信号是由采集卡的采样时钟分频而来,不能接收外同步信号,只能由校验系统发出同步信号。

综观目前已有的电子式互感器校验系统,根据A/D转换单元的区别,基本分为嵌入式A/D方案和采集卡方案。嵌入式A/D方案即使用A/D转换芯片实现A/D转换,虽然优点很突出,但其设计复杂度高,调试难度大。相比之下,直接使用采集卡则要简便得多,而且采集卡具有集成度高、精度高、性能稳定可靠等优点,结合当前的虚拟仪器技术,能快捷搭建高精度、高稳定性的校验平台。目前由采集卡构成的校验系统有2个固有缺陷:一是不能克服采集卡非同步,二是不能接收外同步信号,二者始终至少存在其一。产生这2个缺陷本质原因是采集卡采样非同步。本文针对上述问题,深入分析了非同步的原因并提出了解决方案。

1 采集卡触发原理分析

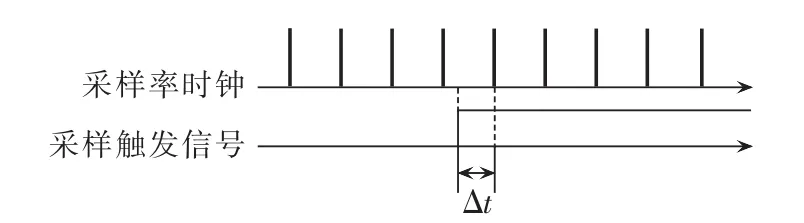

采集卡的本质是A/D转换器。A/D转换器的原理有很多种,尽管不同原理的A/D转换器的转换速度和精度不同,但其工作过程是相同的,即由采样触发信号控制,在工作时钟同步下工作。一次转换需要的时钟数由A/D转换器的原理和位数决定,一次A/D转换完成到下一次A/D转换开始的最短时间的倒数就是A/D转换器能达到的最大采样率。A/D转换器的转换精度主要受量化误差影响,即取决于A/D转换器的位数[8]。A/D转换器从接收到采样触发信号至开始采样存在微小的延时,在一般使用时并未考虑。但是在应用于校验系统时,这个延时会造成相位测量误差,有时该误差会相对较大,不得不予以考虑。采集卡触发采样和开始采样的时序图如图1所示。

图1 触发采样时序Fig.1 Time difference between triggering and sampling

图1中,上面的脉冲序列为采样率时钟,下面的脉冲为采样触发信号。从图中可以看出,采集卡从触发采样到开始采样,并不严格同步,有Δt的延时,从而造成相位测量误差ΔΦ。具体地,当被采样信号周期为T、采样率为fs时,最长采样延时(单位s)为:

由采样延时引起的最大角差(单位(′))为:

以4 kHz采样率为例,采样触发信号为外部秒脉冲(PPS)同步信号,与采样率时钟没有任何时间相关性。由图1可以看出,从采样触发信号上升沿到开始采样有延时Δt,其最大值为250 μs。对于50 Hz工频信号,1 μs 时间差对应 1.08′相位差,250 μs 即对应270′。目前的电子式互感器的准确度一般为0.2级,要求相应的校验系统的准确度至少为0.05级,对应的角差测量准确度为2′。过采样技术能在一定程度上改善幅值和相位测量准确度,但在相位测量方面,其效果仍然不十分理想。以24位高精度采集卡PXI/PCI-5922为例,在确保24位采样精度的条件下,即使以最高采样率(500 kHz)采样,对于50 Hz工频信号,由采样延时引入的相位差最大仍然可达2.16′,已经超出角差限值。此外,经济性也是重要的考虑因素。

由此可见,使用采集卡构建的校验系统,当接收外部同步信号时,由采集卡采样延时引起的测量相位差是必然存在的,且相位差与采样率和被采样信号频率均有关,制约了校验系统的整体准确度。使用过采样在一定程度上可以克服上述问题,但效果有限,且成本相对较高。为了提高校验系统的相位测量准确度,本文提出通过时间数字转换器TDC(Timeto-Digital Converter)技术测量采集卡触发采样到开始采样的时间差,再将时间换算为角度以校正相位的方法,具有良好的效果和经济性。

2 TDC单元的原理及实现

以上分析表明,采集卡的相位测量误差是由触发采样到开始采样的延时Δt引起的,如果能测量出Δt,则可以根据Δt校正相位。若被采样信号周期为T,则需要校正的相位值即为ΔΦ。

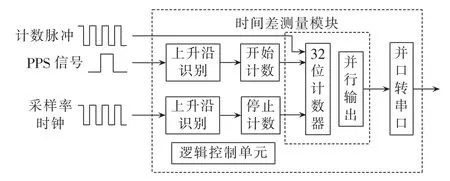

TDC技术是时间测量的基本手段和常用技术,常用的有计数器、电流积分、时间放大等方法[9]。针对本文中提到的需求,宜选择计数器法,下面介绍采用基于现场可编程门阵列(FPGA)的计数器法实现TDC时间差测量的原理。计数器法的基本原理是以被测时间起止时刻为计数门控信号,控制计数器对已知频率的脉冲信号计数。计数器在被测时间的开始时刻“开门”即开始计数,在被测时间结束的时刻“关门”即停止计数。具体地,以PPS采样触发信号的上升沿为“开门”信号开始计数,以该上升沿后的第1个采样率时钟的上升沿为“关门”信号停止计数,测量原理框图如图2所示。

图2 基于TDC的时间差测量原理框图Fig.2 Block diagram of time difference measuring based on TDC

在图2中,假设计数脉冲频率为fclk,计数器在PPS信号上升沿到来时开始计数,在紧接着的采样率时钟的上升沿到来时停止计数。在被测时间段内,计数器的计数值为N,那么被测时间Δt为:

由上式可知,fclk越大,测量时间的分辨率越高,Δt测量越精确。

选用Altera公司的CycloneⅡ系列的FPGA器件EP2C8T144C8,外接50 MHz有源晶振,作为EP2C8-T144C8工作时钟和计数器输入脉冲。在QuartusⅡ开发环境下,使用Verilog HDL开发图2所示的时间差测量电路的各个功能模块,最终生成顶层原理图,下载到EP2C8T144C8中[10],从而实现上述TDC单元。

TDC单元测量采集卡从触发采样到开始采样的时间差的具体实现方法如下:将采集卡的采样率时钟由RTSI总线路由出来,和PPS触发信号分别输入到时间测量电路的2个输入端,作为计数器开始计数和停止计数的控制信号,测量结果由串口反馈至校验系统的计算机,以据此校正测量的相位。

经实验验证,上述TDC单元的时间差测量准确度为±0.02 μs,对应相位校正量的准确度在50 Hz条件下为±0.02′。

3 校验系统实现及其准确度分析

3.1 校验系统实现

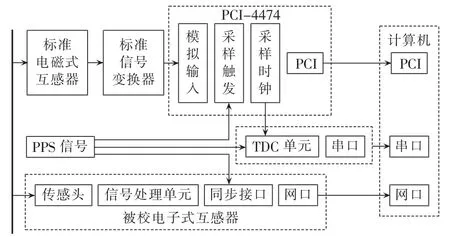

基于TDC的数字输出电子式互感器校验系统由采集卡、标准电磁式互感器、标准信号变换器、TDC单元、计算机和校验软件等组成。校验系统的构成框图如图3所示。

图3中,标准电磁式互感器、标准信号变换器和采集卡构成标准通道,标准数据经PCI总线送入计算机;被校电子式互感器作为被校通道,被校数据经网口以IEC61850-9-2格式帧送入计算机;标准路和被校路数据由外部PPS信号进行同步;同时,外部PPS信号和采集卡的采样时钟输入到TDC单元,测量采集卡从触发采样到开始采样的延时,测量结果由串口送入计算机。

图3 校验系统结构Fig.3 Structure of calibration system

计算机获取标准通道数据、被校通道数据和延时时间之后,由校验程序计算标准通道数据和被校通道数据的幅值和相位并进行对比,得出被校电子式互感器相对标准电磁式互感器的比差和角差。最后,根据测量的采样延时时间,对计算出来的角差予以校正。校验程序流程图如图4所示。

当被测电流或电压的频率偏移50 Hz,或者采样时间为非工频周期整数倍时,直接使用离散傅里叶变换计算相位和幅值会因非整周期采样而产生误差[11]。为了减小非整周期采样产生的误差,常用的有准同步算法、相位修正方法和加窗插值算法[12-15],本文的校验系统采用加二阶汉宁卷积窗的误差修正算法,对由于非整周期采样而产生的频谱泄漏误差做了修正[16]。

3.2 准确度分析

图3的校验系统引入测量误差的环节有标准电磁式互感器、标准信号变换器和采集卡A/D转换,引入的幅值误差分别记为 σ1、σ2、σ3,引入的相位误差分别记为 φ1、φ2、φ3,以下分别分析其误差。

采用0.02级标准电磁式互感器,引入的幅值误差σ1和相位误差φ1符合0.02级准确度要求。

采用0.02级标准信号变换器,引入的幅值误差σ2和相位误差φ2符合0.02级准确度要求。

本文校验系统使用PCI-4474采集卡,具有24位量化位数、45 kHz带宽和PCI通信总线,满量程为20 V,最大动态范围可达110 dB。A/D转换的最小分辨率为:

其中,Nc为A/D转换器位数;Umax为满量程输入电压。所以,24位采集卡的最大量化误差为:

本文实现的校验系统设计为额定条件下,采集卡输入电压为5 V。在校验S级电流互感器时,在1%的额定电流测试点处,由A/D量化引入的幅值误差为:

代入数值计算得到σ3约为±0.0024%,远小于±0.01%。

PCI-4474采集卡使用T-Clock同步技术,使得各通道以等时间间隔同步采样,同步时间误差小于10 ns,引入的相位误差φ31在50 Hz条件下为:

TDC单元采用基于FPGA的计数器法实现时间差测量,使用频率为50 MHz的计数脉冲,时间测量准确度为±0.02μs,在50 Hz条件下相位校正分辨率可达±0.02′。经校正之后由采集卡非同步采样引入的相位测量误差φ32在50 Hz条件下为:

由采集卡引入的相位测量误差在50Hz条件下为:

上述误差远小于0.01级互感器的角差限值。

标准通道的总体幅值测量误差为:

标准通道的总体相位测量误差为:

由误差分析可知,标准通道的总体幅值误差和相位误差均小于0.05级准确度互感器的幅值和相位误差限值。

综上所述,该校验系统在接收外同步信号时,能克服由于采集卡从触发采样到开始采样存在延时而造成的相位测量不稳定误差。配合加二阶汉宁卷积窗校验算法,该校验系统整体准确度可达0.05级,能对0.2级及以下电子式互感器进行校验。

4 测试结果

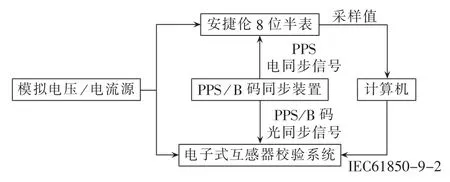

为了验证本校验系统所采用方案的可行性和校验系统的准确性,使用更高准确度等级的测量仪器对本校验系统进行了比对测试,测试的原理图如图5所示。

图5 校验系统测试原理图Fig.5 Schematic diagram of calibration system test

测试实验在国家高电压计量站互感器校验实验室进行,采用安捷伦8位半表测量的数据作为标准数据,通过GPIB总线传输到计算机,再转换为IEC 61850-9-2帧格式发送到被测试的电子式互感器校验系统。电子式互感器校验系统的测量数据作为被校数据,利用校验系统计算其和标准数据的幅值和相位,比对得出角差和比差。以电流校验为例,标准信号变换器的电流变换选择为5 A/4 V,即额定电流Ir为 5 A,在 1%Ir、5%Ir、20%Ir、100%Ir和 120%Ir测试点处的10次测试数据的比差和角差平均值分别列于表1和表2。

表1 比差测试数据Table 1 Results of ratio error test

表2 角差测试数据Table 2 Results of phase error test

由表1、表2可以看出,在上述测试点处,本校验系统均满足0.05级准确度要求,且通过多次测试,比差的单点波动不超过0.02%,角差的单点波动不超过0.2′。由于电流互感器测试点比电压互感器测试点动态范围更大,因此校验系统的测量准确度在校验电压互感器时也满足0.05级。

测试结果表明:本校验系统稳定性好,能够接收外同步信号,测量准确度可以达到0.05级。

5 结论

本文分析了基于采集卡的校验系统存在的2个固有缺陷,指出这2个固有缺陷的根本原因是采集卡采样触发机制,即触发采样到开始采样不严格同步,并定量分析了这种触发机制对相位测量准确度的影响。据此,提出了一种新的电子式互感器校验系统,通过TDC单元测量采集卡从触发采样到开始采样的延时,对测量的相位进行校正,有效解决了上述问题。在校验算法上,采用加二阶汉宁卷积窗算法,抑制非整周期采样对测量精度的影响。

本文所实现的TDC单元,其时间差测量准确度为±0.02 μs,在50 Hz工频条件下,对应相位校正准确度理论上可以达到±0.02′,为实现基于采集卡并能接收外同步信号的高精度校验系统提供了一种切实可行的方案。受某公司委托研发的基于TDC的数字输出电子式互感器校验系统已应用于该公司电子式电流互感器出厂误差检验。