基于FPGA的SoC原型验证方法研究

冯凌霄,张 冰

(江苏科技大学 电子信息学院,江苏 镇江 212003)

基于FPGA的SoC原型验证方法研究

冯凌霄,张 冰

(江苏科技大学 电子信息学院,江苏 镇江 212003)

在SoC设计的多种验证方法之中,基于FPGA的原型验证是一种较为贴近实际芯片的验证方法,可以大幅降低流片的风险,提高验证的效率和全面性。以一款基于OR1200的TD-LTE基带芯片为例,从原型验证的硬件平台设计、环境搭建以及验证的实现等方面阐述了基于FPGA原型验证的方法,并结合实际经验对原型验证中的一些问题提出了解决思路。

系统芯片;现场可编程逻辑门阵列;原型验证;验证方法

SoC(system on chip,系统芯片)设计技术产生于上世纪90年代中期,随着集成电路产业的快速发展,SoC设计也在朝着规模更庞大,功能更复杂的方向发展。对于如今的SoC设计而言,较大的逻辑规模使得代码的编写在整个设计中所占用的时间相对减少,更多的时间被用在了对芯片的验证上。SoC设计的验证方法较为丰富,在实际工程中应用较多的有仿真验证、静态验证、形式验证、物理验证、以及基于FPGA的原型验证等[1]。

诞生近30年来,FPGA工艺技术日趋成熟,其功耗、成本不断降低,规模、速度以及易用性不断增强,使得FPGA的应用日益广泛。原型验证就是FPGA的一个重要应用领域。这种通过将SoC代码移植到FPGA平台上实现的验证方式,相对于传统的纯软件仿真验证手段可以节省更多的时间,便于软硬件的协同开发,同时能够降低流片风险,提高成功率。

本文通过一款以OpenRisc1200处理器为核心的基带芯片,阐述了原型验证硬件资源的整合、IP替换、顶层集成、测试激励仿真、综合实现以及硬件联调等FPGA原型验证的软硬件平台构建和使用方法,有效的缩短了SoC开发时间,降低了成本,提高了流片成功率。

1 基于OR1200的基带芯片设计

本文所述的是一款应用于Femto家庭基站,满足TDLTE协议标准的基带处理芯片。该芯片采用OpenRisc系列精简指令集处理器OR1200作为控制核心。OR1200采用哈佛结构、5级流水线,支持虚拟存储器和基本DSP功能,具有执行效率高,功耗低,结构简单等优势。

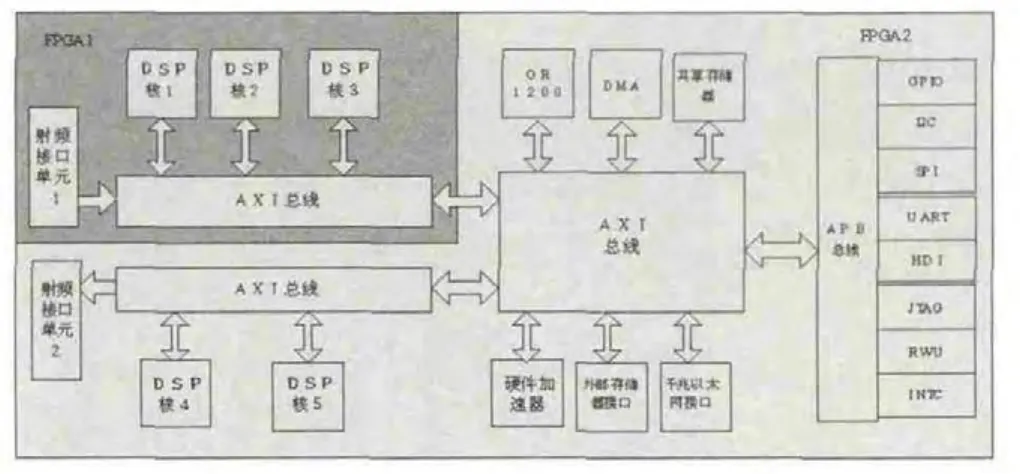

芯片功能模块的互联采用AMBA(AdvancedMicrocontroller Bus Architecture)系列总线,它是ARM公司开发的一种应用于SoC设计的互联总线标准[2]。在本设计中,芯片内部模块间数据传输对速度要求较高,外设接口对数据速率要求相对较低,因此分别采用AXI和APB总线。

基于OR1200的基带芯片架构如图1所示,除了OR1200和AMBA总线外,整个系统还包括射频接口单元,硬件加速器,DMA模块,千兆以太网MAC控制器,多个可编程矢量DSP核,以及I2C总线,同步串口SPI,复位及看门狗单元(RWU)等多个模块。

2 FPGA原型验证硬件平台的设计

图1 基于OR1200的基带芯片架构图Fig.1 Structure diagram of OR1200 based baseband processor

由于逻辑资源相对匮乏,FPGA初诞生之时,仅仅是作为可编程逻辑器件的延续,主要用于实现粘合逻辑等低复杂度的数据处理。近年来随着集成电路工艺发展,FPGA的逻辑规模突飞猛进,为SoC的原型验证提供了巨大的发挥空间。如今在FPGA原型验证中,数颗甚至一颗FPGA搭建的硬件验证平台就能完全满足大部分SoC设计的验证需求。

在FPGA原型验证硬件平台的设计中需要考虑以下两个方面:一是SoC设计的FPGA原型验证硬件平台的架构与最终芯片尽可能保持一致,从而使FPGA原型验证可以真实地模拟SoC设计的各种功能,保证验证的质量,以及最大限度的实现设计重用;二是在能够满足当前验证需求的前提下,在设计时兼顾验证平台的通用性及可扩展性,使之在其他设计中可以重复利用,从而节约成本。

图2 FPGA原型验证硬件平台结构图Fig.2 Structure diagram of FPGA-based prototyping verification hardware platform

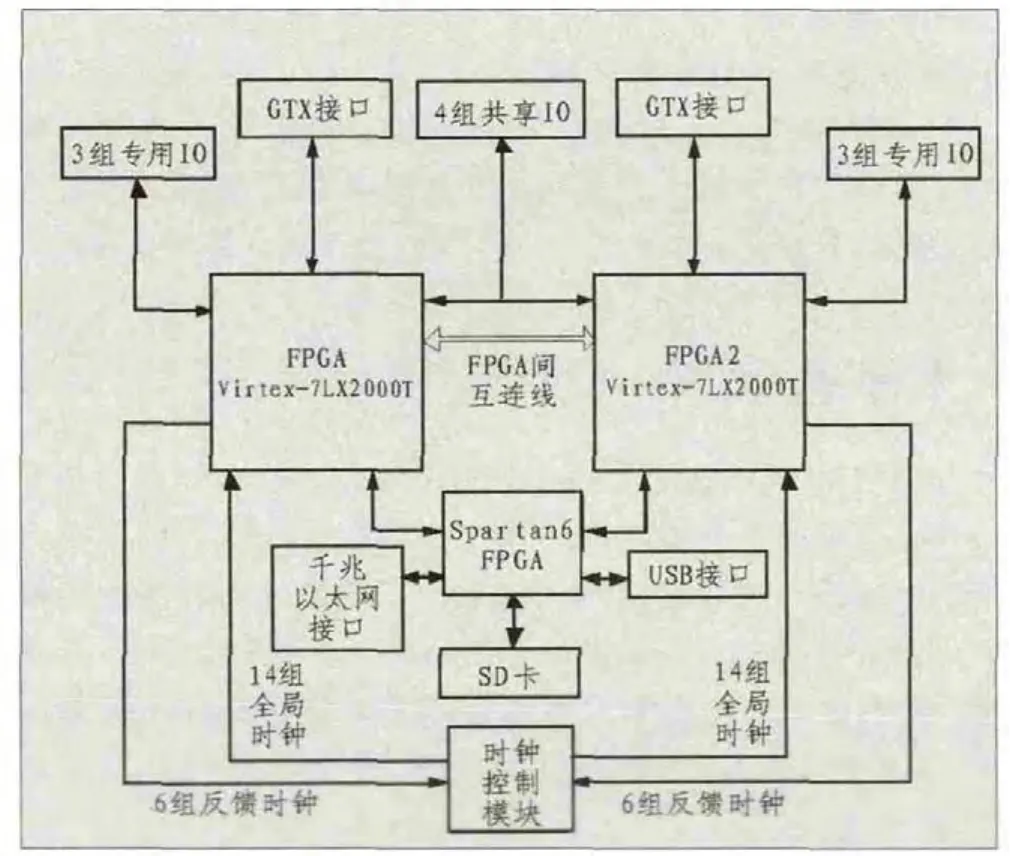

本课题设计的原型验证硬件平台结构如图2所示,该验证平台具有两颗Xilinx Virtex7系列的2000T FPGA。2000T FPGA芯片采用了3D堆叠技术,使得两颗芯片具有4000万等效逻辑门的资源。原型验证硬件平台上的时钟控制模块为FPGA提供14组全局时钟,6组反馈时钟用于FPGA之间时钟信号的传递,50组LVDS信号线用于FPGA间数据传输,两颗FPGA具有4组共享IO接口,同时每颗FPGA各具有三组专用IO接口。常用外设通过子板与验证平台的IO接口相连来使用。通过相应的接口可以将该平台与PC机、示波器、通信分析仪等设备连接,搭建完整的通路进行链路级的验证,提高原型验证的完备性。该原型验证硬件平台采用全FPGA的方案,可以实现与芯片架构一致的验证,具有一致性好,灵活性高,可扩展性强,容量大,通用性好的优点。

3 FPGA原型验证环境的搭建

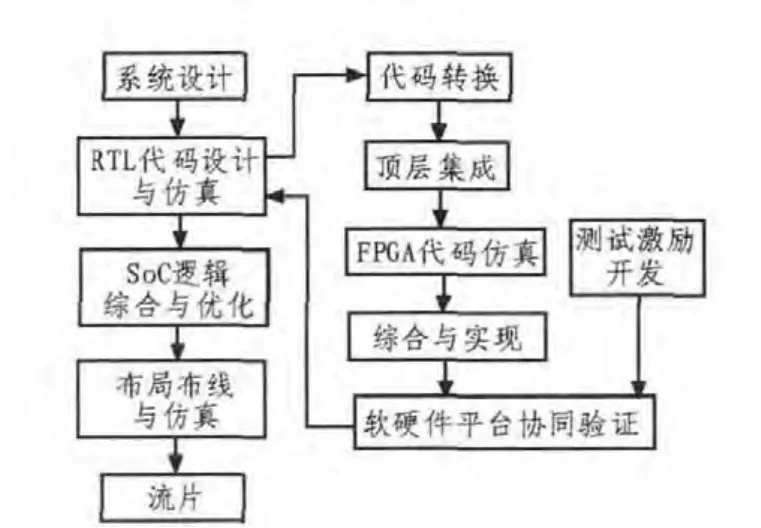

SoC设计的FPGA原型验证与SoC芯片的设计以及FPGA原型验证硬件平台的资源结构密切相关。在SoC设计完成代码设计和功能仿真后,就可以开始基于FPGA的原型验证环境的搭建。通过一系列的操作,将代码下载到FPGA上,在其中运行大量的测试激励,进行模块级、系统级的验证,验证完成后将验证结果反馈到SoC设计中,以进行相应的软硬件修改。基于FPGA的SoC原型验证流程如图3所示。

图3 基于FPGA的SoC原型验证流程图Fig.3 Flow chart of FPGA-based prototyping verification

3.1 代码转换

作为可编程器件的FPGA与SoC设计所采用的ASIC工艺是不一样的。FPGA采用的是基于查找表的结构,而ASIC工艺则是基于相应芯片制造厂提供的标准单元库。综合工具可以完成RTL代码到标准单元库的映射[3]。FPGA与SoC基本结构的不同,导致了SoC设计的RTL代码需要做一定的修改才能移植到FPGA中。

3.1.1 存储单元的替换

SoC的存储单元通常是芯片制造厂定制的,是不可综合的。而FPGA厂商通常提供经过丰富验证的成熟的存储单元IP核供用户使用,因而在原型验证时需要进行存储单元的替换[4]。在存储单元替换过程中,需要注意SoC与FPGA存储单元的信号触发方式是否完全一致。在本设计中,两者的片选和读写时能信号就是完全相反的。为了提高代码的一致性,使用条件编译来进行存储模块的顶层例化。

3.1.2 门控时钟的处理

在SoC设计中使用门控时钟是为了降低功耗,但是由于FPGA特殊的布线结构,如果使用门控时钟的话,容易产生毛刺,使数据传送发生错误。另外,使用门控时钟既不能用来准确估算SoC芯片最终的功耗,门控时钟所降低的功耗对于用来原型验证的FPGA而言又没有实际的意义,所以对门控时钟和时钟选择器采取的方案是直接屏蔽掉相关功能。

3.1.3 其他IP模块的替换

在SoC设计中,除了上述IP以外,通常会用到其他的IP,如锁相环,除法器,乘加器等。如果FPGA综合工具无法综合这些IP,都需要进行相应的替换。

3.2 代码的布局规划和顶层集成

在完成IP的替换以后,需要对RTL代码进行顶层集成。在顶层集成之前,需要根据FPGA的容量以及RTL代码的逻辑规模进行代码的布局规划。在本设计中,基带芯片的逻辑规模在2000万门以上,而单片Virtex7 2000T FPGA的等效逻辑门数接近2000万门,考虑到时钟走线以及布局的因素,要满足基于0R1200基带芯片的验证需求就需要使用两片FPGA。因而,就要对基带芯片的RTL代码进行布局规划。图1标示了基带芯片各模块在两片FPGA中的布局规划。其中,将接收部分置于FPGA1中,发送部分以及系统控制部分置于FPGA2中,两者的信号传送采用FPGA之间的高速差分互连线实现。

完成上述步骤之后,就可以根据规划进行顶层集成,将各个功能模块集成为两个顶层模型,使得两个顶层模型分别对应于两个FPGA。在顶层集成中,除了考虑各个模块的位置以外,还需要注意以下几个问题:首先,在顶层集成时,可以根据硬件平台的资源情况对两个FPGA之间的互联信号进行调整,以提高芯片间通信的质量;其次,需要考虑整个系统的时钟和复位的安排,必要时可以添加一些模块或原语,使设计满足FPGA的设计规则,保证两片FPGA的协调工作;最后,整个基带芯片验证系统接口的布局也需要根据硬件平台的资源在顶层集成时予以考虑。

3.3 代码的VCS仿真

由于对SoC设计的代码做了前述的一系列修改,为了保证基于FPGA的原型验证的等效性,在综合之前需要对修改后的代码进行仿真[5]。

本设计使用SYNOPSYS公司的VCS仿真工具进行仿真。VCS仿真工具提供了GUI和脚本控制两种操作方式,为了保证设计的一致性,使用脚本语言控制VCS的运行。只需要对控制脚本makefile、文件列表以及测试激励略作修改,就可以进行仿真。Makefile会依据不同的设置进行不同的仿真。该仿真方式操作简单,可重用性好,便于代码的版本控制。

为了验证代码修改前后的等价性,可以针对相应模块设计测试激励。假设在IP核替换时对DDR2控制器、OR1200处理器、以及DSP核的ram进行了替换,那么可以设计一个测试激励通过OR1200处理器在以上各个模块的ram之间存取数据。遍历所有相关的ram完成仿真以后,可以通过VCS的DVE组件查看仿真波形。如果仿真结果正确,则说明对RTL代码的修改是等效的。图4所示为DDR2控制器模块的仿真波形。通过VCS仿真不仅可以查看代码修改前后是否等效,还可以检查出顶层集成时的语法错误,另外DVE组件对于查看代码结构和定位错误也特别方便。

图4 DDR2控制器的仿真波形Fig.4 Simulation waveform of DDR2 controller

3.4 综合与实现

在修改后的RTL代码通过仿真以后,就可以开始代码的综合和实现。综合是将对电路高级的HDL语言描述形式转化成低级的门级网表描述形式;实现是将对电路的网表形式的描述映射到FPGA器件中,使得FPGA具备所需要的功能。

在基于OR1200的基带芯片的原型验证中,出于对代码综合效率及质量的考虑,先由synplify综合代码,然后使用vivado对综合输出的网表进行实现。软件的运行由脚本控制,使综合与实现流程完全自动化,从而减少了时间的消耗,加快项目的进度。

3.5 可配置文件的生成与下载

Vivado软件在完成布局布线以后,会生成一个可配置FPGA的比特流文件。分别将两个FPGA的可配置文件通过usb blaster下载到FPGA中。至此SoC设计的功能就在FPGA原型验证平台上实现了,原型验证的系统环境搭建完成。

4 基于FPGA的原型验证实现

基于OR1200的基带芯片FPGA原型验证系统环境搭建完成以后,就可以开始对芯片及主要功能模块进行硬件平台上的原型验证。验证工作包括:基带芯片设计内部各功能模块之间的接口、AMBA总线的工作状态、复位系统、程序下载功能、省电模式以及基带芯片与射频芯片协议栈芯片通信的动态行为。这些验证工作可以大致分为两类:模块级验证和系统级验证。

4.1 模块级验证

模块级验证的主要目的是保证各功能模块在硬件上实现后,能够达到预期的功能,从而便于后续的系统级验证。模块级验证的主要思想是,通过激励配置源对待验证模块发送激励,通过vivado提供的内建逻辑分析仪ILA,辅以示波器等仪器分析待验证模块内部及输出信号。

对于不同的模块,其激励配置源的产生可以有不同的方式,可以通过编写C语言程序下载到OR1200中,用OR1200来产生;也可以使用PC机发送配置数据,通过USB接口控制器转换成满足AXI协议的格式,发送给待验证模块。在具体进行模块级验证时,可以根据待验证模块的验证需求及其自身结构选择激励配置源的产生方式。

对待验证模块输入激励后,可以使用vivado的内建逻辑分析仪ILA观测所需信号。该工具的原理是利用FPGA内部未被使用的存储器块建立一个逻辑分析软核,该逻辑分析软核能实时的观测信号的状态将波形数据存储在存储器块中,并通过JTAG接口发送给PC机,显示时序波形。图8所示为测试DDR2模块时ILA捕获的波形。通过ILA采集模块内部信号,示波器等仪器采集外部信号,便能有效的分析待验证模块的状态及其响应。

值得一提的是模块级验证并不要求也不必要对设计中的每一个功能模块都进行验证。在验证方案制订时,对于前期已经进行过较完备验证的模块,可以不进行模块级验证[6];如果原型验证较为紧迫的话,一些不影响系统运行的非关键模块也可以不进行模块级验证。

图5 ILA捕获的DDR2模块的波形Fig.5 Waveform of DDR2 captured by ILA

4.2 系统级验证

完成模块级验证以后,便可以开始系统级验证。系统级验证与模块级验证的区别在于,模块级验证仅仅涉及SoC设计中的单个或少数几个模块,而系统级验证的对象则将整个系统的大部分甚至所有模块包括在内。在系统级验证中,原型验证的重点不再局限于各个模块的功能,而是整个系统的行为。

以基带芯片[7]的下行接收链路的原型验证为例,通过矢量信号发生器和综合测试仪模拟基站功能发送符合TD-LTE协议的射频信号,射频信号经过射频子系统后转换成基带信号进入基带芯片,送入射频接口单元进行定时、滤波、降采样、去CP等处理,在OR1200的控制下将结果送入接收部分的DSP核中进行同步、解调等操作,在硬件加速器中实现信道译码操作,译码后的数据回传给PC,在PC中实现物理特性和协议特性分析。这样就可以分析出下行接收链路所涉及模块及系统的工作状态,获得系统级验证所需的验证结果。

5 结 论

文中以一款基于0R1200的基带芯片为例,详细阐述了FPGA原型验证的方法,包括硬件平台的设计、环境的搭建以及验证的具体实现。原型验证硬件平台容量大,可重用性好;验证环境搭建时,充分利用脚本语言的优势,实现了编译仿真与综合实现的自动化。整个原型验证系统灵活性好,一致性高且便于操作,有效地减少了验证时间,提高了流片成功率。

[1]张术利,刘忻.基于FPGA的SoC原型验证的设计与实现[J].电子技术,2011(5):71-73.

ZHANG Shul-i,LIU Xin.The design and implementation of the FPGA based SoC prototyping verification[J].Electronic Technology,2011(5):71-73.

[2]杨安生,黄世震.基于ARM SoC的FPGA原型验证[J].电子器件,2011,34(3):247-251.

YANG An-sheng,HUANG Shi-zhen.The FPGA prototyping verification of SoC based on ARM[J].Chinese Journal of Electron Devices,2011,34(3):247-251.

[3]ARMLtd.AMBA AXI Protocol Rev1.0.[S].ARMIHI 0011A—2003.2004.

[4]刘韬,楼兴华.FPGA数字电子系统设计与开发实例导航[M].北京:人民邮电出版社,2005.

[5]Thomas L,Anderson.Design intentsraise verification level[M].Electronic Engineering Times,2001.

[6]李哲,田泽,杨峰,等.基于AFDX网络终端系统SoC的FPGA原型验证[J].航空计算技术,2010,40(2):130-134.

LIZhe,TIAN Ze,YANG Feng,etal.FPGA prototype verification based on AFDX network end-system SoC[J].Aeronautical Computing Technique,2010,40(2):130-134.

[7]石芳,郑文松.脉宽调制芯片在高压发生电路中的应用[J].火箭推进,2012(1):68-71,75.

SHI Fang,ZHENG Wen-song.Application of pulse-width modulation chip in high-voltage generating circuit[J].Journal of Rocket Propulsion,2012(1):68-71,75.

The research of FPGA based SoC prototyping verification method

FENG Ling-xiao,ZHANG Bing

(The School of Electronic Information,Jiangsu University of Science and Technology ,Zhenjiang 212003, China)

In a variety of verification methods for SoC design,FPGA-based prototyping verification is relatively close to the actual chips,which can greatly reduce the failure rate of the tape-out and improve the efficiency and comprehensiveness of verification.This article focus on the analysis of the OR1200-based TD-LTE baseband processor,mainly describes FPGA-based prototyping verification method from the aspects of design of hardware verification platform,construction of verification environment, and the implementation of prototyping verification.Meanwhile, the article presents some solutions for the practical project in prototyping verification.

SoC;FPGA;prototyping verification;verification method

10.14022/j.cnki.dzsjgc.2014.16.014

TN492

A

1674-6236(2014)16-0044-04

2013-04-19 稿件编号:201304067

冯凌霄(1989—),男,江苏溧阳人,硕士研究生。研究方向:数字电路设计与验证。