PECVD在TSV领域的应用

李晶

(沈阳拓荆科技有限公司,沈阳 110179)

PECVD在TSV领域的应用

李晶

(沈阳拓荆科技有限公司,沈阳 110179)

PECVD设备及工艺技术已在半导体前道互连工艺及TSV领域展现了其广阔的应用前景,介绍了拓荆PECVD在TSV领域的应用,展现其良好的工艺表现。

等离子体增强化学气相沉积(PECVD);硅通孔技术(TSV);正硅酸乙酯(TEOS);二氧化硅薄膜(SiO2)

硅通孔技术(TSV,Through-Silicon-Via)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直通孔,实现芯片之间互连的最新技术。与以往常规的IC封装键合和使用凸点叠加的技术不同,TSV能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和低功耗的性能。TSV与常规封装技术有一个明显的不同点,TSV的制作可以集成到制造工艺的不同阶段。在晶圆制造Complementary-Metal-Oxide-Semiconductor(CMOS)或Back-End-of-Line(BEOL)步骤之前完成硅通孔通常被称作Via-first,此时TSV的制作可以在Fab厂前端金属互连之前进行,实现Core-to-Core的连接;在CMOS完成之后再进行TSV的制作,然后完成器件制造和后端的封装被称为Via-middle;而将TSV放在封装生产阶段,通常被称作Via-last,该方案的明显优势是可以不改变现有集成电路流程和设计。

等离子体增强化学气相沉积(PECVD)设备可以在150~400℃下沉积具有良好性能的薄膜材料,而且具有对孔洞结构的优良覆盖率,因此在新近的TSV领域具有广泛的应用性。PECVD技术是通过化学反应的方式,利用等离子能源,在反应器内使气态或蒸汽状态的化学物质在气相或气固界面上经化学反应形成固态沉积物的技术。PECVD通常用于淀积绝缘层,用射频方式产生等离子体。离子的轰击为次生物质提供能量,使之能在较低的温度下就可以在硅片上发生化学反应而形成薄膜沉积,因而可应用于金属布线后的绝缘膜沉积等应用。

1 TSV对PECVD的技术要求

TSV的制作可以集成到制造工艺的不同阶段,因 Interposer(no devices)和 Via-first对介质层沉积温度没有限制,但是对于Via-last,介质层沉积温度需要小于200℃,甚至更低的温度。高温和低温PECVD工艺的开发至关重要。为了提高器件的整体性能,PECVD介质层薄膜需要具有良好的电学性能和机械性能,例如高的击穿电压(Break Down Voltage),低的漏电流 (Leakage Current),良好的界面结合性以及适当的应力等。同时PECVD介质层薄膜还必须具备良好的稳定性。高深宽比 (AR>10:1)孔洞内的覆盖性是对PECVD技术的挑战,这也是TSV对PECVD薄膜的一个重要需求。PECVD设备与其他的薄膜沉积方式(如spin on)相比,薄膜的质量更好,主要体现在薄膜的电性、致密性和成膜成本上,其作为生产型设备具有一定优势。

2 PECVD工艺现状

以下将主要从薄膜性能及其稳定性、TSV孔覆盖性以及薄膜附着性几个方面进行讨论。

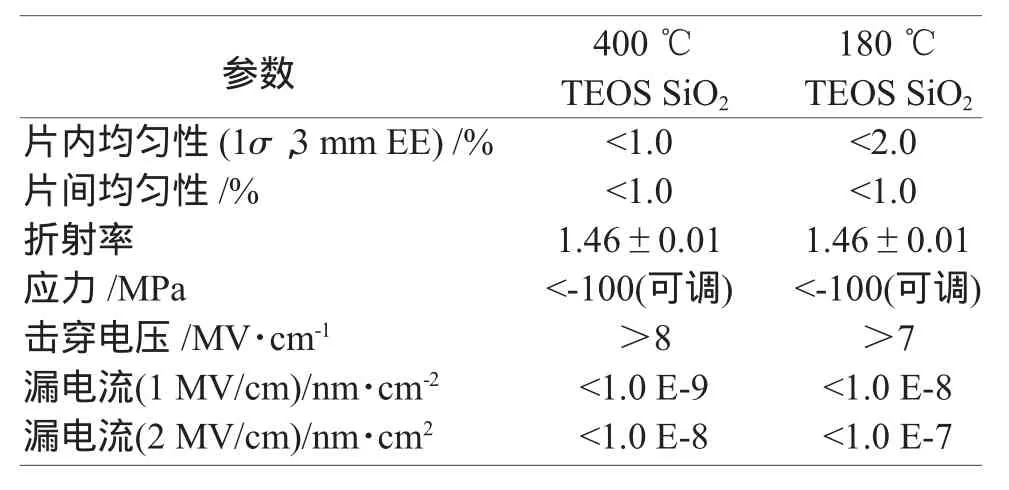

TEOS/O2PECVD薄膜的工艺性能见表1,结果显示PECVD设备在高温和低温下工艺的各项技术指标(膜厚均匀性、薄膜应力、薄膜材料的电性能等)达到TSV领域要求,并且通过了马拉松可靠性验证。

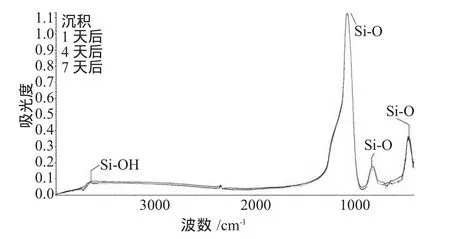

低温PECVD TEOS SiO2薄膜(<200℃)容易具有吸水性,导致吸水后的薄膜电性能会下降,并且会影响与下一层金属层的附着性,所以在低温条件下沉积的薄膜其稳定性至关重要。傅里叶红外光谱(FTIR)利用光干涉技术在红外波段测量材料的吸收光谱。特征波长的吸收峰反映的是材料的分子基团和材料的成分。低温PECVD TEOS SiO2薄膜主要的Si-O峰出现在940~1 080 cm-1范围内,在1 050 cm-1处达到最大。其余的两个Si-O-Si峰出现在816 cm-1和436 cm-1处。对于不稳定的薄膜在Si-OH处有一个明显的峰,并且随时间变化。Si-OH可以通过3 605~3 650 cm-1间的峰和935~941 cm-1间的峰进行检测。通过设备和工艺的优化能够开发出具有良好稳定性的PECVD TEOS SiO2薄膜,克服了其吸水性的缺点。应用FTIR通过对PECVD一周连续的检测,验证其薄膜的化学成分的稳定性,见图1。

表1 TEOS/O2PECVD薄膜的工艺性能

图1 低温PECVD TEOSSiO2薄膜FTIR图谱随时间的变化

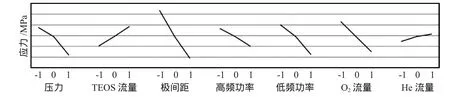

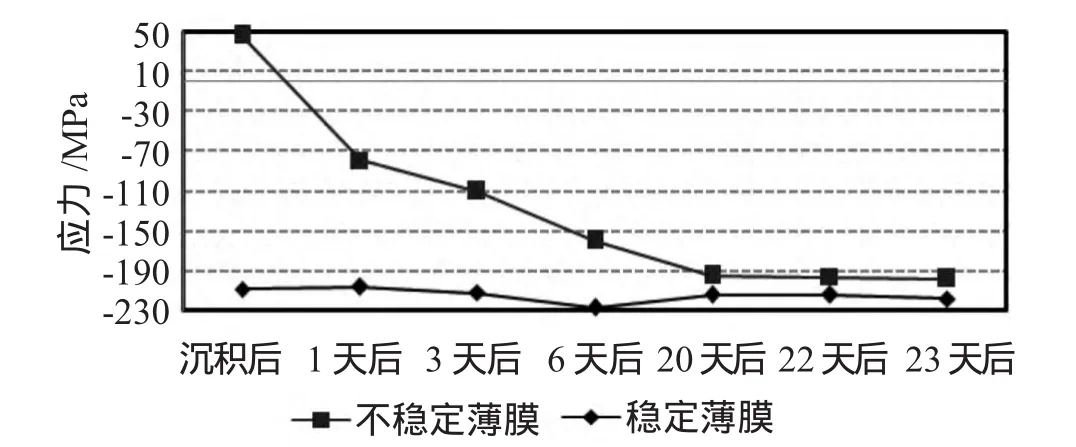

一般来说,各工艺参数间是相互关联的,改变其中的一个参数可能不只影响薄膜的一个性能指标。为了能有效地判断工艺问题,每一次必须只改变一个参数,并对相应的结果以及薄膜特征进行测试,各个工艺参数对薄膜应力的影响见图2,通过控制LF power和gap以及O2流量等可以调整薄膜的应力。通常不稳定薄膜吸水之后其应力值会朝着压应力方向变化,但是通过对工艺的优化可以实现薄膜应力随时间增长保持不变,这也表明了该薄膜具有较好的抗水性,图3显示了低温PECVD TEOS SiO2薄膜应力稳定性。值得注意的是,提高薄膜的某一个性能可能会对薄膜的其他性能产生影响。因此,需要调整各个工艺参数来优化总体性能。

图2 各工艺参数对薄膜应力的影响

图3 低温PECVD TEOS SiO2薄膜应力稳定性监测

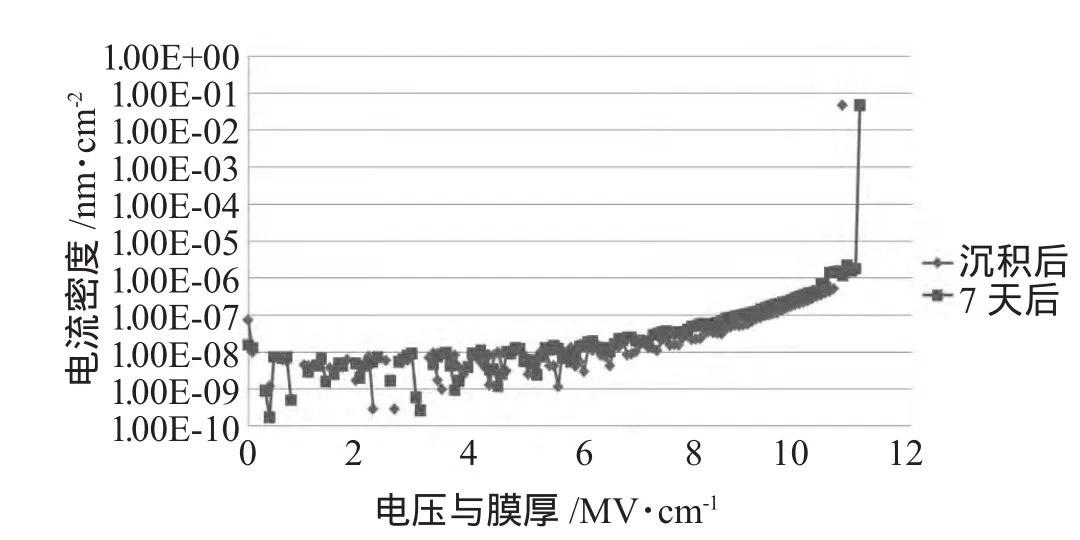

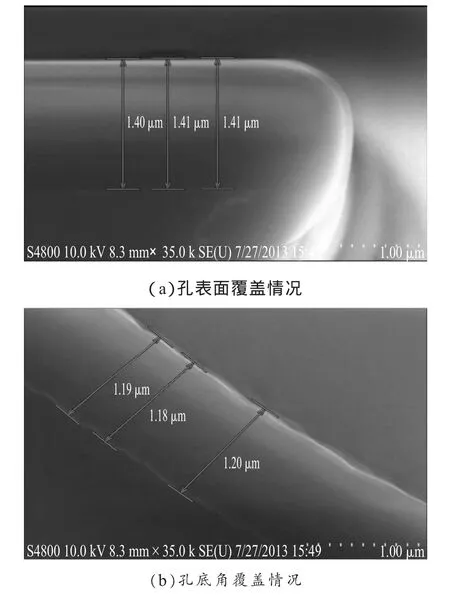

优化后的低温PECVD TEOS SiO2薄膜的电学性能到达TSV领域的要求,其击穿电压(Break Down Voltage)大于10 MV/cm,漏电流(Leakage Current)小于 1×10-9A/cm2@1 MV/cm,并且随时间变化保持稳定,见图4。综上所述,即使是低温条件下,通过设备及工艺的优化,低温PECVD SiO2薄膜性能是优异的且具有良好的稳定性。中覆盖性的表现见图5。

图4 低温PE-TEOS SiO2薄膜电性稳定性监测

低温TEOS PECVD薄膜具有优异的覆盖率,满足TSV领域对薄膜覆盖率的要求。不同深宽比的孔径覆盖率表现不同,例如AR1:1孔径的覆盖率能达到75%以上,AR10:1孔径的覆盖率能达到20%以上,低温TEOS PECVD工艺在AR1:1孔径

图5 低温TEOS PECVD工艺覆盖性(AR1:1)

另外使用百格法测试了低温PECVD薄膜的附着性,验证了低温TEOS工艺附着性满足要求。

3 结 论

(1)拓荆公司掌握了PECVD关键技术,能够向客户提供不同的TSV制程所需的PECVD介质层薄膜沉积技术,并能使之达到量产要求。

(2)面对客户特殊的制程需求,拓荆公司能够提供更低温度的(<180℃)PECVD介质层工艺。

(3)拓荆公司的 PECVD设备及工艺已在TSV领域得到其稳定性能验证。

(4)PECVD设备陆续开发的新技术将能应对未来的挑战。

PECVD Applications in TSV

Li Jing

(Piotech Co.,Ltd,Shenyang 110179,China)

Abstract:PECVD equipment and process technology has shown broad applications in the Front-End-of-Line (FEOL)semiconductor manufacturing process.This paper mainly introduces the new application of PECVD in the emerging Through-Silicon-Via (TSV)technology and its good performance.

Keywords:PECVD (Plasma Enhanced Chemical Vapor Deposition);TSV (Through Silicon Via);TEOS;SiO2film

TN305.96

A

1004-4507(2014)07-0006-04

2014-06-24

李晶(1987年生),女,沈阳,中级工程师,2010年毕业于哈尔滨工业大学材料加工专业。现在沈阳拓荆科技有限公司从事PECVD工艺研发工作。