基于FPGA的谐振音叉高速信号采集装置的搭建*

郭占社,韩景轩,樊尚春,李逸伦

(1.北京航空航天大学仪器科学与光电工程学院,北京 100191;2.北京航空航天大学虚拟现实与系统国家重点实验室,北京 100191)

基于FPGA的谐振音叉高速信号采集装置的搭建*

郭占社1,2*,韩景轩1,2,樊尚春1,2,李逸伦1,2

(1.北京航空航天大学仪器科学与光电工程学院,北京 100191;2.北京航空航天大学虚拟现实与系统国家重点实验室,北京 100191)

谐振音叉作为一种重要的谐振敏感元件,其输出信号直接体现了其频率特性,且直接决定了谐振式传感器的性能,所以对谐振音叉输出信号的研究具有重要意义。本文搭建了一套基于FPGA的高速信号采集装置来进行音叉信号的采集和处理。该装置由硬件部分和软件部分组成,其中硬件部分主要包括电荷放大、滤波、电平转换、模数转换、FPGA信号解算单元及串口调试单元等;软件部分则包括下位机软件和上位机软件。为了对装置性能进行测试,本文采用实验室实际的音叉样件进行实验,通过对其输出信号的拾取和信号处理,测得该装置测试精度可达到0.2%。这样的实验结果表明该装置可满足谐振音叉在1 kHz~30 kHz范围内频率特性的测量要求,且性能良好。

传感器信号处理;信号采集;谐振音叉;FPGA;高速;性能测试

在信号测试领域,高速信号处理是一个很核心的范畴,其设计好坏对整个系统的性能有着决定性的影响。在通信、医疗、图像处理、遥感测量、航空航天等方面都有着非常广泛的应用[1-4],如医疗方面对肺功能测试装置的呼吸信号进行处理,或者在温度、压力测量方面,对谐振式传感器的输出信号进行信号处理等。

基于机械谐振技术,以谐振元件作为敏感元件而实现的传感器称为谐振式传感器。其原理为通过检测由被测物理量的变化而引起的敏感元件固有频率的变化来实现测量。由于重复性、分辨力和稳定性等非常优良,因此谐振式传感器成为当今人们研究的焦点。谐振式传感器的核心部分为谐振敏感元件,而谐振音叉作为一类重要的敏感元件,其输出信号直接体现了其频率特性,且直接决定了谐振式传感器的性能,所以对谐振音叉输出信号的研究具有重要意义[5]。本文依据实验室待测试信号对速度和精度要求高的特点,结合现有的高性能数字采集技术,考虑到FPGA器件具有集成度高,速度快,接口丰富,易于调试等优点,设计并制作了基于FPGA的高速信号采集装置,并采用实验室的谐振音叉进行了实验验证,通过对其频率的拾取和信号处理,得到该装置的测试精度为0.2%。此结果证明该高速信号处理装置性能良好。

1 整体设计

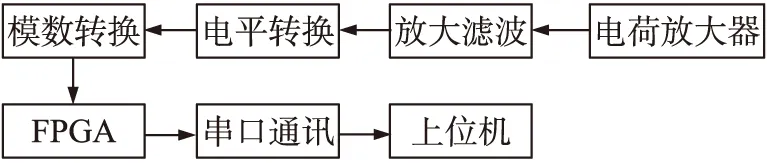

在信号发生器产生频率连续可调的激励信号输入到激励元件,激励元件把电信号转化为作用在谐振音叉梁上的驱动力,使之发生与驱动力同频的振动。拾振元件把这个振动转化为电信号向外输出[6]的前提下,该高速信号采集装置的总体结构和思路是:将振动转化的电信号经过信号变换及调理电路,变为与数模转换芯片输入范围相一致的信号,通过FPGA对信号进行解算并采集至上位机,对信号波形与频率值进行显示。整体设计框图如图1所示。

图1 整体设计框图

2 硬件设计

2.1 模拟前端设计

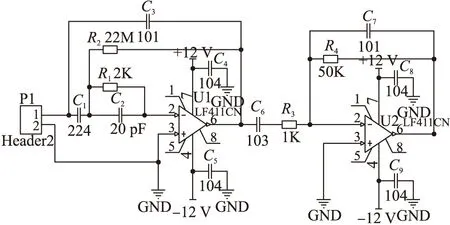

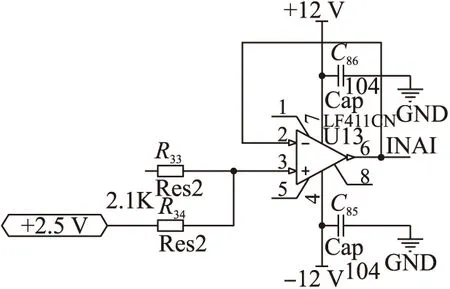

图2 电荷放大器与反相放大电路

由于实验时采用的音叉元件采用压电激励与压电拾振方式,而压电元件要求负载电阻(即前置放大器的输入电阻)也要有足够高的阻抗,以防止电荷迅速泄漏而引入测量误差,据此设计了电荷放大器。而后又搭建了闭环增益为50倍的反相放大电路,以形成截止频率为31.8 kHz的低通滤波,增加电路稳定性。电荷放大器与反向放大电路图如图2所示。

同时由于实验音叉样件固定于实验台上,其感应空间中的50 Hz工频电磁场,产生了比压电元件输出信号大两个数量级的工频干扰。为此设计了如图3的双T形50 Hz陷波器。

图3 双T型50 Hz陷波电路

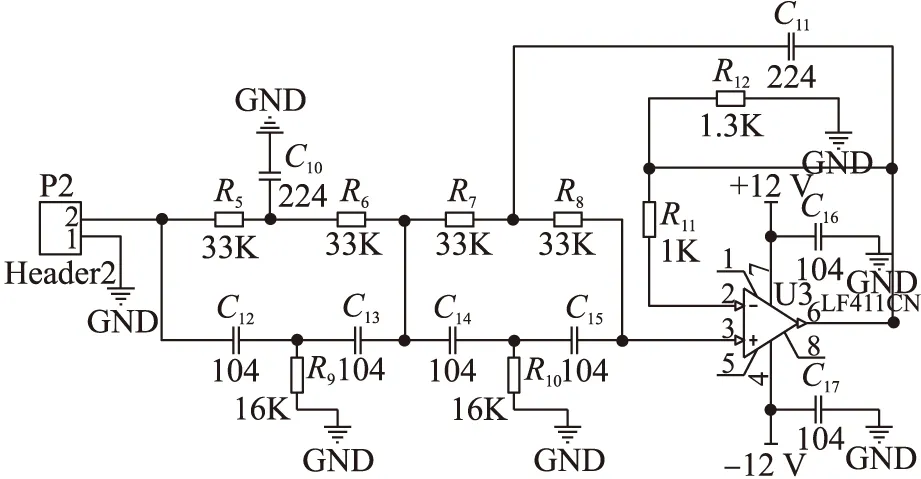

当激励信号为1 kHz~30 kHz的正弦波,振幅为200 mV时,经过电荷放大器、反相放大器以及50 Hz陷波器后的信号在谐振频率点时最大振幅可达到10 V左右,而AD转换芯片只能对0到5 V之间的信号进行采集,这样就必须将信号的振幅调整到0到5 V之间,并能较好的利用A/D转换芯片的采集范围,图4为电平转换电路。

图4 电平转换电路

2.2 数字电路设计

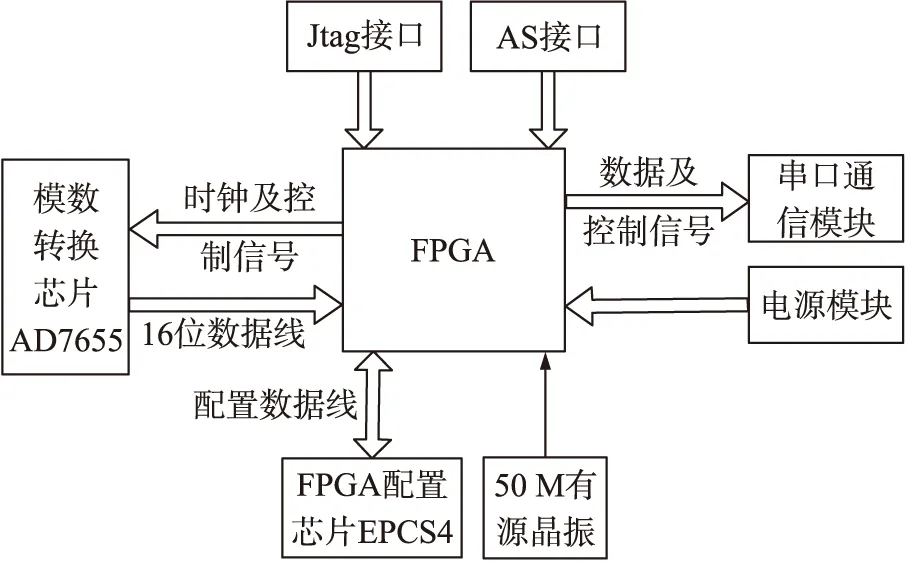

该高速信号采集系统设计框架图如图5所示。主要包括A/D模块设计、FPGA模块设计与串口模块设计三个部分。

图5 数字电路设计框图

根据本系统的技术指标要求,A/D转换器应至少实现2路信号同步采样,且A/D转换器的分辨率应不少于12 bit,每通道的采样频率应不小于100 kHz。通过比较各种型号的A/D转换器,最后选择了低成本、4路、16位、1MSPS的A/D转换器AD7655作为A/D转换芯片[7]。FPGA的选用上采用了Altera公司的Cyclone Ⅱ系列低成本的EP2C8Q208C8N,并用EPC4进行配置,系统编程后,调入JTAG配置指令来对EP2C8Q208C8N进行初始化。在串口模块中使用MAX3232进行电平转换,实现与上位机的通讯。

3 系统软件设计

3.1 下位机软件设计

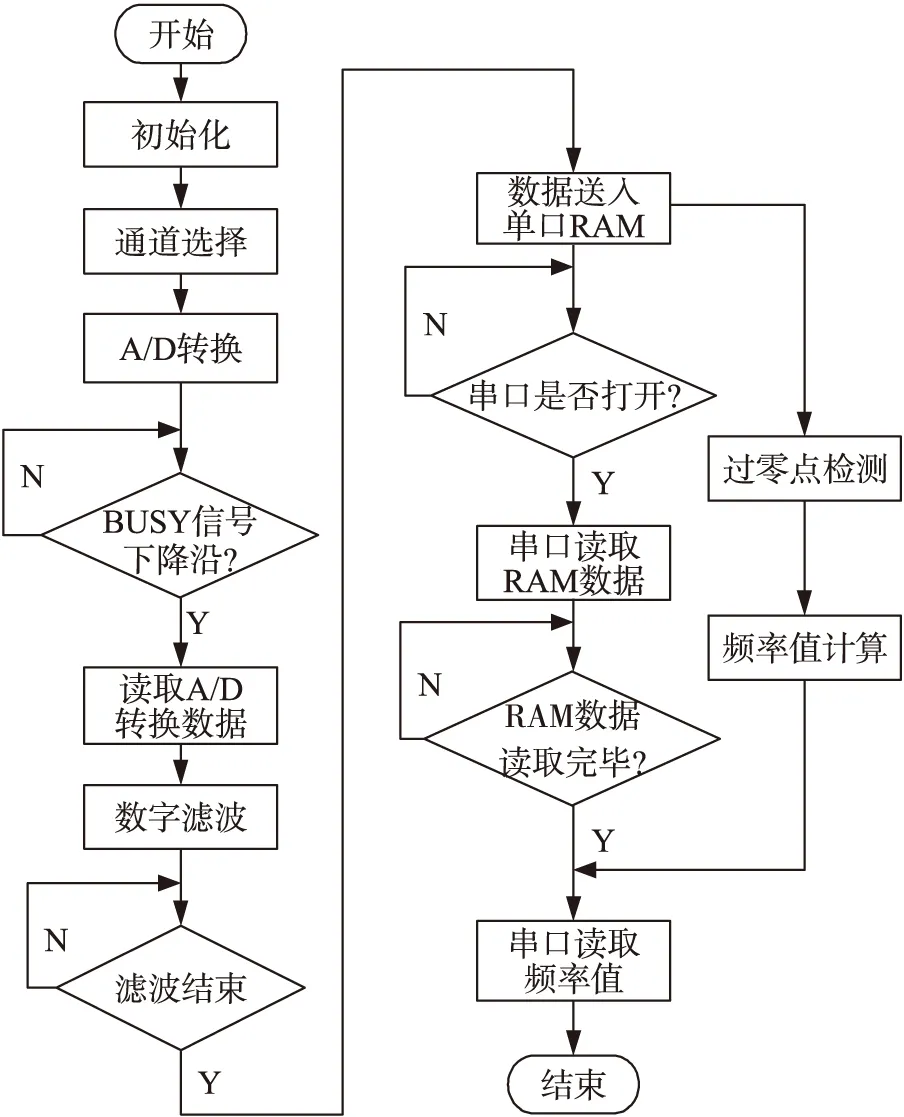

下位机软件设计主要实现五个部分的功能,包括A/D转换模块设计、FIR数字滤波器设计、RAM模块设计、频率检测与串口通讯设计。程序设计流程图如图6所示。

图6 下位机程序设计流程图

3.1.1 A/D转换模块设计

3.1.2 FIR数字滤波器与RAM模块设计

由于用示波器观察A/D前端信号波形仍存在高于30 kHz的高频噪声,为得到更为平滑、准确的信号,采用内部的IP核搭建截止频率为30 kHz的32阶低通滤波器,IP核是用VHDL等硬件描述语言描述的功能块,使设计FIR滤波器的周期比传统设计方法少了很多。经FIR滤波处理后的信号由于频率较高串口不能满足采样要求,这里需将数据先存入RAM中。而在读取RAM内部数据时读取时钟需满足采样定律,不能高于串口的发送频率[9-10],否则会导致数据丢失。

3.1.3 频率检测与串口通讯设计

由于在测量过程中,当有外力作用于音叉系统时,会造成音叉谐振频率的改变,需对频率的改变进行实时检测,从而获得音叉系统频率特性的变化趋势。传统的检测方法是检测一段时间内时间变化的均值,结果存在一定误差,且要求A/D的采样根据信号频率变化而改变,硬件上不易实现,本系统采用过零点检测的方法,对波形零点附近的数据作曲线拟合,由相邻两个过零点的时间差即可计算得到信号频率[11]。

串口模块直接对RAM内部数据与频率值进行读取,并发送至上位机进行显示。为使上位机能快速对数据进行读取,这里串口波特率设为115 200 bps。

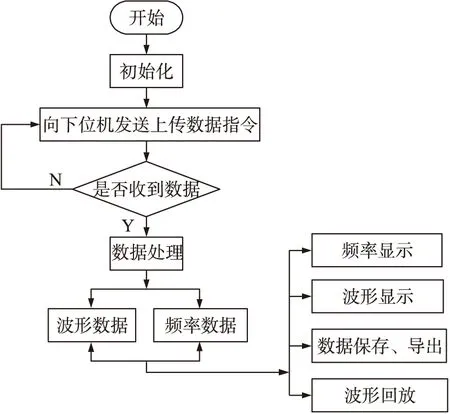

3.2 上位机软件设计

为实现对信号的波形与频率值的显示与数据的存储,能更直观的对音叉的频率特性进行测试,需要设计上位机软件来满足此需求,这里采用VC++6.0的MFC界面实现[12]。上位机程序流程图如图7所示。

图7 上位机程序流程图

4 实验验证

用制作好的信号采集装置进行对谐振音叉的频率进行信号采集。将谐振音叉放置于单轴转台T-450上,以减小外界振动对音叉频率特性的影响。实验装置的实物图如图8所示。

图8 实验装置实物图

将实际音叉样件接入测试电路,调节信号发生器输出频率进行扫频,扫频范围从1 kHz到30 kHz,振幅为180 mV。用示波器观察A/D前端输入波形,测得实验音叉样件的一阶谐振频率为7.8 kHz,用上位机MFC界面对经FIR滤波后的信号进行采集与显示,得到音叉测试样件的一阶谐振频率为7.80 996 kHz,其相对误差为0.128%。显示界面如图9所示。

图9 上位机界面

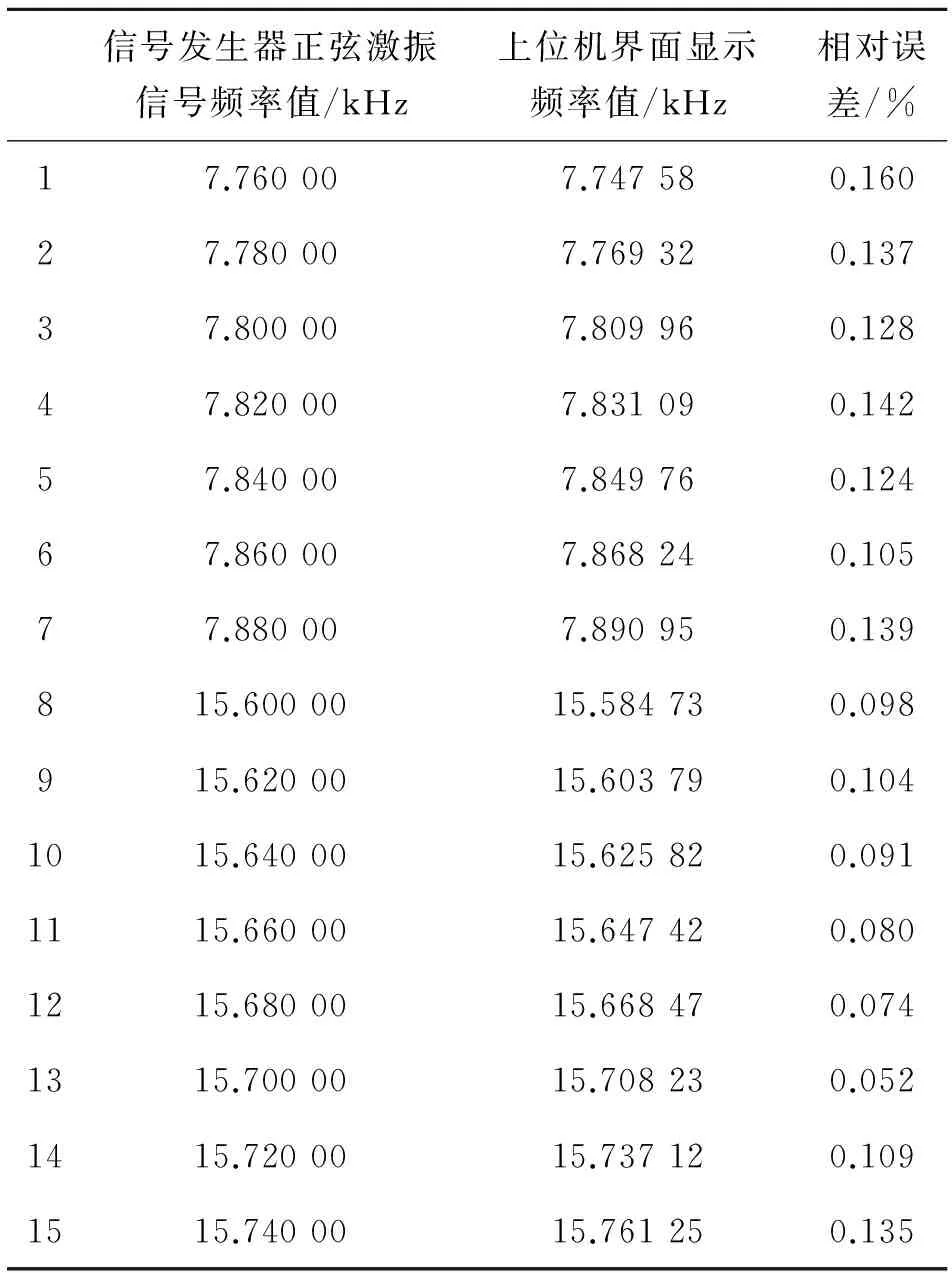

而后又对实验音叉样件的二阶谐振频率进行测量,测得上位机界面显示频率与示波器所测A/D前端输入波形频率相对误差为0.13%。经过多次反复测量,实验装置最大相对误差不超过0.2%。具体测量结果如表1所示,表中详细记录了信号发生器正弦激振信号频率值和上位机界面显示频率值还有它们的相对误差,实验结果表明扫频信号能被完整采样,且精度较高,能够达到预期效果。

表1 实验测试结果

5 结束语

①以FPGA为核心器件搭建的谐振音叉高速信号采集装置,易于实现有效控制与检测计算,提高了系统的响应速度。②充分利用集成的IP软核,缩短了设计周期,可得到更为平滑、准确的信号。

[1] 沈姗姗. 宽带雷达高速信号采集及其一维成像和特征提取[D]. 南京:南京理工大学,13-24.

[2]徐瑞,韩海生,金天弘. 基于DSP的生物医学信号高速实时数据采集与处理系统[J]. 医疗卫生设备,2007,28(2):21-23.

[3]Hsuan-chun Liao,Mochamad Asri,Tsuyoshi Isshiki. A High Level Design of Reconfigurable and High-Performance ASIP Engine for Image Signal Processing[J]. IEICE Transations on Fundamentals of Electronics Communications and Computer Sciences E SERIES A;2012,95(12):2373-2383.

[4]杨东军,方伟,叶新. 太阳辐射监测仪遥测信号采集系统设计[J]. 计算机测量与控制,2009,17(9):1851-1853.

[5]何孟珂,周浩敏,郝欣. 基于FPGA的硅谐振压力微传感器数字闭环系统设计[J]. 现代电子技术,2008,32(13):150-153.

[6]樊尚春,刘广玉. 新型传感技术及应用[M]. 北京:中国电力出版社,2005.

[7]AD7655 Datasheet,Analog Devices Inc,2004.

[8]樊尚春,孙苗苗. 一种基于谐振音叉的新型差动式硅微加速度计设计与分析[J]. 传感技术学报,2012,25(1):20-24.

[9]许金生,周春雪,赵从毅. 基于IP Core的FIR数字滤波器的FPGA实现[J]. 安徽工业大学学报,2007,24(3):309-313.

[10]唐博,李锦明,李士照. 基于FPGA的高阶FIR滤波器强抗干扰数据采集系统[J]. 电子技术应用,2012,38(19):89-92.

[11]盛辉. 基于FPGA的高速频率计设计[J]. 硅谷,2013(2):93.

[12]电容式微加速度传感器信号处理电路的设计[J]. 传感技术学报,2006,19(5):2090-2196.

郭占社(1973-),男,河北邯郸人,汉族,博士后,硕士研究生导师、副教授,主要研究方向为微机电系统,先进传感技术和微机电器件和建模仿真技术等领域,guozhanshe@buaa.edu.cn;

韩景轩(1990-),女,河北霸州人,汉族,在读硕士,主要研究方向为信号处理。

ConstructionoftheHigh-speedSignalAcquisitionDeviceofResonantTuningForkbasedonFPGA*

GUOZhanshe1,2*,HANJingxuan1,2,FANShangchun1,2,LIYilun1,2

(1.School of Instrument Science and Opto-electronics Engineering of Beihang University,Beijing,100191,China;2.State Key Laboratory of Virtual Reality and systems of Beihang University,Beijing,100191)

As one of the important resonant sensitive elements,the output signal of the resonant tuning fork can directly reflect the frequency characteristic and directly determine the performance of the resonant sensor. Therefore,research on the frequency characteristic of the resonant tuning fork is of great significance. In this paper,a high-speed signal acquisition device based on FPGA is built. The hardware and software design methods of the device are introduced in detail. Among this,the hardware part includes charge amplification,filtering,level conversion,analog to digital conversion,signal solver unit based on FPGA,and serial debug unit,the software part includes lower machine software and PC software. At last,the actual sample is used to test the performance of the device. The measuring accuracy of the device can reach 0.2% through experiments. In conclusion,the results show that this device can satisfy the frequency test requirement in the range of 1 kHz to 30 kHz,and it works very well.

the resonant tuning fork;signal acquisition;FPGA;high-speed;performance test

项目来源:国家国际科技合作专项资助(2014DFA31230)

2014-07-10修改日期:2014-09-12

10.3969/j.issn.1004-1699.2014.11.010

TM932

:A

:1004-1699(2014)11-1495-05