石墨烯晶体管研究进展

李昕,郭士西,宋辉,李全福,师俊杰,方明,王小力,刘卫华

(西安交通大学电子与信息工程学院, 710049, 西安)

石墨烯晶体管研究进展

李昕,郭士西,宋辉,李全福,师俊杰,方明,王小力,刘卫华

(西安交通大学电子与信息工程学院, 710049, 西安)

针对集成电路的特征尺寸小于10 nm以下所面临的短沟道效应、隧道效应和制造工艺限制困难引发的研究热点——石墨烯能否替代硅,着重从数字晶体管、射频晶体管和柔性透明晶体管3个方面概括和分析了新型石墨烯晶体管的发展现状。分析认为:石墨烯平行纳米带阵列结构和异质结结构有望打开石墨烯禁带以实现大的电流开关比,将是石墨烯数字晶体管的研究热点;通过降低接触电阻、接入电阻以及衬底、栅介质的匹配来提高截止频率和最大振荡频率将是石墨烯射频晶体管的主要发展趋势;基于聚对苯二甲酸乙二醇酯(PET)衬底和离子凝胶栅介质的柔性制造技术,最有希望在保证石墨烯高迁移率的基础之上实现全石墨烯透明柔性电路,使石墨烯晶体管得以实用,必将对集成电路行业产生巨大影响。

石墨烯晶体管;禁带;截止频率;最大振荡频率;柔性晶体管

随着后摩尔时代的到来,集成电路制造技术不断改进,极紫外(EUV)光刻的引入,将特征尺寸大幅度减小,下一代硅基集成电路的特征尺寸将达到15 nm,甚至10 nm以下[1]。但是,随之而来的短沟道效应和介质隧穿效应等的影响,以及制造难度的提升,将很难得到特征尺寸小于10 nm的性能稳定的电路产品[1]。所以急需研究开发基于新材料、新结构和新工艺的器件。

英国科学家GEIM等人制备出了仅一个原子厚几纳米宽的石墨烯量子点器件[2],在这种尺度下,石墨烯存在约0.5 eV的禁带宽度,且器件仍然能保持较好的导电性。GEIM预测石墨烯量子点器件的特征尺寸最小可降低到1 nm[2]。此后对新型石墨烯晶体管的研究引起科学界越来越广泛的关注,并被认为是后摩尔时代电子学的最佳候选者[3-4]。

本文将主要从数字晶体管、射频晶体管和柔性透明晶体管3个方面概括和分析石墨烯新型晶体管的发展现状。从如何打开石墨烯禁带以实现大的电流开关比和实现逻辑互补的角度分析其在数字晶体管中主要面临的挑战和机遇;从如何提高截止频率fT和最大振荡频率fMAX的角度来阐述其在射频晶体管中需要解决的主要难题和发展方向;从如何匹配柔性衬底和柔性栅介质的角度论述石墨烯柔性透明晶体管的优势。

1 石墨烯数字晶体管

电子穿过石墨烯几乎没有任何阻力,所产生的热量也非常少。石墨烯具有很高的载流子迁移率和热导率[4],有望在数字逻辑晶体管方面成为硅的替代材料。但是,大面积的石墨烯是一种零禁带材料,以此作为沟道的晶体管很难被关断,电流开关比也很小。此外,为了实现理论上的零静态功耗,需要实现由下拉的n型石墨烯晶体管和上拉的p型石墨烯晶体管构成的石墨烯互补数字逻辑。然而,由于石墨烯的性质非常稳定,对其进行n型、p型掺杂是很困难的,因此对石墨烯数字晶体管方面的研究主要集中在2个方面:一是如何产生禁带以实现高的开关比;二是如何对石墨烯掺杂以构造互补逻辑。

1.1 石墨烯产生禁带的研究

1.1.1 直接产生禁带法 直接产生禁带的方法主要包括构造石墨烯纳米带结构[5]和构造石墨烯纳米带网状结构[6]等。

(1)构造石墨烯纳米带结构。当石墨烯纳米带的宽度小于10 nm时,呈现出半导体特性[5],利用石墨烯纳米带构造的场效应晶体管的电流开关比最高可接近107,并且产生的禁带宽度Eg和石墨烯纳米带宽度d呈现一种反比的关系,它们之间的经验公式为Eg≈0.8/d。石墨烯纳米带禁带的产生是由于量子限域效应和边界效应的原因[7],当材料尺寸达到纳米量级时,费米能级附近的电子态由接近连续的能带分裂成分离能级,从而产生非零禁带。

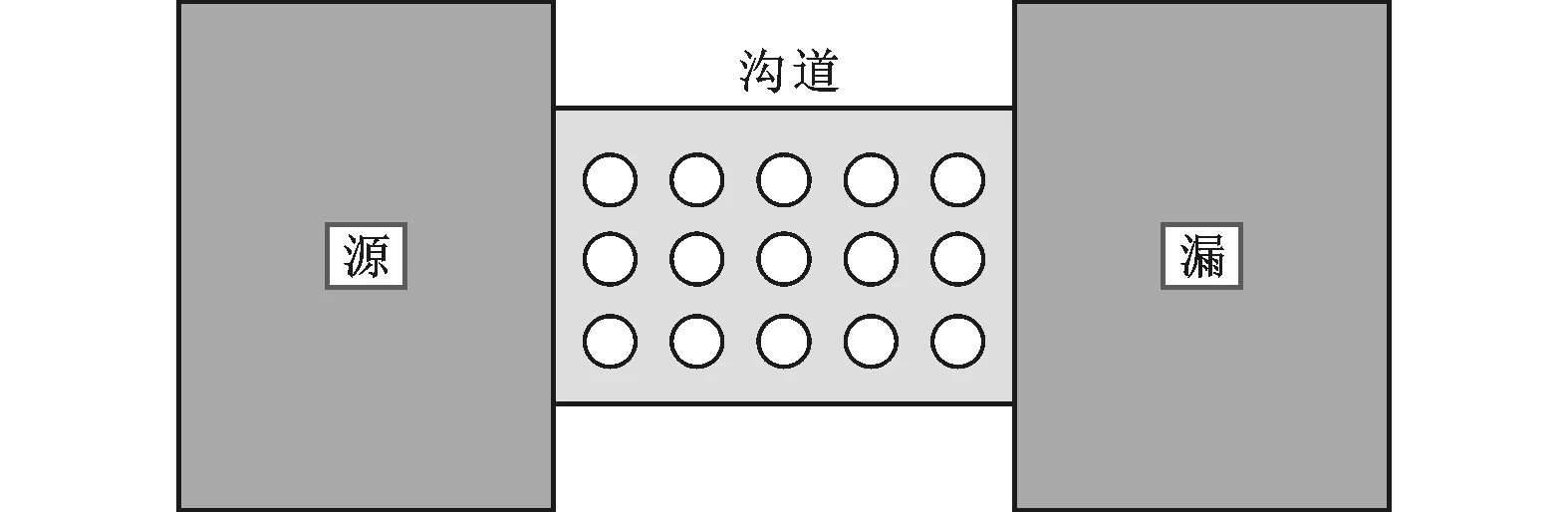

(2)构造石墨烯纳米带网状结构。石墨烯纳米带网状结构和石墨烯纳米带结构的工作原理相似,只是整体宽度更大,其结构相当于石墨烯纳米带和石墨烯组成的一个网状结构,其中最小的尺寸小于10 nm,故具有半导体特性。由于石墨烯纳米带网状结构相对容易获得,因而吸引了许多研究小组的关注。Bai等人利用纳米带网状结构的SiO2作为掩膜版,通过氧等离子体刻蚀,得到了规则排列的石墨烯纳米带网状结构场效应晶体管(FET)[6],如图1所示,并形象地将这种结构分为“孔”和“颈”两种单元,颈宽最小值可达到5 nm。这种石墨烯纳米带网状结构的晶体管的优点是在保证大的电流开关比的前提下能实现大的导通电流,其值大约是石墨烯纳米带晶体管导通电流的100倍。Zeng等人利用阳极氧化铝薄膜作为模板,得到平均颈宽约14.7 nm的石墨烯纳米带网状结构[8]。

图1 石墨烯纳米带网状结构FET示意图

石墨烯纳米带网状结构是继石墨烯纳米带之后最有希望直接用于数字电路的结构。但是,这种结构的载流子散射[9]会比石墨烯纳米带更大,因为在这种结构中,载流子的通路更加弯曲,会阻碍载流子的传输。导通电流更大的原因是因为这种结构能提供更多的载流子沟道。

1.1.2 间接产生禁带法 间接产生禁带的方法主要是通过引入具有非零禁带的物质作为势垒产生禁带,在石墨烯表面和边界上构造异质结,形成异质结晶体管,该方法是目前石墨烯数字晶体管新的研究热点。

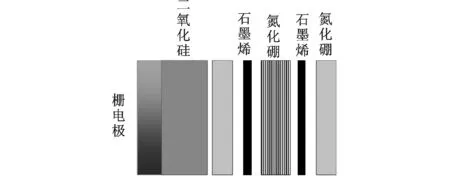

石墨烯异质结晶体管一般分为横向异质结[10]和纵向异质结[11-12]。横向异质结是一种平面结构,将石墨烯和具有非零禁带的半导体材料相互接触,间接加入了禁带,如图2a所示。Moon等人将单层石墨烯部分氟化[10],进而得到石墨烯-氟化石墨烯-石墨烯的横向异质结结构,禁带宽度约为2.93 eV,电流开关比提高到106,且具有良好的电流饱和特性,这是一般石墨烯晶体管所不能达到的,只是这种结构产生的导通电流却很小,还有待进一步提高和改进。从二维结构生长角度来研究,Liu等人获得了氮化硼-石墨烯-氮化硼[13]平面异质结结构,并可以制作出各种形状的图案,具有制备横向异质结晶体管的潜力。

纵向异质结是一种堆叠式的结构,层层相叠,如图2b所示。Britnell等人首先提出了将这种结构用于石墨烯晶体管,分别用几个原子层厚的氮化硼和二硫化钼作为中间势垒层,通过隧穿效应实现了约50和104的电流开关比[11],开关比相差较大是由于这2种材料禁带宽度差别大所致。随后,Georgiou等人对这种结构进行了改进,将氮化硼换成了二硫化钨,由于二硫化钨禁带小,可以利用隧穿效应和热电子激发2种机理[12],实现了最大可达106的电流开关比。

(a)氮化硼/石墨烯横向异质结形成示意图

(b)石墨烯垂直异质结示意图

(c)受栅压和正栅压影响的石墨烯垂直异质结能带结构示意图

对比2种晶体管发现,横向异质结晶体管电流相对较小,但饱和性较好,纵向异质结晶体管则电流相对较大,并且通过利用不同材料匹配可以得到更大的输出范围,但是饱和性并不好。这2种结构都需要在材料和结构上寻找最优参数。

1.2 构造互补逻辑-掺杂

为了实现理论上的零静态功耗,石墨烯晶体管需要实现n管、p管的区分,构成互补逻辑。但是,单层石墨烯的性质非常稳定,对其进行n型、p型掺杂是很困难的。下面分别从n型掺杂和p型掺杂2个角度分析相关研究进展。

n型替换掺杂方法是先在石墨烯表面通过离子辐照产生缺陷,然后在NH3气体中退火[14],引入n型杂质。Wang等人在NH3中通过电热反应,在石墨烯的边缘部分和缺陷部分产生n型杂质[15]。这2种方法都是利用N原子替代C原子产生的掺杂。此外,衬底诱导掺杂[16]也是一种比较简便的n型掺杂方式。

p型替换掺杂可以用B原子直接取代C原子来实现。前人利用反应微波等离子[17]的方法实现了对石墨烯的p型掺杂,将石墨烯放在等离子体增强化学气相淀积的腔室内,与低能微波等离子体分解的三甲基硼离子气体反应即可得到p型掺杂的石墨烯。通过电狐放电[18]的方法也可以实现对石墨烯的p型替换掺杂。目前采取表面吸附的形式来实现p型掺杂是更常见的方法。石墨烯在常温常压下具有弱的p型导电特性[16],这是由于吸附空气中H2O的缘故,有利于石墨烯的p型掺杂。

总体而言,空气中的石墨烯具有p型特性,如果不进行掺杂,只能得到p型晶体管。利用替换C原子的方法实现n型、p型掺杂都比较难以实现,并且对石墨烯还可能造成损伤。同时,从B—C键和N—C键的键能强度值来看,p型掺杂比n型掺杂相对容易实现[17-18]。

1.3 石墨烯数字晶体管展望

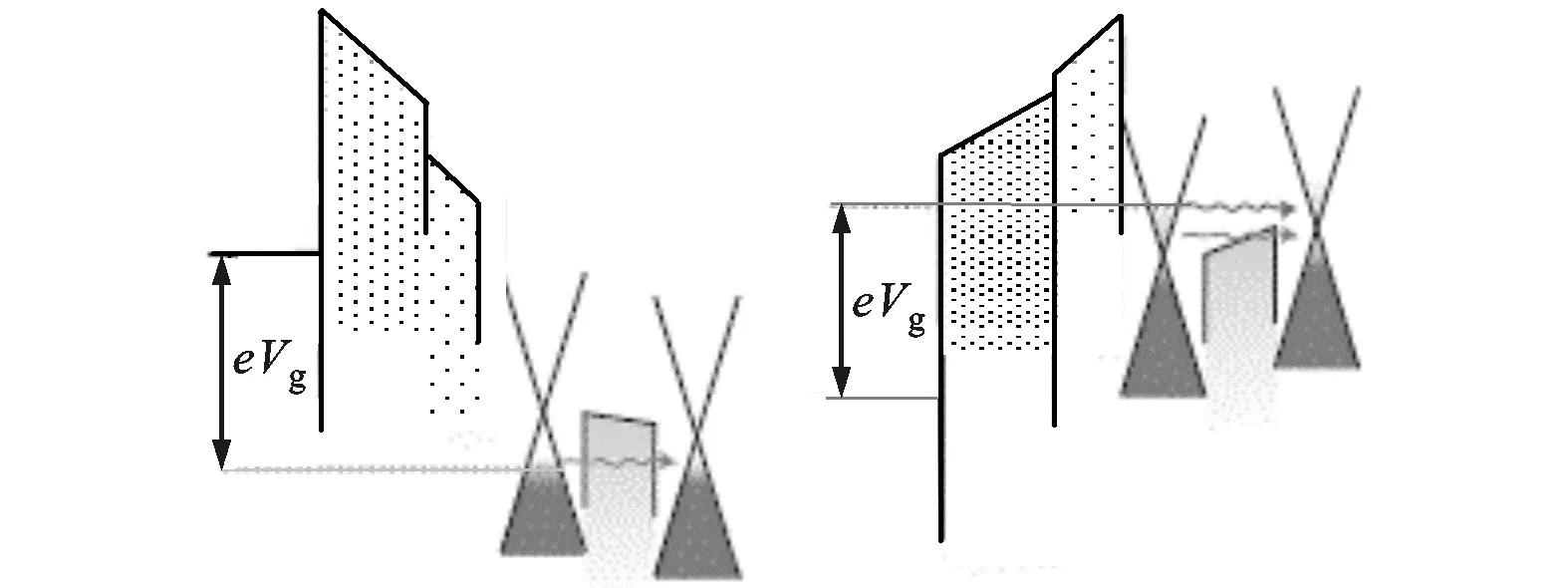

石墨烯纳米带结构或者石墨烯异质结结构,都可以实现具有禁带的石墨烯晶体管。对于石墨烯纳米带而言,由于高迁移率的特性受到严重限制,并且对其操控非常困难,因此需要找到一种可控的、能产生光滑边缘的制备方法。在改进制备方法的条件下,本文认为石墨烯平行纳米带阵列结构应该是比较具有潜力的一种结构,其结构示意图如图3所示。图中两边为电极区,中间为沟道区,这种结构不仅能够提供更多的沟道,而且与石墨烯纳米带网络结构相比能抑制散射,有望具有高的开关比和导通电流。

图3 石墨烯纳米带阵列结构示意图

异质结结构是近年兴起的一种方法,对石墨烯晶体管的发展起到了积极的推动作用。虽然要制造出与石墨烯晶格匹配的介质材料如氮化硼等目前还有很大的挑战,但是纵向异质结结构有望构造隧道晶体管,实现高的开关比,是一个很有前途的方向。

石墨烯的掺杂工艺同样面临着很大的挑战,原子替换掺杂和吸附掺杂是目前2种主要的掺杂方法。替换掺杂比较困难并且容易破坏石墨烯晶格,产生缺陷,吸附掺杂相对容易,但是不太稳定,这就需要科研人员继续努力来寻找更加简便实用的掺杂方法,既不对石墨烯自身造成影响,又能稳定存在,并且比较容易实现。

总体而言,石墨烯数字晶体管距离实际应用还有很长的路要走,电流开关比和互补特性只是2个最基本的要求。在满足这2个基本的条件下,还要分析评价其数字电路的其他指标,例如亚阈值特性、短沟道效应、集成度以及功耗等。

2 石墨烯射频晶体管

在射频电路领域,石墨烯晶体管已经被设计应用在电子倍频器、移相键控调制器和混频器[18]等具有射频概念的电路中。将石墨烯晶体管用于射频电路,要求其具有高频工作特性,即具有高的载流子迁移率、低的接触电阻和接入电阻(未被栅覆盖的电极),同时最好具有电流饱和特性,因为只有在饱和区晶体管的本征增益才会比较大。下面首先对射频电路中各个主要影响因素进行分析,然后根据由此引发的研究关注热点进行介绍和分析。

2.1 石墨烯晶体管特征频率影响因素分析

石墨烯射频晶体管主要有2个重要的频率指标:截止频率fT和最大振荡频率fMAX。随着频率上升,电流增益会下降。截止频率fT和最大振荡频率fMAX的表达式如式(1)、式(2)所示,根据公式中的各个参数,就可以得到提高截止频率和最大振荡频率的办法。

(1)

(2)

式中:gm为跨导;CG为栅电容;gD为沟道电导;RSD和RG为源漏串联电阻和栅电阻。

根据式(1),提高跨导gm、减小栅电容CG,可以提高截止频率;根据式(2),减小沟道电导gD、源漏串联电阻RSD、栅电阻RG和栅电容CG可以提高最大振荡频率fMAX。综合这2个公式,可以得到提高截止频率和最大振荡频率的方法,其一是提高跨导gm、减小沟道电导gD,这就要求电路尽可能工作在饱和区;其二是减小源漏串联电阻RSD,而串联电阻包括接触电阻、沟道电阻和接入电阻3部分,其中石墨烯沟道电阻一般比较小,且可以由栅极调控。但是,石墨烯与电极之间的接触电阻RC比较大,同时未被栅电极覆盖的接入电阻RA也比较大,RC和RA有很大的改善空间,是目前的研究热点。

2.2 提高石墨烯晶体管频率特性的研究进展

目前针对石墨烯晶体管的研究围绕着提高截止频率fT和最大振荡频率fMAX两方面进行,以下从减小石墨烯与金属电极的接触电阻、减小接入电阻(未被栅极覆盖的沟道电阻)、提高载流子迁移率以及石墨烯晶体管漏电流的饱和特性等几个方面进行分析。

2.2.1 减小石墨烯与电极的接触电阻 减小接触电阻是石墨烯晶体管在数字电路和射频电路应用中都要面临的问题。在数字电路方面,接触电阻的大小对石墨烯晶体管电流开关比有着重要影响,接触电阻越大,则电流开关比越小。在模拟电路中,接触电阻对石墨烯晶体管的跨导、截止频率和最大振荡频率都有很大的影响,因为增大接触电阻RC,会减小漏电流ID,导致跨导gm减小,随之引起截止频率fT、最大振荡频率fMAX也会减小,器件性能受到限制,所以就必须减小接触电阻。目前报道的减小接触电阻的方法主要包括金属和石墨烯边缘接触[19]、紫外臭氧处理[20]、退火处理等。其中,边缘接触是指尽可能让石墨烯边缘的悬挂键和金属产生接触,如图4a所示,被称为end/edge-contacted,利用石墨烯边缘悬挂键与金属原子实现共价键结合,获得稳定的接触效果。与此相对应的是面接触,主要让石墨烯的上下表面与金属电极表面接触,如图4b所示,被称为side/top-contacted。前人通过仿真计算发现边缘接触end-contacted比上下表面接触side-contacted的接触电阻小得多[21],这是由于石墨烯的上下表面结构完整,无缺陷和悬挂键,与金属界面之间主要是静电吸附,结合力较弱。当接触金属分别为Au、Cu、Pt、Pd和Ti时,end-contacted的接触电阻比side-contacted的接触电阻分别减小了6 571、2 488、233、60和8.8倍。为了制造更多的边缘结构而将石墨烯切成很多细条[22],如图5a所示,对比2种金属电极Cu和Pd,结果发现石墨烯与Cu和Pd的接触电阻分别降低了22%和32%。Wang小组利用三明治结构夹持石墨烯,再进行端面切割,之后在石墨烯端部制造电极,实现了石墨烯边缘和金属电极之间的原子级接触[19],如图5b所示,其中接触电阻最小达到100 Ω·μm。

(a)石墨烯和金属边缘接触 (b)石墨烯和金属面接触

(a)切割石墨烯表面增加边缘长度的器件结构示意图

(b)实现石墨烯边缘和金属电极原子级接触示意图

2.2.2 减小石墨烯晶体管的接入电阻 减小接入电阻是石墨烯射频电路研究比较多的一个方面,减小接入电阻的办法主要是对未被栅极覆盖到的区域电阻进行处理,涉及的工艺处理方式包括自对准法[23]、掺杂法[24]以及引入电场调控[25]等方法。自对准工艺法是直接通过结构设计和工艺优化来减小未被栅极覆盖的沟道长度,从而减小接入电阻,如图6a、6b所示。图6a是通过先加工源漏后加工栅极的自对准工艺[23],实现了沟长LG=3 μm时,截止频率13 GHz的效果。图6b是利用Co2Si纳米线[26]作为栅极,通过自对准工艺就可以实现沟道全覆盖,并且沟道长度可以做得很小,实现了高频和高速度[37]双重效果,最高截止频率fT可以达到300 GHz。掺杂法是通过掺杂工艺改变被掺杂区的阻值来减小接入电阻,如图6c所示。加电极调控法是通过对没有被栅极覆盖区施加电场,依据其不同导电类型,相应减小接入电阻来提高截止频率,如图6d所示。这些方法都是通过减小接入电阻,从而减小源漏串联电阻RSD,进而增大跨导gm、提高截止频率fT和最大振荡频率fMAX。

(a)优化结构的自对准法示意图

(b)纳米线栅的自对准法示意图

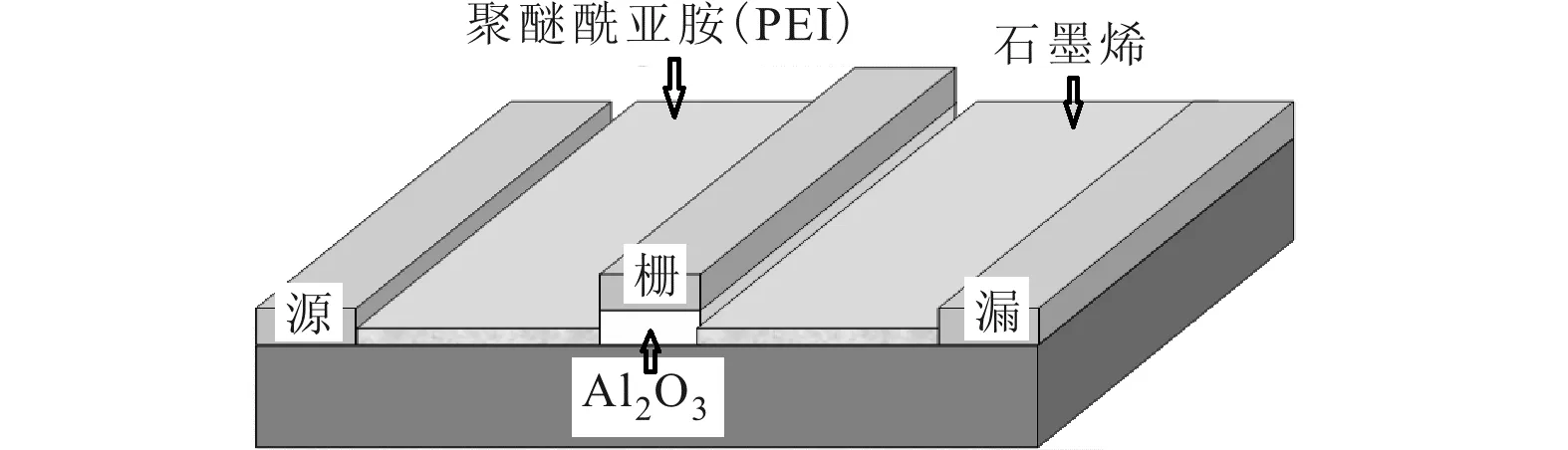

(c)聚合物掺杂法示意图

(d)局部施加电场法示意图

2.2.3 提高石墨烯射频晶体管性能的其他尝试 提高石墨烯射频晶体管性能的其他方法如提高载流子迁移率和电流饱和特性,也是非常重要的。石墨烯本身就具有很高的载流子迁移率,受栅介质层、衬底[27]和光刻胶杂质[9]等的影响,载流子迁移率受到很大的束缚。提高载流子迁移率的做法就是将杂质去除掉,并且选择比较光滑的衬底,如氮化硼(BN)[19,27]等。BN和石墨烯具有相似的结构,被称为白色石墨,具有原子级光滑的平面,有利于提高载流子的迁移率。电流饱和特性是石墨烯射频电路必需具备的,电流饱和时,跨导比较大,沟道电导比较小,这样就可以得到比较大的本征增益,但是实验测试的石墨烯器件没有明显的电流饱和特性,需要继续对其原因和改善办法做出进一步的研究。

2.3 石墨烯射频晶体管展望

石墨烯射频晶体管相对于数字晶体管而言具有更大的优势,因为射频晶体管工作在导通区域。目前对石墨烯射频晶体管的研究较为顺利,从其截止频率fT(如图7所示[3])可以看出,石墨烯射频晶体管高频特性能够与硅相媲美,充分说明了石墨烯射频晶体管的应用潜力。为了进一步提高其射频性能,下一步的研究思路应该是,减小石墨烯和金属的接触电阻、石墨烯射频晶体管的接入电阻,以及选择匹配的衬底和栅介质来提高石墨烯载流子迁移率。

图7 不同类型晶体管在不同栅长时的截止频率对比图

3 石墨烯柔性透明晶体管

单原子层的石墨烯具有优异的柔性和透光率[28-29],与传统器件相比,石墨烯柔性透明薄膜晶体管(TFT)加工方法简单、成本低,在柔性透明电子学方面将具有很大的潜力。以下将首先对石墨烯柔性器件的稳定性进行分析,然后论述石墨烯用作柔性器件应该考虑的问题,最后对基于石墨烯的柔性透明薄膜晶体管进行举例说明。

3.1 石墨烯柔性透明器件的稳定性分析

石墨烯柔性器件必须接受各种形变的考验才能正式应用于柔性器件。同透明电路中常用的ITO导电薄膜(氧化铟锡透明电极)相比,石墨烯能承受更大的应变,如图8所示[28],ITO在应变3%时,电阻变化已经比较明显,而石墨烯在应变6%时电阻保持稳定。同时,其他研究人员还测试了石墨烯迁移率随其弯曲时的变化,结果发现,石墨烯柔性晶体管在弯曲半径为0.6~6 cm时,载流子迁移率的变化在20%以内[30]。以上数据表明,石墨烯可以比较理想地用于柔性器件中。但是,当石墨烯被拉伸或者弯曲到一定程度时,其电学特性也会发生一定的变化。这可以根据扭曲石墨烯纳米带诱导出赝磁场和谷电流理论来解释[31],这一缺陷必将影响石墨烯的电学特性。尽管如此,石墨烯相比常见的柔性材料还是具有很高的稳定性。

图8 石墨烯和ITO的电阻变化率随应变的变化曲线

3.2 石墨烯柔性透明晶体管关键问题

3.2.1 石墨烯用于柔性电极 石墨烯不仅可以作为沟道进行导电,还可以用作柔性或有机晶体管的导电电极。相对于金属电极而言,将石墨烯作为柔性电极具有很多优点。因为石墨烯和有机材料接触时电子具有较低的注入势垒[32],所以石墨烯和有机材料具有更好的结合特性,有利于载流子输运,能增大迁移率。现在工艺已经可以满足大面积的石墨烯薄膜的制备,用于柔性器件的石墨烯电极通常是通过化学气相淀积(CVD)来制备的,通过控制工艺条件可以得到不同厚度的大面积石墨烯薄膜,可用作柔性透明电极材料。

3.2.2 石墨烯柔性晶体管栅介质 对于石墨烯柔性透明晶体管,栅介质的选择很重要。目前较常用的栅介质包括离子凝胶[29]和氧化石墨烯(graphene oxide, GO[28,33]),而不采用硅基器件常见的HfO2或者Al2O3等高k介质的原因:①用于传统衬底的高k介质要在高温下才能生成,柔性衬底承受不了高温,所以这种高k介质不能应用于柔性晶体管;②离子凝胶对电子绝缘,对离子导电,能产生较大电容[33],实现低压工作以及产生较大的导通电流,而氧化石墨烯(GO)的介电常数(室温下为5 F/m)大于二氧化硅的介电常数[29],能实现栅介质的作用;③这2种栅介质制作工艺简单,离子凝胶可以直接通过气溶胶喷射印刷技术[29]来实现,GO只需要在制备并转移石墨烯的基础之上增加了一步氧化工艺。

3.2.3 石墨烯柔性晶体管衬底的选择 对于石墨烯柔性透明晶体管,衬底一般选择柔性的聚合物来实现,例如酞酸乙二酯(PET)衬底[29]。这类衬底相对于二氧化硅等坚硬衬底而言,具有透光性好、弯曲和拉伸的稳定性等优点,但是这种衬底也严重限制了石墨烯沟道的载流子迁移率,这是由于衬底粗糙度比较大,导致对电子散射比较大的原因。利用BN做柔性衬底[12],可以得到性能更好的石墨烯柔性透明晶体管。

3.3 基于石墨烯的柔性透明薄膜晶体管

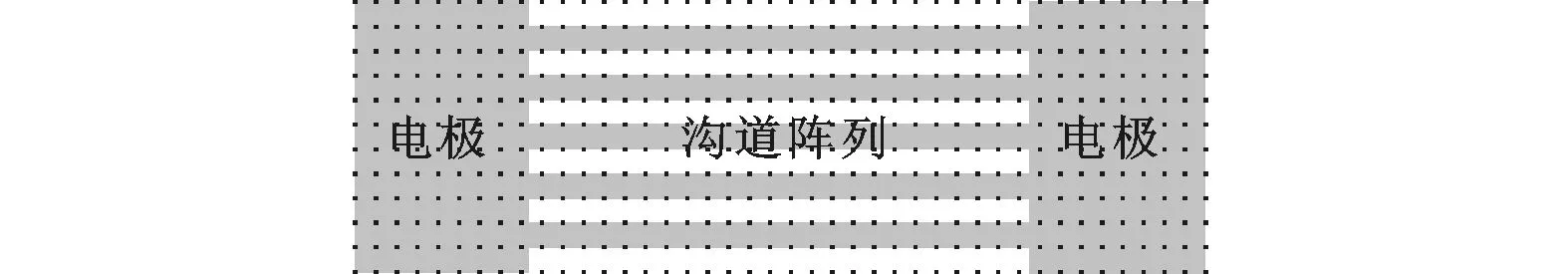

(a)GO为栅介质、石墨烯作为沟道和电极的全石墨烯TFT

(b)用辊压印技术加工的石墨烯TFT阵列

(c)共平面石墨烯TFT阵列

将石墨烯作为沟道和电极,同时将GO作为栅介质,可以形成一种被称为全石墨烯[33]的晶体管电路,如图9a所示。Lee等人将氧化石墨烯作为栅介质[29],石墨烯既作为导电沟道,也作为导电电极,便得到了全石墨烯柔性晶体管。图9b是通过滚压印技术[28]来加工石墨烯TFT阵列示例,其中,离子凝胶为晶体管栅介质,PET为衬底。图9c为共平面石墨烯TFT阵列[29],通过气溶胶喷墨打印技术来加工离子凝胶栅介质。另外,还有研究小组将石墨烯和石墨集成为一个整体的TFT阵列,通过空间成型的不同的金属催化剂来有选择性的制备石墨烯和石墨[34],这样将有希望通过一步工艺来实现石墨烯晶体管的加工。

3.4 石墨烯柔性透明晶体管展望

石墨烯不仅可以作为沟道材料、电极材料,也可以作为导电互连材料和电阻材料,并且与栅介质材料如GO、离子凝胶和其他有机材料都有很好的兼容性。在制造工艺方面,石墨烯柔性透明晶体管不仅可以通过常规半导体工艺实现,也可以通过辊压印技术、Langmuir-Blodgett(LB)工艺技术[33]以及气溶胶喷墨打印等非常规半导体技术方便又廉价地实现。

4 总结与展望

本文从石墨烯数字晶体管、石墨烯射频晶体管和石墨烯柔性透明晶体管等3个方面对石墨烯晶体管进行分析和总结。石墨烯数字晶体管最基本的要求是具有足够的电流开关比和实现互补逻辑。在改进制备方法的条件下,构造石墨烯纳米带阵列结构应该是比较具有潜力的研究思路,不仅提供了更多的沟道,而且抑制散射,有望具有高的开关比和导通电流。另外构造异质结结构,非常有希望提高石墨烯晶体管的开关比和饱和电流。虽然制造出与石墨烯晶格匹配的介质材料如氮化硼等目前还有很大的挑战,但是纵向异质结结构有望构造隧道晶体管,实现高的开关比,是一个很有前途的方向。石墨烯射频晶体管主要是利用石墨烯高迁移率和低电阻的特性,理论上可以实现很高截止频率和良好的饱和特性,目前主要受接触电阻和未被栅覆盖的接入电阻过大的影响。通过减小石墨烯和金属的接触电阻、石墨烯射频晶体管的接入电阻,以及选择不同的衬底和栅介质来匹配石墨烯载流子迁移率以提高其射频性能将是主要研究热点。石墨烯柔性透明晶体管与硬衬底晶体管相比,对衬底和栅介质的要求特别高,需要界面更光滑以保持载流子迁移率,且要求衬底和栅介质是柔性的,以保证器件在变形的情况下仍能稳定工作。提出PET衬底和离子凝胶栅介质是最实用和有前途的工艺组合,能够在保证石墨烯迁移率的基础之上产生较大的栅电容,有望实现全石墨烯透明柔性电路。如果石墨烯晶体管得以实用,必将对集成电路行业产生巨大影响,同时促进相关联行业的进步。

[1] IEONG M, DORIS B, KEDZIEJAKUB J, et al. Silicon device scaling to the sub-10-nm regime [J]. Science, 2004, 306: 2057-2060.

[2] PONOMARENKO L A, SCHEDIN F, KATSNELSON M I, et al. Chaotic dirac billiard in graphene quantum dots [J]. Science, 2008, 320: 356-358.

[3] SCHWIERZ F. Graphene transistors [J]. Nature Nanotechnology, 2010, 5: 487-496.

[4] BALANDIN A A, GHOSH S, BAO W, et al. Superior thermal conductivity of single-layer graphene [J]. Nano Letters, 2008, 8(3): 902-907.

[5] LI X, WANG X, ZHANG L, et al. Chemically derived, ultrasmooth graphene nanoribbon semiconductors [J]. Science, 2008, 319: 1229-1231.

[6] BAI J, ZHONG X, JIANG S, et al. Graphene nanomesh [J]. Nature Nanotechnology, 2010, 5: 190-194.

[7] CAI J, RUFFIEUX P, JAAFARFAR R, et al. Atomically precise bottom-up fabrication of graphene nanoribbons [J]. Nature Letters, 2010, 466: 470-473.

[8] ZENG Z, HUANG X, YIN Z, et al. Fabrication of graphene nanomesh by using an anodic aluminum oxide membrane as a template [J]. Advanced Materials, 2012, 24(30): 4138-4142.

[9] YANG Y, MURALI R. Impact of size effect on graphene nanoribbon transport [J]. IEEE Electron Device Letters, 31(3): 237-239.

[10]MOON J S, SEO H, STRATAN F, et al. Lateral graphene heterostructure field-effect transistor [J]. IEEE Electron Device Letters, 2013, 34(9): 1190-1192.

[11]BRITNELL L, GORBACHEV R V, JALIL R, et al. Field-effect tunneling transistor based on vertical graphene heterostructures [J]. Science, 2012, 335: 947-950.

[12]GEORGIOU T, JALIL R, BELLE B D, et al. Vertical field-effect transistor based on graphene-WS2heterostructures for flexible and transparent electronics [J]. Nature Nanotechnology, 2013, 8: 100-103.

[13]LIU Z, MA L, SHI G, et al. In-plane heterostructures of graphene and hexagonal boron nitride with controlled domain sizes [J]. Nature Nanotechnology, 2013, 8: 119-124.

[14]GUO B, LIU Q, CHEN E, et al. Controllable N-doping of graphene [J]. Nano Letters, 2010, 10(12): 4975-4980.

[15]WANG X, LI X, ZHANG L, et al. N-doping of graphene through electrothermal reactions with ammonia [J]. Science, 2009, 324: 768-771.

[16]KIM H H, YANG J W, JO S B, et al. Substrate-induced solvent intercalation for stable graphene doping [J]. ACS Nano, 2013, 7(2): 1155-1162.

[17]TANG Y B, YIN L C, YANG Y, et al. Tunable band gaps and p-type transport properties of boron-doped graphenes by controllable ion doping using reactive microwave plasma [J]. ACS Nano, 2012, 6(3): 1970-1978.

[18]PANCHAKARLA L S, SUBRAHMANYAM K S, SAHA S K, et al. Synthesis, structure, and properties of boron- and nitrogen-doped graphene [J]. Advanced Materidals , 2009, 21: 4726-4730.

[19]WANG L, MERIC I, HUANG P Y, et al. One-dimensional electrical contact to a two-dimensional material [J]. Science, 2013, 342: 614-617.

[20]LI W, LIANG Y, YU D, et al. Ultraviolet/ozone treatment to reduce metal-graphene contact resistance [J]. Applied Physics Letters , 2013, 102: 183110.

[21]MATSUDA Y, DENG W Q, GODDARD W A, et al. Contact resistance for “end-contacted” metal-graphene and metal-nanotube interfaces from quantum mechanics [J]. The Journal of Physical Chemistry: C, 2010, 114: 17845-17850.

[22]SMITH J T, FRANKLIN A D, FARMER D B, et al. Reducing contact resistance in graphene devices through contact area patterning [J]. ACS Nano, 2013, 7(4): 3661-3667.

[23]JUNG M H, PARK G H, YOSHIDA T, et al. High-performance graphene field-effect transistors with extremely small access length using self-aligned source and drain technique [J]. Proceedings of IEEE, 2013, 101(7): 1603-1608.

[24]MOVVA H C P, RAM M E, CORBET C M, et al. Self-aligned graphene field-effect transistors with polyethyleneimine doped source/drain access regions [J]. Applied Physics Letters, 2012, 101: 183113.

[25]AL-AMIN C, VABBINA P K, KARABIYIK M, et al. Improving high-frequency characteristics of graphene FETs by field-controlling electrodes [J]. IEEE Electron Device Letters, 2013, 34(9): 1193-1195.

[26]LIAO L, LIN Y C, BAO M, et al. High-speed graphene transistors with a self-aligned nanowire gate [J]. Nature, 2010, 467: 305-308.

[27]DEAN C R, YOUNG A F, MERIC I, et al. Boron nitride substrates for high-quality graphene electronics[J]. Nature Nanotechnology, 2010, 5: 722-726.

[28]YAN C, CHO J H, AHN J H. Graphene-based flexible and stretchable thin film transistors [J]. Nanoscale, 2012, 4: 4870-4882.

[29]KIM B J, LEE S K, KANG M S, et al. Coplanar-gate transparent graphene transistors and inverters on plastic [J]. ACS Nano, 2012, 6(10): 8646-8651.

[30]KIM B J, JANG H, LEE S K, et al. High-performance flexible graphene field effect transistors with ion gel gate dielectrics [J]. Nano Letters, 2010, 10: 3464-3466.

[31]ZHANG D B, SEIFERT G, CHANG K, et al. Strain-induced pseudomagnetic fields in twisted graphene nanoribbons [J]. Physical Review Letters, 2014, 112: 096805.

[32]LEE S, JO G, KANG S, et al. Enhanced charge injection in pentacene field-effect transistors with graphene electrodes [J]. Advanced Materials, 2011, 23: 100-105.

[33]LEE S K, JANG H Y, JANG S, et al. All graphene-based thin film transistors on flexible plastic substrates [J]. Nano Letters, 2012, 12: 3472-3476.

[34]PARK J U, NAM S W, LEE M S, et al. Synthesis of monolithic graphene-graphite integrated electronics [J]. Nature Materials, 2012, 11: 120-125.

(编辑 刘杨)

LatestAdvanceofResearchesonGrapheneTransistors

LI Xin,GUO Shixi,SONG Hui,LI Quanfu,SHI Junjie,FANG Ming,WANG Xiaoli,LIU Weihua

(School of Electronics and Information Engineering, Xi’an Jiaotong University, Xi’an 710049, China)

According to the research hotspot arised by the difficulties that when the feature sizes of integrated circuits become less than 10 nm, the silicon ICs are unlikely stable due to the short channel effect, tunneling effect and manufacturing process limits, the latest advance of researches on graphene transistors are discussed from three aspects including digital transistors, radio frequency (RF) transistors and flexible transparent transistors. Graphene nanoribbons array parallel structure and heterogeneous structure are the most promising approaches on opening the graphene band gap to achieve a high on/off current ratio and to achieve complementary logic. The main development trend of graphene RF transistors is to improve the cut-off frequency and maximum oscillating frequency by reducing the contact resistance and access resistance, and matching the interface between substrate and gate dielectric. It is realized that the flexible manufacturing technology of Polythylene terephthalate (PET) substrate and Ion Gel gate dielectric are the most promising approaches to achieve a full graphene transparent flexible circuit and to keep graphene high mobility. Graphene transistors will have a huge impact on the integrated circuit industry.

graphene transistors; bandgap; cutoff frequency; maximum oscillation frequency; flexibility transistors

2014-04-04。

李昕(1968—),女,副教授;王小力(通信作者),男,教授,博士生导师。

国家自然科学基金资助项目(91123018,61172041,61172040);陕西省自然科学基金资助项目(2014JM7277)。

时间:2014-08-11

10.7652/xjtuxb201410001

TN304.9

:A

:0253-987X(2014)10-0001-08

网络出版地址:http:∥www.cnki.net/kcms/detail/61.1069.T.20140811.1039.005.html