一种任意比率电子齿轮分频器的实现方法

申建广,陶涛,2,梅雪松,2,许睦旬,刘善慧,彭志会

(1.西安交通大学机械工程学院, 710049, 西安; 2.西安交通大学机械制造系统工程国家重点实验室, 710049, 西安)

一种任意比率电子齿轮分频器的实现方法

申建广1,陶涛1,2,梅雪松1,2,许睦旬1,刘善慧1,彭志会1

(1.西安交通大学机械工程学院, 710049, 西安; 2.西安交通大学机械制造系统工程国家重点实验室, 710049, 西安)

针对滚齿机数控系统电子齿轮箱的设计要求,提出了一种根据现场可编程门阵列和Bresenham算法的任意比率电子齿轮分频器的实现方法。该方法的实现原理是将计算机图形学上描绘由两点所决定的直线的算法应用到电子齿轮的脉冲频率分频上,采用硬件描述语言来实现电子齿轮分频。该方法对Bresenham算法进行了改进,将累计误差值和溢出斜率修改为整数,使算法只涉及整数的加减运算,因此更快捷、更可靠。软件仿真和实验结果表明,所提出的电子齿轮分频方法可使分频过程更为简便,不仅减少了硬件资源耗费,而且算法具有较强的实用性。

滚齿机;电子齿轮;Bresenham算法;任意分频器

在滚齿机数控系统中,电子齿轮功能及脉冲合成的组合可以完成展成运动和差动运动,是滚齿运动控制的关键[1]。电子齿轮实现了机械传动的电气化,齿轮比可以任意改变,可以随时增加电子齿轮的数量,使用灵活方便,传动比范围大,而且传递运动的精度高,在简化机械传动系统、替代内联传动方面得到了广泛的应用[2]。

目前,电子齿轮的实现方式主要有硬件实现的模拟式的电子齿轮、软件实现的电子齿轮,以及利用锁相环方式实现的电子齿轮等[3-5]。在滚齿机数控系统中,需要用到多种频率的时钟脉冲信号,考虑到同步性和硬件成本的影响不可能为每个时钟信号提供晶振,因此电子齿轮需要通过设计数字电路分频器的方式来实现。数字分频器的设计方法主要有奇数分频器设计、偶数分频器设计和分数分频器设计[6-7],其中分数分频器的实现方法最为复杂。文献[3]提出了任意整数分频器的实现方法,文献[6-8]分别提出了不同小数分频器的实现方法,该方法可以实现分数分频,但算法涉及乘除运算和浮点运算,运算速度和资源消耗较大。文献[9]设计的任意分数分频器,通过采用2个整数分频来实现分数的分频,但是在实现之前需要软件实现相关的计算,在实际的现场可编程门阵列(FPGA)中控制2种分频信号的均匀分布也比较复杂,不同分数对应的2种整数分频出现的次数差异较大且均匀化较为困难,造成这种方法的稳定性不好,输出信号易抖动[10],而且不同分频系数误差的出现形式和位置也不尽相同。Thomas等人提出了基于Bresenham算法的分数分频器设计[11],该方法运算简单快捷、稳定性较好,但只能应用于实现分频系数小于1/2的分数分频。

本文对Bresenham算法[12]进行了改进,采用Verilog-HDL硬件语言在FPGA上进行了算法实现和电路综合,设计出了通用的任意分数分频器。通过FPGA实现脉冲式电子齿轮的功能,并结合硬件电路和软件控制完成了电子齿轮的设计。本文通过QuartusII软件平台进行了仿真,并在自主开发的滚齿机数控系统中对该实现方法进行了实验验证,证明了该方法可行性强,具有配置灵活、实时性高、精度高的特点。

1 电子齿轮分频原理

电子齿轮在数控系统中是通过对输入和输出脉冲频率进行处理来实现运动控制的,因此实现任意传动比电子齿轮的关键是如何设计任意分频比率的分频器。设计出的分频器电路应满足如下关系式

(1)

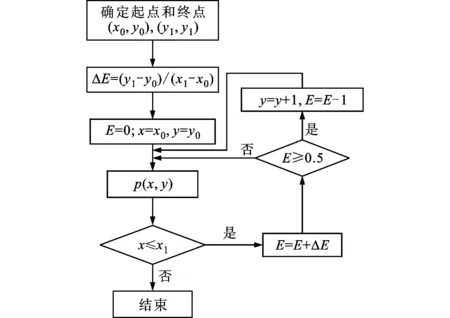

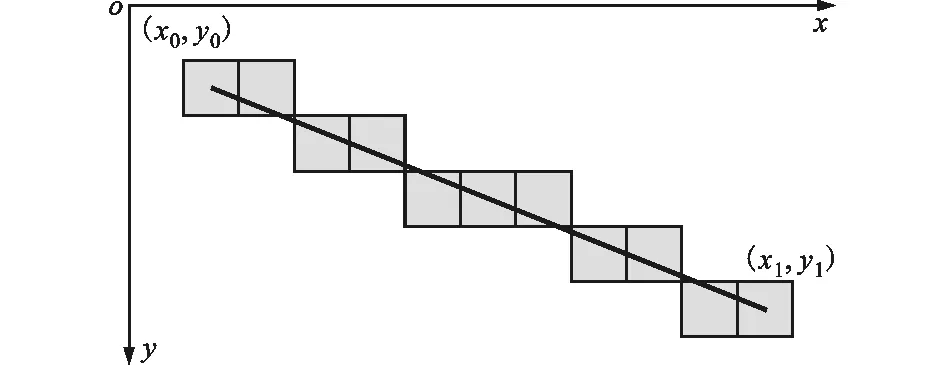

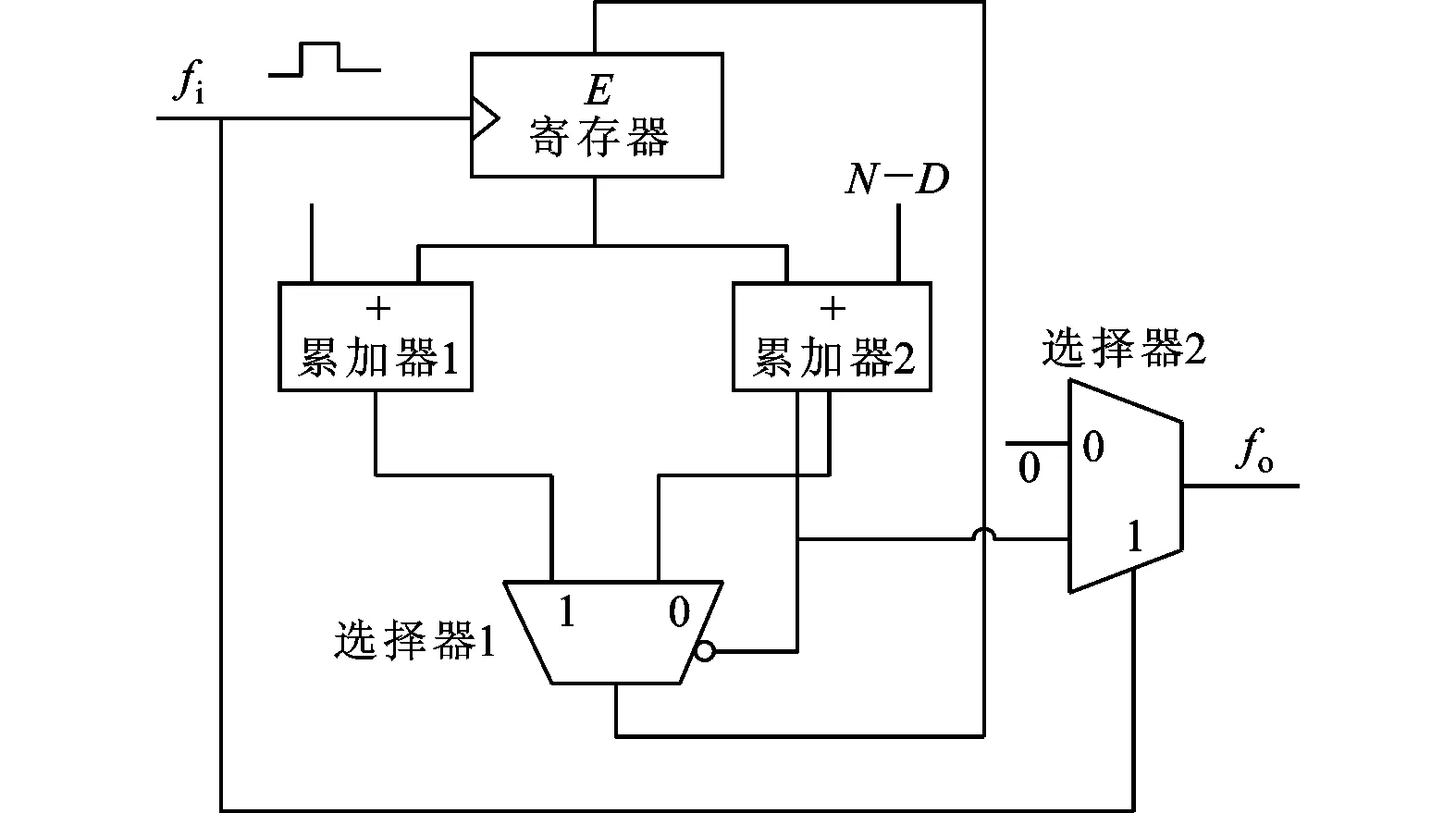

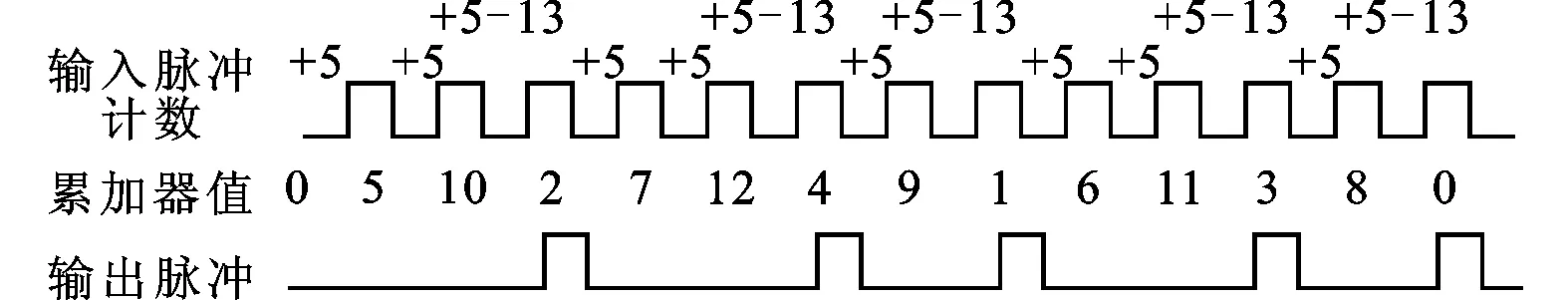

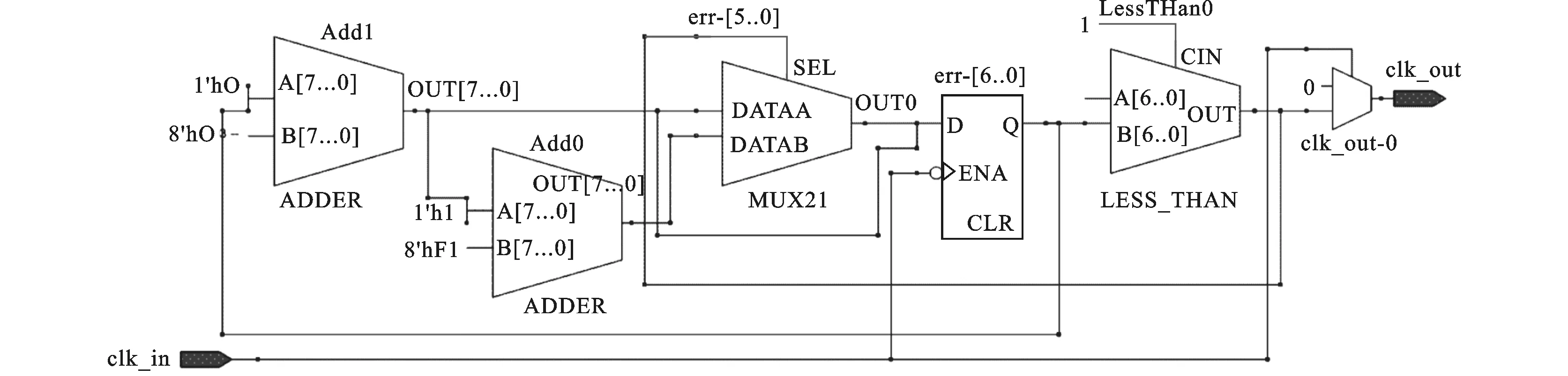

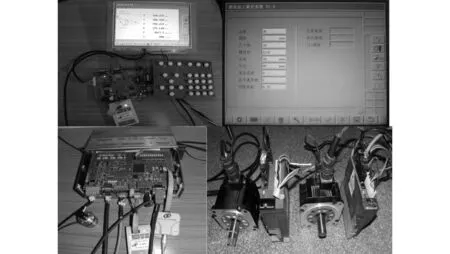

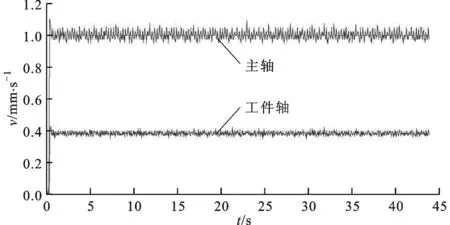

式中:fo为输入频率;fi为输出频率;N、D为整数,且N 1.1Bresenham算法 E:累计误差 Bresenham算法是经典的直线生成算法[12],算法框图如图1所示。如图2所示,选用电脑系统常用坐标系,从(x0,y0)绘画直线至右下角的点(x1,y1),x、y分别代表其水平及垂直坐标,并且x1-x0>y1-y0。x、y的值分别向右及向下增加,而两点间的水平距离为x1-x0且垂直距离为y1-y0。由此可知,该线的斜率必定在1~0之间。此算法的目的就是找出在x0与x1之间、与第x行相对应的第y列,从而得出像素点,使得该像素点的位置最接近原始的直线。 图2 Bresenham直线 1.2 算法改进 对Bresenham算法进行改进,使ΔE等于Δx,溢出斜率由0.5修改为Δy,从而算法只涉及整数的加减运算,因此更快捷、更可靠。改进算法如图3所示。 图3 Bresenham改进算法 将Bresenham算法应用到FPGA硬件电路中,设x坐标像素点为输入脉冲,y坐标像素点为输出脉冲,即每当输入N个脉冲时,便可得到D个输出脉冲。 根据改进的Bresenham直线算法,设计出了一种任意分数分频器。当一个控制周期内输入脉冲为fi时,输出的脉冲为fo。fi和fo的关系如下 (2) 如果把这个控制周期缩短为fi=D,则这个周期内输出的脉冲数为N,即控制周期很短,因此可以由FPGA进行控制,分频器的原理如图4所示。 图4 采用Bresenham算法的任意分数分频器的原理图 当系统输入一个脉冲时,寄存器的值累加N,当累加值大于D时即输出一个脉冲,然后将累加器2的值放入寄存器中,在输入下一个脉冲时继续累积,依次循环。因此,当输入脉冲个数为D时,输出的脉冲个数刚好为N,依次类推,就可以完成整个输入脉冲序列的分频输出。 图5 分频系数为5/13的分频示意图 当D为N的整数倍时,即可实现任意整数的分频。当N 3.1 误差分析 根据Bresenham改进算法的分频原理,对于分频系数为N/D的电子齿轮,因为输出的脉冲是单个的,因此输入和输出之间是有误差的,最大的输出误差为1个脉冲。为了计算出电子齿轮脉冲输出误差,输入脉冲从0开始计数,令输入fi个脉冲时的输出脉冲为0,并且输入fi+1个脉冲时输出1个脉冲,此时对应的fi即为最大输入脉冲数,并对应最大输出脉冲误差,用数学关系表示如下 (3) 因此可以计算得出 (4) 由此对应电子齿轮的输出脉冲误差为 (5) 由式(5)可以看出,电子齿轮输出脉冲的最大输出误差始终小于1个脉冲,并且输出误差随输入脉冲呈现周期为D的周期性变化。 3.2 仿真及实验结果 为验证所设分频器是否能达到预期效果,本文通过Quartus II对其进行了综合和仿真实验。综合电路图如图6所示,用FPGA电路来完成该电子齿轮分频器的设计,仅占用15个逻辑单元(LE),从而提高了执行效率,降低了资源消耗。 Quartus II的仿真结果如图7所示,图中clk_in、clk_out分别表示输入脉冲和输出脉冲,err为累加器,可以看出图7中的仿真值和图5中的理论值是一致的。 为进一步验证电子齿轮的分频效果,采用自行设计的基于FPGA与双MCU的滚齿机专用数控系统,对电子齿轮的实际分频信号进行采集,并对采用电子齿轮控制的主轴电机和工件轴电机的实际位置进行采集,实验装置如图8所示。实验采用基频频率为100 MHz的时钟频率,主轴的速度为60 mm/min,电子齿的分频系数为5/13,实验结果如图9所示。图9中分频结果与仿真结果相一致,主轴和工件轴的转速v都能够严格保持设定的电子齿轮比。 图6 分频器综合电路图 图7 分频系数为5/13的仿真结果 图8 滚齿机专用数控系统 (a)分频实验结果 (b)滚齿机速度实验结果 本文通过对Bresenham算法进行改进,将其应用到数控滚齿机的电子齿轮分频控制上,设计出了一种任意比率的电子齿轮分频器。本文所设计的电子齿轮算法只涉及整数的加减运算,不仅使分频过程更为简单和可靠,而且减少了硬件资源的耗费。仿真和实验结果表明,本文所设计的电子齿轮分频器方法新颖、设计简单、使用灵活,具有输出脉冲均匀、精度高、实时性好的实用特性。 [1] 胡赤兵, 田芳勇, 姜衍仓. 电子齿轮箱在非圆齿轮滚齿加工中的应用 [J]. 机械设计与制造, 2009(12): 79-81. HU Chibing, TIAN Fangyong, JIANG Yancang. Application of the electrical gearbox in the hobbing non-circular gear [J]. Machinery Design & Manufacture, 2009(12): 79-81. [2] DINSDALE J, JONES P F, Thorneycroft M. The electronic gearbox-computer software replaces mechanical couplings [J]. CIRP Annals: Manufacturing Technology, 1982, 31(1): 247-249. [3] TIAN Hongli, SHI Shuo. Controllable arbitrary integer frequency divider based on VHDL [C]∥2009 International Joint Conference on Artificial Intelligence. Amsterdam, Netherlands: Artificial Intelligence, 2009: 691-694. [4] SEONCHEOL K, YOUNGSIK K. A fractional-NPLL frequency synthesizer design [C]∥Proceedings of the IEEE Southeast Conference 2005. Piscataway, NJ, USA: IEEE, 2005: 84-87. [5] 滕福林, 李宏胜, 温秀兰, 等. 电子齿轮比对轮廓误差及加工效率影响的研究 [J]. 中国机械工程, 2012, 23(13): 1607-1610. TENG Fulin, LI Hongsheng, WEN Xiulan, et al. Research on influences on contour error and cutting efficiency from electrical gear-ratio [J]. Chinese Mechanical Engineering, 2012, 23(13): 1607-1610. [6] 常兴旺, 李孝辉, 王玉兰, 等. 基于FPGA的小数分频的研究与设计 [J]. 电子测量与仪器学报, 2009(增刊): 253-255. CHANG Xingwang, LI Xiaohui, WANG Yulan, et al. Design of decimal fraction frequency divider based on FPGA technology [J]. Journal of Electronic Measurement and Instrument, 2009(Supplement): 253-255. [7] 冯焱, 周海东, 忤婷, 等. 多模式定位系统接收机中的分数频率综合器 [J]. 西安交通大学学报, 2011, 43(12): 35-39. FENG Yan, ZHOU Haidong, WU Ting, et al. A fractional-n frequency synthesizer for multi-mode positioning system receivers [J]. Journal of Xi’an Jiaotong University, 2011, 43(12): 35-39. [8] GU Liangling, ZHOU Nanquan. Research of frequency divider based on programmable logic device [J]. Procedia Environmental Sciences, 2011, 10: 820-824. [9] HU Xiaoping, LIN Yunfeng. Realization on decimal frequency divider based on FPGA and Quartus II [C]∥Communication in Computer and Information Science. Berlin, German: Springer, 2011: 350-356. [10]尹辉炳, 张涛. 基于VHDL的全数字分数分频器设计 [J]. 科学技术与工程, 2006, 6(12): 1609-1611. YIN Huibing, ZHANG Tao. The design of total digitized fractional frequency divider based on VHDL [J]. Science Technology and Engineering, 2006, 6(12): 1609-1611. [11]PREUBER T B, SPALLEK R G. Analysis of a fully-scalable digital fractional clock divider [C]∥International Conference on Application-specific Systems. Samos, Greece: Architectures and Processors, 2006: 133-177. [12]JACK E B. Algorithm for computer control of a digital plotter [J]. IBM Systems Journal, 1965, 4(1): 25-30. (编辑 管咏梅) RealizationofArbitraryRatioFrequencyDivisionElectronicGear SHEN Jianguang1,TAO Tao1,2,MEI Xuesong1,2,XU Muxun1,LIU Shanhui1,PENG Zhihui1 (1. School of Mechanical Engineering, Xi’an Jiaotong University, Xi’an 710049, China; 2. State Key Laboratory for Manufacturing Systems Engineering, Xi’an Jiaotong University, Xi’an 710049, China) A new electronic gear based on Bresenham algorithm and field-programmable gate array (FPGA) is presented to realize the arbitrary ratio fractional frequency for the design of hobbing machine CNC system. The basic principle of this realization method determines the order to form a closer approximation to a straight line between two given points, which is usually used to draw lines on a computer screen, and applied for fractional frequency divider at arbitrary ratio in hardwere description language (HDL) on the FPGA. This new algorithm eliminates expensive multiplications and divisions as well as numerical scaling to integer-only arithmetic, so achieves high efficiency and good stability. Generic synthesizable Verilog-HDL design following this algorithm is simulated on Quartus II system and examined by synthesis examples on CNC system. gear hobbing machine; electronic gear; Bresenham algorithm; fractional frequency divider 10.7652/xjtuxb201401016 2013-07-01。 作者简介: 申建广(1984—),男,博士生;陶涛(通信作者),男,教授,博士生导师。 基金项目: 国家科技支撑计划资助项目(2013BAF04B01)。 时间: 2013-10-17 网络出版地址: http:∥www.cnki.net/kcms/detail/61.1069.T.20131017.0827.015.html TN772 :A :0253-987X(2014)01-0096-05

2 分频器设计

3 仿真及实验结果

4 结 论