基于SATA接口固态硬盘的高速存储系统设计

孙海波, 王晓斌, 李雅梅

(北京强度环境研究所 北京 100076)

基于SATA接口固态硬盘的高速存储系统设计

孙海波, 王晓斌, 李雅梅

(北京强度环境研究所 北京 100076)

介绍一种基于SATA接口固态硬盘的高速存储系统。采用LVDS接口实现高速数据输入,通过IDE-SATA转接芯片JMH330S实现SATA接口固态硬盘的高速读写控制。采用千兆以太网作为控制和数据下载接口,利用Microblaze软核运行LwIP协议栈,实现TCP/IP协议。测试结果证明,系统可支持600Mb/s的连续LVDS数据流输入,存储的数据完整可靠。

SATA; LVDS; 固态硬盘; 存储; 千兆以太网

前言

近年来,航天任务中对嵌入式数据采集存储系统的要求越来越高,主要表现在采集通道数量的增加、信号采样率的提高、信号采样精度的提升。而目前存储系统较低的存储带宽成为数据采集系统的瓶颈。采用FPGA控制FLASH阵列可以达到较高的存储带宽[1],但是对于高可靠性应用,需要设计非常可靠的坏块管理算法和纠错码校验ECC(Error Correcting Code)算法,实现起来比较复杂。

近年来出现的SATA接口固态硬盘具有存储速度高、存储容量大、可靠性高等优点,可以满足航天领域对数据存储的要求。由于SATA协议复杂,直接使用FPGA控制SATA接口固态硬盘成本高,难度大,开发周期长,由此也带来可靠性的降低。本文使用FPGA控制IDE-SATA转接芯片JMH330S,实现了基于SATA接口固态硬盘的高速存储系统,数据输入接口为低压差分信号LVDS(Low-Voltage Differential Signaling),数据下载接口为千兆以太网,系统支持掉电保护功能,可靠性高,通用性强,适用于多种应用场合。

1 系统组成

基于SATA接口固态硬盘的高速存储系统的系统组成如图1所示。前端数据采集系统(或其它数据源)产生的数据通过高速LVDS接口发送至存储系统。存储系统的主控芯片采用Spartan6 XC6SLX45 FPGA,FPGA内部的LVDS接收模块接收LVDS数据流并将其转换为并行数据。并行数据通过深度为32k的SAVE_FIFO进入IDE接口模块。在数据管理模块控制下,IDE接口模块读取SAVE_FIFO的数据,并通过JMH330S芯片控制固态硬盘进行高速存储;读取数据时,IDE接口模块将读出的硬盘数据存入CPU_ FIFO中,Microblaze通过DMA方式将数据读入其DDR3内存,并通过千兆以太网发送至上位机。Microblaze是FPGA内部的嵌入式CPU,它以DDR3为内存,运行TCP/IP协议栈,主要用来处理接收的以太网、RS422命令,将上层控制指令解析并传递至数据管理模块,完成数据存储、读取、删除等功能。

图1 基于SATA接口固态硬盘的高速存储系统组成

2 模块设计

2.1 LVDS接收模块

LVDS使用很低的电压幅度(100mV~450mV)通过一对平行的PCB走线或平衡电缆传输高速数据。在两条平行的差分信号线上,电流及电压振幅相反,噪声信号同时耦合到两条线上,接收端只关心两信号的差值,因此噪声会被抑制掉。LVDS高速、低功耗、低噪声等特点使其在板级高速数据传输中得到广泛应用。

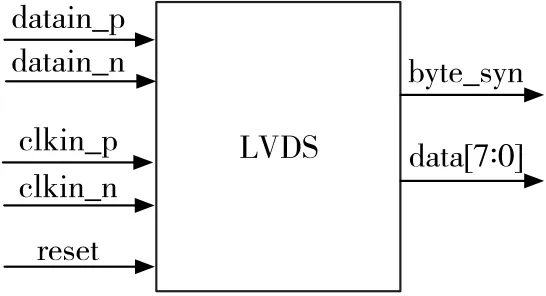

本系统采用两对LVDS数据线,分别为伴随时钟线差分对和数据线差分对。LVDS伴随时钟的频率为75MHz,串行解串因子(SerDes ratio)为8:1,即每个伴随时钟周期内传输8bits数据,故数据码率为600Mb/ s。Spartan6 FPGA可支持高达1050Mb/s的LVDS数据接收和发送,利用FPGA内部丰富的解串器(ISERDES)、锁相环PLL(Phase Locked Loop)和延时(IODELAY)资源,可实现2:1~16:1的数据解串[2]。LVDS接收模块的功能是将串行LVDS码流解串为并行数据。本模块的输出接口为字节同步信号byte_ syn和8位并行输出信号data[7:0]。LVDS接收模块输入输出接口见图2。

图2 LVDS接收模块输入输出接口

2.2 JMH330S介绍

JMH330S是SATA-IDE桥接芯片,符合SATA1.0版本规范,可兼容SATA2.0和SATA3.0接口固态硬盘,最高可支持ATA Ultra DMA模式7,理论数据传输速度可达150MB/s。JMH330S主要实现IDE总线数据、地址、控制信号与SATA总线数据、地址、控制信号的转换,故只需采用传统的IDE控制接口即可实现高速SATA接口固态硬盘的读写,简化了设计,节省了成本。

2.3 IDE接口模块

IDE接口的硬盘传输模式有PIO、DMA以及Ultra DMA三种方式。Ultra DMA方式在选通信号的上升沿和下降沿均锁定数据,提高了数据的传输速率,并且在数据传输结束时还要进行循环冗余校验CRC (Cyclic Redundancy Code),具有较高的可靠性。本文在寄存器读写时采用PIO方式,在存储数据时采用Ultra DMA模式5,最高数据传输速度为100MB/s。IDE接口模块的功能主要包括设备(硬盘)初始化,Write DMA和Read DMA(二者均以Ultra DMA模式传输数据)。

根据ATA-6协议[3],在硬盘初始化时,FPGA通过SetFeatures命令将IDE传输方式设置为Ultra DMA模式5。每次Ultra DMA写操作时,首先设置起始48位逻辑地址和将要写入的扇区数,然后通过向状态控制寄存器写命令0x35启动一次Write DMA操作。硬盘收到控制命令后,会向IDE接口模块发送DMA请求(DMARQ)信号,IDE接口模块用DMACK_应答并撤销STOP信号,在硬盘DMARDY_信号有效后,IDE接口模块开始读取SAVE_FIFO中数据并驱动数据同步信号HSTROBE以及16位并行数据。Ultra DMA模式5的传输速度为100MB/s,数据宽度为16bits,由于在HSTROBE信号的上升沿和下降沿均传递数据,故HSTROBE信号为25MHz。Write DMA过程采用100MHz时钟,rden为SAVE_FIFO读使能信号。使用FPGA片内逻辑分析仪ChipScope截取的Write DMA时序图见图3。

图3 Ultra DMA写操作时序图

在Write DMA过程中,可能会出现硬盘DMARDY_信号无效,该现象为硬盘暂停Write DMA。此时主机应继续产生3个HSTROBE信号并进行3次数据传输,等待硬盘DMARDY_信号有效后,继续进行Write DMA操作。否则会出现数据错误的情况。

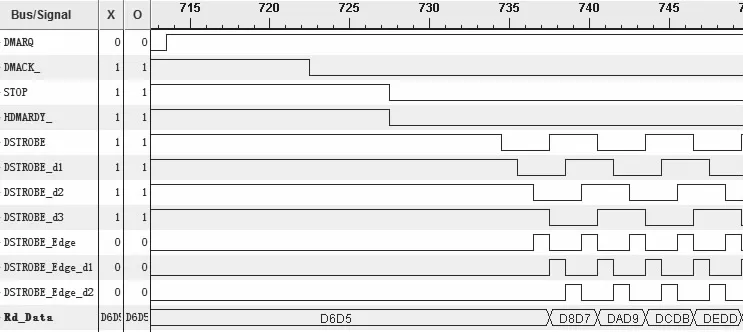

对于Read DMA操作,过程类似,使用ChipScope截取的Read DMA时序见图4。由于JMH330S输出的数据同步信号DSTROBE为异步信号,因此应首先经过2级D触发器同步化处理,得到DSTROBE_d2。DSTROBE_d2与DSTROBE_d3(DSTROBE_d2延迟一个时钟周期)异或得到上升沿和下降沿信号DSTROBE_Edge。该信号相对原DSTROBE信号已延迟了3个时钟周期,此时读取经过3级D触发器同步后的总线数据得到Rd_Data信号。分别使用DSTROBE_Edge_d2信号(DSTROBE_Edge经过2级D触发器延迟)和Rd_Data信号作为CPU_FIFO的写使能和写数据信号。DSTROBE的频率为25MHz,DSTROBE _Edge的频率为50MHz,而采样时钟应大于DSTROBE_Edge频率的两倍,在本文中,采样时钟为150MHz。

图4 Ultra DMA读操作时序图

2.4 数据管理模块

数据管理模块实现的功能主要是接收Microblaze软核的命令,控制数据存储、数据读取、数据删除等数据存储管理的功能,并在突然断电时完成掉电保护功能。

2.4.1 数据存储管理

数据管理模块将固态硬盘中逻辑地址为0x100的页作为信息记录页(每页为512字节),记录总存储次数、每次存储的起始地址、存储页长度等信息。系统上电时,读取固态硬盘的信息记录页并暂存入双口RAM的指定地址处。当数据管理模块收到Microblaze软核的开始存储命令时,根据上一次的存储起始地址和存储页长度,生成本次存储的起始地址。并且当SAVE_FIFO中达到8192个字的深度时开始一次Write DMA(每次写32页),同时累加该次的存储页长度。在收到停止存储命令时,应继续从SAVE_FIFO中读取32k数据进行存储,以防止存储数据不完整,并将新的存储次数、该次存储的起始地址、存储页长度写入双口RAM的指定地址处,存储至固态硬盘的信息记录页。当收到Microblaze软核的数据读取命令以及读取次数索引值时,数据管理模块从双口RAM中指定位置得到本次存储的起始地址和存储页长度,开始Read DMA过程,并通过CPU_FIFO接口将读出的数据传递至Microblaze软核。

2.4.2 掉电保护

由于固态硬盘中存在较大的数据缓冲区,当突然断电时,缓冲区中的数据可能还未存入固态硬盘内部的FLASH中,造成数据丢失。本存储系统采用后备电池进行掉电保护,其机制如下:正常情况下,系统由9V外部电源供电,当外部电源的电压低于电池电压(7.2V)时,由二极管电路自动转至后备电池供电;当比较器电路检测到外部电源电压低于7V时,如果在存储状态下,数据管理模块强制执行停止存储命令,存储SAVE_FIFO中剩余数据和信息记录页;然后持续供电1秒,确保固态硬盘完成全部数据的存储,最后控制继电器断开电池供电。

2.5 Microblaze软核

通过嵌入式片上可编程系统SOPC(System On Programmable Chip)技术在FPGA内部建立32位Microblaze软核,运行嵌入式程序。Microblaze软核的组成架构如图5所示。其中DDR3和axi_dma模块通过高速AXI总线与Microblaze软核实现互联,其他低速外设通过AXI_lite总线与之互联。

图5 Microblaze组成架构

128MB的DDR3是数据和程序运行空间。Microblaze软核与数据管理模块的命令接口(CMD)采用axi_gpio IP核实现。读取硬盘数据时,需要将逻辑中CPU_FIFO内数据读取至DDR3,然后通过千兆以太网实现高速数据发送。为了提高数据吞吐量,采用成熟IP核axi_dma配合自定义的axistream_fifo模块实现高速数据读取,自定义的axistream_fifo模块符合axi4_stream协议。同时,使用IP核axi_ethernet和axi_ dma实现千兆以太网功能,作为数据高速下载接口。读取硬盘数据时流程如下:首先配置axi_dma1,开启读取CPU_FIFO的DMA通道,将数据放入DDR3中,然后开启axi_dma2的DMA通道,将DDR3中的数据通过千兆以太网接口发送出去。

通过千兆以太网或RS422,可实现用户控制指令接收功能和数据下载功能。为保证千兆以太网发送数据的可靠性,采用LwIP协议栈实现TCP网络协议。LwIP是瑞士计算机科学院开发的一套用于嵌入式系统的开放源代码TCP/IP协议栈。LwIP的含义是Light Weight(轻型)IP协议,它可以在无操作系统的情况下独立运行。在软件开发工具包(SDK)中包含了LwIP 1.4.0的源码与库,可以通过工具直接生成针对axi_ethernet的驱动,使用简单,代码少,运行方便[4,5]。

3 性能测试

在系统进行存储时,每16k字节启动一次Write DMA,使用示波器观察DMARQ信号。DMARQ信号的平均有效时间为190μs,即最大存储速度约为82MB/s。留有一定裕量,采用速度为75MB/s的LVDS数据源测试系统性能。数据源的时钟频率为75MHz,串行解串因子为8:1,即数据码率为600Mb/s,输出的LVDS测试数据为累加数据。固态硬盘的型号为三星840pro-128G,经过100次采集存储100s数据,并下载至上位机,千兆以太网的平均数据下载速度为24MB/s。通过数据分析得知,数据正确无误,无误码和丢数现象。测试结果验证了本文介绍的基于SATA接口固态硬盘高速存储系统的可靠性。

4 结束语

本文介绍了一种基于SATA接口固态硬盘的高速存储系统,它采用高可靠的SATA接口固态硬盘作为存储介质,使用高速LVDS接口作为数据输入接口,并采用千兆以太网作为数据导出接口,支持掉电保护功能,可以实现高速、可靠的数据存储与下载。该系统协议简单,方便连接,可应用于航空、航天等高速数据记录领域,具有广阔的应用前景。

[1] 吴 昊.高速大容量固态存储系统设计[D].西安电子科技大学硕士学位论文,2010.

[2] Nick Sawyer.Source-Synchronous Serialization and Deserialization[R].Xilinx Corporation:Application Note XAPP1064 (v1.1),2010.

[3] American National Standards Institute.American National Standard for Information Technology-AT Attachment with Packet Interface-6(ATA/ATAPI-6)[S].Revision 3b,2002.

[4] 张文沛,彭先蓉,徐 勇.基于SOPC的千兆以太网数据传输设计[J].仪器仪表用户,2010,(3):66~68.

[5] Anirudha Sarangi and Stephen MacMahon.Light Weight IP(lwIP)Application Examples[R].Xilinx Corporation:Application Note XAPP1026(v3.2),2012.

Design of High-speed Storage System Based on SATA Interface Solid State Hard Disk

Sun Haibo, Wang Xiaobin, Li Yamei

A design of high-speed storaged system base on SATA interface solid state hard disk(SSD)is introduced.The LVDS interface is adopted to receive the high-speed incoming data.Depending on IDE-SATA bridge chip JMH330S,the high speed read and write commands for SSD are performed.The 1000-M Ethernet is used as the control and download interface,and Microblaze runs the LwIP stack to achieve TCP/IP protocol.Test result proves that the storage system can sustain consecutive LVDS data stream as fast as 600Mb/s and the storage data is integrated and reliable.

SATA; LVDS; Solid state hard disk; Storage; 1000-M Ethernet

TN919

A

CN11-1780(2014)02-0048-05

孙海波 1987年生,硕士,工程师,研究方向为测量与通信技术。

2013-09-18 收修改稿日期:2013-09-26

王晓斌 1965年生,研究员,研究方向为计算机测量与控制。

李雅梅 1976年生,助理工程师,研究方向为数据采集与存储。