基于FPGA的铁路语音记录系统的设计与实现

唐 琳,黄建刚

(成都大学 电子信息工程学院,四川 成都 610106)

0 引 言

随着我国经济的不断发展,交通工具也在不断的更新,高铁动车的实际应用,使铁路交通技术又上了新的台阶,但列车种类的更新与行车速度的提高,对于列车运行的安全保障也提出了更高的要求.先进的交通工具需要先进的安全保障手段,在列车行进过程中的电调、列调、行调、机站、站段等各个部门之间相互的通话记录都必须存储保留,以利于日后安全防范和事故取证[1].铁路语音记录系统主要用于铁路上各个站点的语音调度监听.传统的铁路语音记录设备往往都是用普通单片机作为核心处理器处理监听的语音数据,因此具有存储容量小、在线播放实时性能差的特点.本研究提出一种基于FPGA的铁路语音记录系统,给出硬件和软件的设计方式,并详细介绍了系统的测试过程和测试结果.

1 系统总体方案

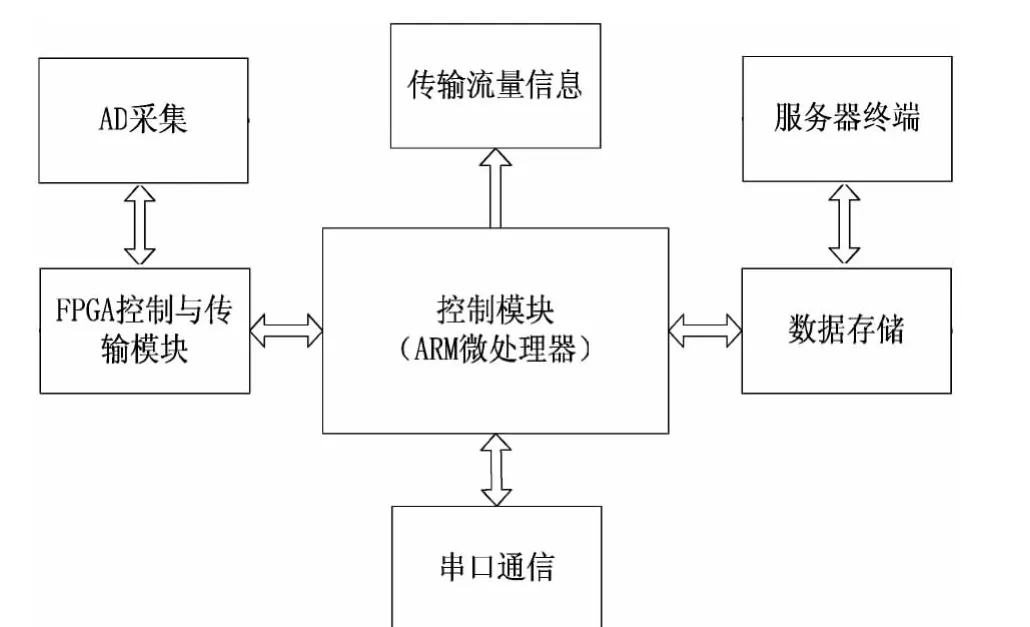

本系统采用ARM +FPGA +声卡的架构、硬件上各个功能模块独立运行与调试的设计方式,系统总体结构框图如图1 所示.

图1 系统总体结构框图

ARM 微处理器[2]是整个系统的核心,ARM 处理器芯片选用三星ARM9 内核的S3C2440,该芯片外设接口资源丰富,内部集成IIS 接口、SPI 接口、UART 接口、LCD触摸屏接口和以太网接口.其中,IIS 接口可直接与声卡芯片UDA1341 进行数据传递.UDA1341是飞利浦公司的一款专业级语音处理、语音编解码芯片,自带2 路AD/DA,内部集成了PGA(可编程增益调节器)和滤波器.本系统仅利用声卡的DA 来播放监听的语音信息,语音记录采用FPGA 控制AD1974 来实现,AD1974 是ADI 公司一款专业级的语音采集芯片,最多支持4 个通道同时录音.为了扩大语音记录系统的存储容量,增加了USB 接口和SD 卡接口作为本地存储设备.同时,主控模块上的以太网接口还可以实现本地存储信息的在线同步功能,使得互联网上任何一台权限设备都可以访问并获得该设备的语音记录信息.

2 硬件与软件设计

2.1 系统硬件设计

语音记录系统采用模块化的硬件设计,其包括主控模块、本地存储模块、电源模块和数据处理模块.其中:主控模块上完成语音信号的前端处理、语音编解码、和以太网通讯;本地存储模块主要包含SD 卡和USB 接口设备,与主控模块通过排线连接,除电源板之外,整个监听系统由核心板、主板、数据采集板以及转接板构成;电源模块完成220 AC 到5 V DC 的转换,由集成的电源转换模块实现,性能更加稳定可靠;数据处理模块以FPGA 和AD1974 为核心,完成数据采集、数据缓存和数据处理.

2.2 FPGA 的应用

在本系统中,数据采集板完成的功能包括语音监听信息的采集、处理和传输,其中采集部分由AD电路完成,数据处理和传输由FPGA 实现,此外,FPGA 还要负责与主板进行通信,对AD 进行配置[3-5].

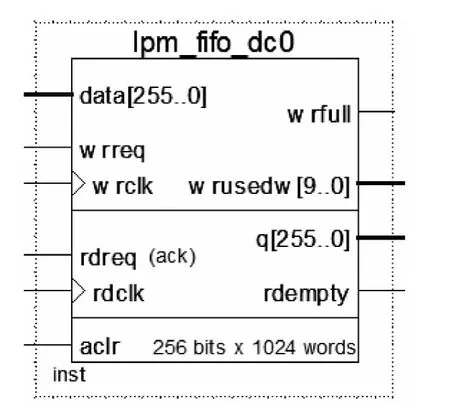

系统硬件设计的重点在于数据处理模块,加入FPGA 控制语音信息的采集并对采集到数据进行处理,这也是区别于传统语音记录系统的地方.数据处理模块核心芯片为 1 片 Altera IV 系列的EP4CE6C22C8N 和1 片ADI 公司的模数转换芯片AD1974,FPGA 控制AD1974 完成语音数据采集,并采用IP Core 实现一个128 KB 的DC FIFO 对采集到的数据进行缓存,加上IIS FIFO 就构成了语音记录系统的双缓冲池结构.DC FIFO 与微处理器之间通过SPI 总线进行数据传输,处理器作为主设备,当需要取数的时候给DC FIFO 一个使能信号,开启数据传输.当处理器不需要取数的时候,FIFO 丢弃溢出数据,确保微处理器取数时保留最新数据,DC FIFO如图2 所示.

图2 FPGA 构造的DC FIFO 示意图

2.3 系统软件设计

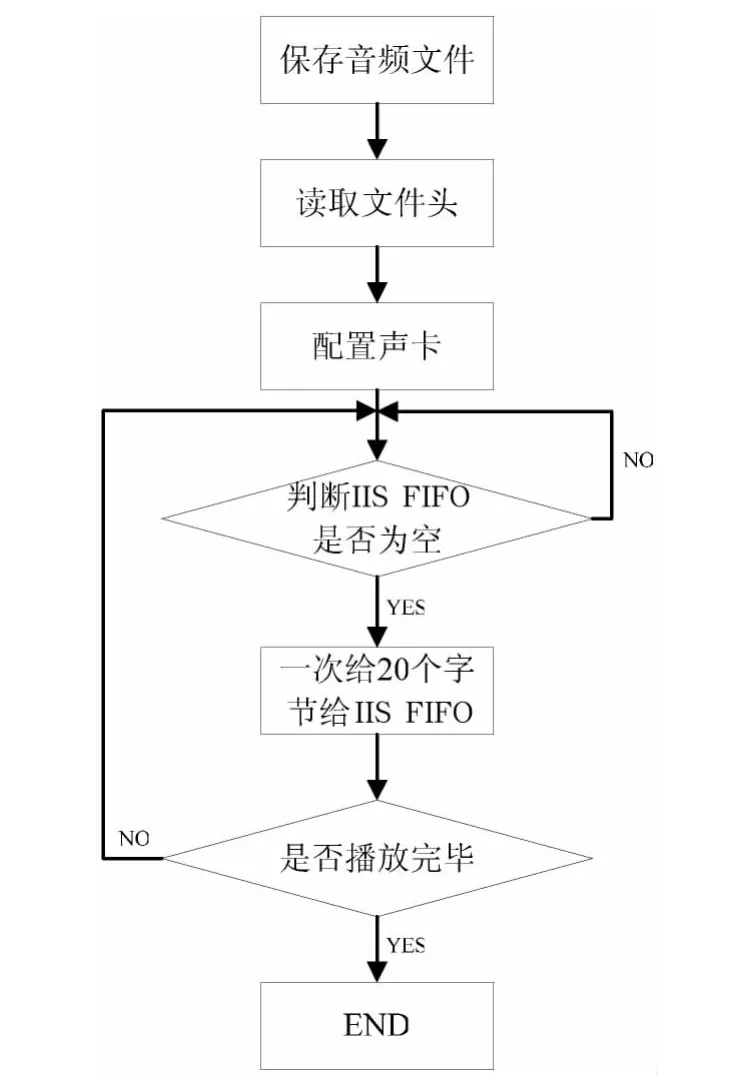

系统的软件在Linux 操作系统平台下进行编写,SPI、IIS、UART、L3 总线等接口的驱动可移植开源的代码,再将对Linux 内核进行剪裁并重新编译得到目标Image 文件烧写到ARM 微处理器的NAND FLASH 中运行[2].系统软件设计的流程如图3 所示.

图3 软件设计流程图

3 测 试

语音记录系统的测试包括多个方面的内容,本研究重点验证了对FPGA 部分电路的测试.

3.1 FPGA 测试平台

在对FPGA 的测试之前,必须保证测试工具的声卡和AD 芯片是可靠的,然后搭建测试平台对FPGA 的存储和缓冲功能进行测试.测试平台包括:主控模块,1 个;电源模块,1 个;数据采集模块,1 个;PC 机,2 台;铁路调度电话机,1 台;USB 线;USB 接口的串口线.

在本系统中,FPGA 构建了1 个256 bit* 1 024 words(内存大小为32 KB)的缓冲池,对AD 采集的数据进行缓冲,这种缓冲机制可以较好地改善在线播放性能.

3.2 FPGA 测试内容及结果

3.2.1 FIFO 溢出后的通信状态.

在本系统中构建的FIFO 容量为32 KB,声卡采样频率为8 kHz,量化位数为16 bit,假如1 次采集4个通道,1 s 的数据量为64 KB,相当于FIFO 每次最多可以存放0.5 s 的数据量.FIFO 装满溢出后的通信状态测试步骤为:让AD1974 不停的采集语音数据,并把数据存放到FIFO 中,当FIFO 的满标志FF第10 次被置位的时候,说明FIFO 已经溢出了10次,同时丢弃了约5 s 的数据,通过判断空标志EF的状态来从FIFO 中取数,每次只取1 帧数据(4 个通道8 个Byte).

测试结果显示,录音对象为一段10 s 的音频文件,播放出来为前面的一部分(约5 s)因溢出丢失,后面的5 s 音频播放正常.测试表明,FIFO 溢出后只是丢失溢出的数据,不会对后面取数造成影响.

3.2.2 FIFO 半满后的通信状态.

把AD 采集的数据打入FIFO,ARM 通过判断FIFO 的半满标志HF 来判断FIFO 里面的数是否达到16 KB,只要FIFO 里的数达到了16 KB 就把数取回来,每次取16 KB 存到ARM 缓存,因为ARM 运行的主频在500 MHz 左右,取16 KB 数据所耗时间几乎可以忽略,取完之后就等待下一个半满标志的到来.这样连续的取数10 s 后将ARM 缓存里的数据逐个给声卡的IIS FIFO,声卡就以8 kHz 的频率将采集到的数据播放出来.

测试结果表明,录音对象为一段10 s 的音频文件,播放出来完全正常,无任何数据丢失的情况.

3.2.3 系统在线实时播放功能验证.

前2 个实验验证了FPGA 的存储功能,实现了系统的本地回放.为了验证系统的在线实时播放功能,测试中把AD 采集到的语音数据存入FIFO,只要FIFO 不空,微处理器就开始取数,每次取1 帧数据传递给IIS FIFO,声卡按照录音时8 kHz 的频率、16 bit 的量化位数进行在线播放.在线播放的关键就在于FPGA FIFO 和IIS FIFO 的双缓冲池设计,该设计极大的减小了数据丢失的概率.只要录音和播放的速率、量化位数保持一致,主频为400 MHz 的处理器取数的时间是可以忽略不计的.

测试结果表明,系统在录音的同时可完成在线回放(延时为ms 级可以忽略不计).

4 结 论

本研究设计的铁路语音记录系统增加了FPGA器件,系统的可编程性能得到了提升,同时也提高了系统的存储容量并改善了在线播放的性能.模块化的设计方式使得系统运行更加稳定可靠,也为今后系统升级改造提供了方便.现场测试结果表明,本语音记录系统在精度、可靠性、功耗与稳定性等方面都优于以前的同类系统.

[1]唐琳.网络化嵌入式铁路调度监听系统的研究[D].成都:成都理工大学,2013.

[2]邵贝贝.嵌入式实时操作系统uCOS-II 版[M].北京:北京航空航天大学出版社,2003.

[3]吴小平.差压流量计的发展现状[J].常州工学院学报,2007,20(4):50-51.

[4]杨小军,陈保东,王剑桥,等.差压流量计的发展和展望[J].工业计量,2010,20(3):27-28.

[5]孙茂一,赵普俊.基于ARM 的科氏质量流量计的远程监控系统[J].中国测试,2014,40(2):63-67.