EtherCAT精确时钟同步技术的实现*

陈 灏,宋 宝,唐小琦

(华中科技大学 机械科学与工程学院,武汉 430074)

EtherCAT精确时钟同步技术的实现*

陈 灏,宋 宝,唐小琦

(华中科技大学 机械科学与工程学院,武汉 430074)

为了解决工业自动化领域中分布过程的同步动作的问题,首先基于EtherCAT的网络拓补结构,阐述了工业以太网EtherCAT的时钟同步机制,设计了分布式时钟的同步算法、仿真程序及具体实现过程,进行同步误差仿真分析,然后通过搭建基于ARM和FPGA的硬件平台对同步效果进行测试,实验结果证明EtherCAT分布式时钟能够达到小于100ns的同步精度,实现了从站之间的同步,从而满足了高速高精加工的需求。

EtherCAT ;分布式时钟;同步

0 引言

随着数控机床高速高精加工的迅速发展,现场总线技术在数控系统中的运用越来越广泛。其中,EtherCAT是一种应用于工业自动化领域的实时工业以太网技术,它具有广泛的适用性,完全符合以太网标准,可以与其他以太网设备及协议并存于同一总线,从而最大化利用以太网宽带进行用户数据传输[1-2,9-10]。同时,EtherCAT小于100μs数据的刷新周期使其可以用于伺服技术中底层的闭环控制。EtherCAT还具有很好的同步性能,利用“分布时钟”机制可以实现各从站节点之间小于1μs的时钟同步精度,这在要求分布系统同时工作的场合显得极为重要。

1 EtherCAT技术原理与特征

EtherCAT充分利用了以太网的全双工特性,使用主从模式介质访问控制。如图1所示,利用单线型的拓补结构,主站发送以太网帧给各从站,从站可以直接处理接收的报文,并从报文中提取或插入相关的用户数据,然后将该报文传输到下一个EtherCAT从站,最后一个EtherCAT从站发回经过完全处理的报文,并由第一个从站作为相应报文将其发送给控制单元。

图1 EtherCAT运行原理

同一EtherCAT数据帧中可以嵌入多种类型的子报文,达到较高的数据帧利用率。每个子报文有其独特的命令字和寻址方式。EtherCAT实行动态数据处理机制,从站直接读取主站数据帧中的数据块或者改变数据帧中的一部分数据,这样所引入的总延时小于100ns。

支持分布时钟的从站称为DC从站,一般内嵌一个周期10ns的本地时钟[3]。分布时钟机制可以使所有EtherCAT设备使用相同的系统时间,从而控制各设备任务的同步执行。从站设备可以根据同步的系统时间产生同步信号,可以为输入事件产生精确的时间标记,产生同步信号,用于中断控制或触发数字量输入输出。

2 EtherCAT分布式时钟的同步算法

分布时钟机制使所有的从站都同步于一个参考时钟。主站连接的第一个具有分布时钟功能的从站作为参考时钟,以参考时钟来同步其他设备和主站时钟。

系统启动时,各从站的本地时钟tlocal(n)和参考时钟tsys_ref(n)之间有一定的差异,称为时钟初始偏移量Toffset(n)。在运行过程中,由于各从站使用的晶振等原因,它们的计时周期会有微小差别,称为时钟漂移。数据帧在各个从站之间传播时的延时称为传输延时Tdelay(n),包括物理层和链路层的延时。在分布时钟机制中,这些因素都必须进行补偿,使得补偿后的本地系统时间tsys_local(n)和系统时间达到同步,从而达到整个系统的同步[1-2]。

EtherCAT时钟同步算法包含两个部分,分别是测量和计算传输延时和时钟初始偏移量,以及时钟同步补偿及动态补偿[4-5]。

传输延时和时钟初始偏移量的测量原理如图2所示,假设tlocal(n)>tsys_ref,它们的关系由下式确定:

tlocal(n)=tsys_ref+Toffset(n)

(1)

图2 传输延时和时钟初始偏移量测量原理

主站发送一个广播写命令数据帧,数据帧到达每个从站后每个从站设备保存每个端口接收到以太网帧前导符的第一位的时刻。数据帧到达参考时钟从站时tsys_ref为T1时刻,到达从站n时从时钟本地时钟时刻为T2(n),可以建立如下关系:

Toffset(n)=T2(n)-T1-Tdelay(n)

(2)

数据帧经过所有的从站后返回,到达从站n时本地时钟时刻为T3(n),到达参考时钟从站tsys_ref的时刻为T4;假设线缆延时均匀,所有从站设备的处理和转发的延时一样,则得出从站n到参考时钟的传输延时:

在冬天与春天之间那些含混不清的日子里,乱雨迁延着冬日的寒意。母亲死后,一杭情绪一直比较低落。如果不是为了所谓的真相,也许他不会离开病中的母亲,母亲可能就不会出事。而自己拼命得到的,原来是一个错误的真相。核桃脸被人收买了。而这个人不是夏冰,夏冰恰恰是被他诬陷的对象。所以,夏冰才想杀他。一定还有一个人,躲在暗中,操纵一切。

Tdelay(n)=[(T4-T1)-(T3(n)-T2(n))]/2

(3)

主站读取各个从站所保存的数据帧到达的时刻,根据式(3)计算各个从站的传输延时Tdelay(n),并写入到各个从站中;为了得到准确的传输延时,主站可以多次测量,然后求平均值;在初始化后的周期运行过程中也可以随时测量传输延时,以补偿环境变化对传输延时的影响。

保持本地时钟的自由运行,从站利用Toffset(n)实现时钟同步。每个DC从站使用自己的本地时间tlocal(n)和本地偏移量Toffset(n)通过公式(4)计算本地系统时间,用来产生同步信号和锁存信号时间标记,供从站微处理器使用。

tsys_local(n)=tlocal(n)-Toffset(n)

(4)

在测得传输延时和时钟偏移量后,主站发送数据报文从参考时钟从站读取系统时间tsys_ref并写入之后的每个从站设备中。从站根据得到的tsys_ref和之前保存于每个从站中的Toffset(n)和Tdelay(n),计算出本地时钟漂移量Δt:

Δt=tsys_local(n)-Tdelay(n)-tsys_ref

=tlocal(n)-Toffset(n)-Tdelay(n)-tsys_ref

(5)

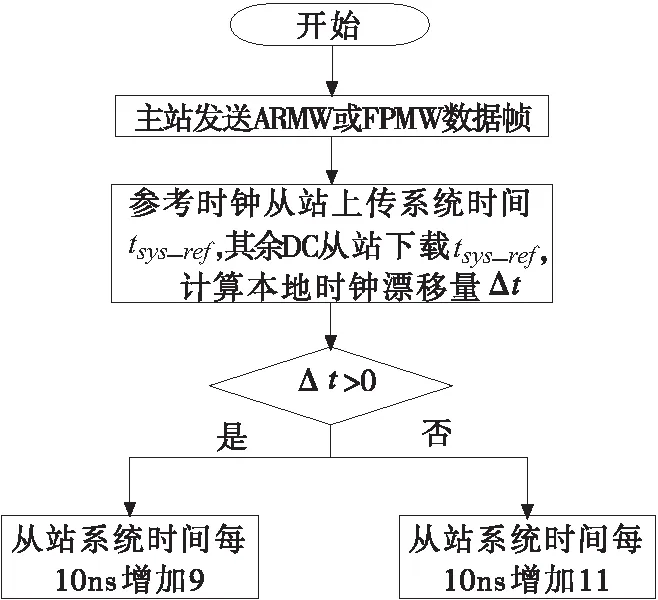

从站根据Δt的正负来调整本地时钟,如果Δt大于0,表示本地时钟运行比参考时钟快,必须减慢运行,则ESC控制本地时间每10ns增加9;如果Δt小于0,表示本地时钟运行比参考时钟慢,必须加快运行,则ESC控制本地时间每10ns增加11,以实现时钟漂移补偿[1,4,6]。

3 EtherCAT分布式时钟的实现方式

图3 EtherCAT分布时钟实施步骤

分布时钟的功能通过读写寄存器来实现[7]。如图3所示,在发送从站初始化命令前,主站首先发送顺序寻址命令APRD读所有从站的特征信息寄存器0x0008~0x0009,以此确定哪些从站支持分布时钟,然后读取数据链路状态寄存器0x0110~0x0111,根据其中的端口状态判断正在使用的端口,从而获得网络拓补结构。主站发送广播写命令BWR,写所有的从站端口0的接收时间寄存器,每个从站在接收到数据帧第一个前导位时,保存本地时钟时刻到寄存器0x0900~0x090F,主站在下一个通信周期读取这些值。

假设只使用端口0和端口1,则参考时钟从站寄存器0x0900~0x0903中保存了数据帧到达端口0时的参考时钟的时刻T1,0x0904~0x0907中保存了数据帧返回时到达端口1时的参考时钟的时刻T4;从站n的寄存器0x0900~0x0903中保存了数据帧到达从站n端口0时的参考时钟的时刻T2(n),0x0904 ~0x0907中保存了数据帧到达从站n端口1时的参考时钟的时刻T3(n)。

图4 分布时钟的漂移补偿步骤

4 ARM和FPGA的EtherCAT分布式时钟测试系统总体结构

为了验证EtherCAT分布式时钟的同步效果,本文设计了一个总线式的数控系统,它基于嵌入式x86工控机实现,主要包括EtherCAT主站系统、EtherCAT从站和人机交互系统三大部分[2]。其硬件体系结构如图5所示,嵌入式 x86 工业 PC,实现数控系统的各项功能,并负责对整个系统进行管理,实现友好的人机交互功能。EtherCAT主站协议卡通过 PCI 总线与嵌入式 x86 工业 PC 进行数据交互。

图5 EtherCAT硬件体系结构

EtherCAT主站协议卡使用ARM来实现EtherCAT通信的所有功能,如EtherCAT数据帧的封装和解包、状态机转换和时钟同步等。为实现ARM与工控机之间的数据交换,利用FPGA实现PCI总线接口和一个双口RAM。FPGA还实现了SPI总线接口的功能,使得主站和控制面板进行通信。EtherCAT从站使用STM32+FPGA的方式来实现EtherCAT从站通信的所有功能,其中FPGA实现EtherCAT链路层协议,ARM一方面实现总线驱动功能以及EtherCAT从站的应用层协议,另一方面实现运动控制功能。

5 实验结果及结论

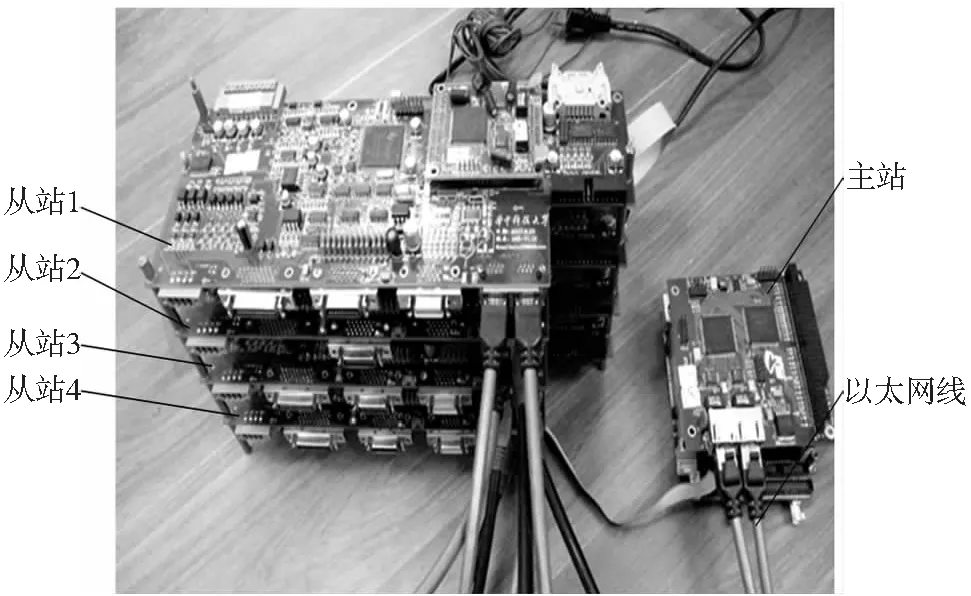

本文的测试平台使用了1个主站和4个从站,如图6所示,主站连接的第一个从站(1号从站)为参考时钟,各个从站以规定的周期同步输出中断信号。用双通道示波器的两个通道同时捕捉1号从站和4号从站的中断输出信号,从而得出各轴间的同步性能。

图6 分布时钟测试平台

同步前后时钟偏差如图7所示,可以看出,4号从站和1号从站同步前时钟偏差为400ns,同步后为60ns。经过测试和对比可以得出结论,EtherCAT分布时钟的同步精度达到或超过了IEEE 1588实施水平。在高速加工时,100ns同步误差的加工误差仅为0.3μm左右,满足了高速高精的加工要求。

图7 中断信号的示波器输出(前图为同步前,后图为同步后)

6 结束语

本文在基于ARM和FPGA的硬件平台上,采用了EtherCAT的分布时钟同步算法,在主站初始化阶段测量并计算出参考时钟从站到各个DC从站的时间延时和初始时钟偏移量,并将这两个参数写入各个从站的寄存器中,然后在下一个周期里,读取参考时钟的系统时间并写入其他DC从站的相应寄存器中,各个DC从站根据参考时钟的系统时间、从站延时和初始时钟偏移量来计算本地时钟误差,并根据其大小对本地系统时间进行调整,从而保证本地系统时间和参考时钟系统时间的同步,达到各个从站之间较好的同步性能。

[1] 郇极,刘艳强.工业以太网现场总线EtherCAT驱动程序设计及应用[M].北京航空航天大学出版社,2010.

[2] 张勇.EtherCAT总线接口在数控系统中的实现[D].武汉:华中科技大学,2011.

[3] Gianluca Cena,Adriano Valenzano. Evaluation of EtherCAT Distributed Clock Performance[J]. IEEE TRANSACTIONS INDUSTRIAL INFORMATICS,2012,8(1):20-29.

[4] G. Cena, I. C. Bertolotti, S. Scanzio, A. Valenzano. On the Accuracy of the Distributed Clock Mechanism in EtherCAT[C]. IEEE International Workshop on Factory Communication Systems, 2010:43-52.

[5] Jae Chol Lee, Seong Jin, Yong Han Jeon, Jae Wook Jeon. Dynamic drift compensation for the Distributed Clock in EtherCAT[C]. International Conference on Robotics and Biomimetics, 2009:1872-1876.

[6] 刘明哲,徐皑冬,赵伟.基于IEEE1588的时钟同步算法软件实现[J].仪器仪表学报,2006,27(6):2009-2011.

[7] ETG,EtherCAT_Introduction[EB/OL].http://www.ethercat.org.cn/pdf/cn/EtherCAT_Introduction.pdf, 2007.2:5.

[8] 汪雅楠,谭南林.EtherCAT时钟同步的误差仿真分析[J].计算机应用,2011,7(30) :22-26.

[9] 郑慧宁.现场总线技术[J].宁夏机械,2005(12):4-6.

[10] 吴瑞金,齐然,刘海伟.现场总线的现状及发展[J].通用机械,2005(2):39-43.

(编辑 李秀敏)

Implementation of EtherCAT Precise Clock Synchronization

CHEN Hao,SONG Bao,TANG Xiao-qi

(School of Mechanical Science and Engineering, HuaZhong University of Science and Technology, Wuhan 430074, China)

To solve the synchronization action of the distributed process in the field of industrial automation, based on the topology structure of EtherCAT, this paper firstly elaborates the mechanism of the EtherCAT clock synchronization, and designs the clock synchronization algorithm, the simulation program and the specific realization process of the distributed clock, in order to carry on simulation and analysis of the synchronization error. Furthermore, a platform constituted by ARM and FPGA was built to assess the synchronization effect. The experimental results show that the EtherCAT distributed clock can achieve an accuracy of less than one hundred nanosecond, which realizes the synchronization between the slave sites and meets the need of high speed and high precision in machining.

EtherCAT; distributed clock; synchronization

1001-2265(2014)05-0069-04

10.13462/j.cnki.mmtamt.2014.05.018

2013-09-02

"高档数控机床与基础制造装备"科技重大专项(2012ZX04001012);"高档数控机床与基础制造装备"科技重大专项(2012ZX04001041);高等学校博士学科点专项科研基金(20090142120035)

陈灏(1989—),男,湖北随州人,华中科技大学硕士研究生,主要研究方向为数控技术、现场总线技术,(E-mail)chenhaosjy@163.com。

TH165;TG65

A