一种用于CMOS图像传感器的10位高速列级ADC

姚素英,徐文静,高 静,聂凯明,徐江涛

一种用于CMOS图像传感器的10位高速列级ADC

姚素英,徐文静,高 静,聂凯明,徐江涛

(天津大学电子信息工程学院,天津 300072)

提出了一种适用于高速小尺寸像素的列级ADC,该ADC采用单斜ADC(single-slope ADC,SS ADC)与逐次逼近ADC(successive-approximation ADC,SA ADC)相结合的方式在提高模数转换速度的同时减小了芯片面积. SS ADC实现5位粗量化,SA ADC实现5位细量化,SA ADC中5位分段电容DAC的桥接电容采用单位电容并利用区间交叠方式实现了误差校正.采用GSMC 0.18,µm 1P4M标准CMOS工艺对电路进行设计,仿真结果表明:所提出的列级ADC在167,kHz/s采样率和3.3,V电源电压下,有效位数9.81,每列功耗0.132,mW,速度比传统SS ADC提高了22倍.

CMOS图像传感器;列级ADC;单斜ADC;逐次逼近ADC

CMOS图像传感器以其功耗低、可靠性高、体积小、价格便宜等特点,已广泛应用于图像采集领域.目前,应用在CMOS图像传感器中的ADC有3种类型:像素级、列级和芯片级.与芯片级ADC相比,列级ADC对速度要求较低,降低了设计难度;与像素级ADC相比,列级ADC由像素内转移到像素阵列外,提高了填充因子,从而提高了图像传感器的光敏感度[1-2].

列级ADC常见结构有3种:单斜ADC(singleslope ADC,SS ADC)[3]、循环ADC(cyclic ADC)和逐次逼近ADC(successive-approximation ADC,SA ADC).列级SS ADC结构简单,每列只需一个比较器和存储器,占用芯片面积小,适用于小尺寸像素,但转换时间长,N位SS ADC需2N个时钟周期(Tclock)完成一次转换,因此在高速场合的使用受到限限制.文献[1]中的SS ADC采用同一斜坡两步转换方式提高速度,但引入了列级噪声;文献[4]中的SS ADC采用多斜坡方式将速度提高3.3倍,但其斜坡个数是粗量化位数2的指数幂,随着粗量化位数的增加,斜坡个数增加,版图面积和功耗增加,限制了速度的提升.列级SA ADC转换速度快,N位SA ADC转换时间为NTclock,但每一列都需一个完整的ADC,每一个ADC都包含一个N位DAC,由于N位DAC占用芯片面积大,导致整个芯片的版图面积大,因此在小尺寸像素使用受限.文献[5]中的SA ADC采用所有列共用二分参考电压方式减小版图面积,但降低了有效位数.文献[6]中的SA ADC采用7位DAC两步转换方式实现了14位精度,但其DAC中的桥接电容采用分数电容,匹配精度不高,并且无法实现低位误差校正.列级cyclic ADC转换速度快,N位cyclic ADC转换时间同样为NTclock,但其功耗较大,原因在于cyclic ADC电路核心为乘2电路,随着量化位数的增加,乘2电路精度提高,这就要求高精度的电容匹配和高增益运放,从而增加了设计难度和功耗[7-8].

综上所述,SS ADC速度慢,SA ADC版图面积大,cyclic ADC功耗高,因此如何实现适用于高速小尺寸像素的列级ADC成为设计难点之一.笔者设计的10位列级ADC将SS ADC与SA ADC相结合,即SS-SA ADC,其中SS ADC实现5位粗量化,SA ADC实现5位细量化,两种ADC共用比较器,并利用区间交叠方式实现了误差校正.该SS-SA ADC的速度比传统的SS ADC提高了22倍,每列版图面积比传统的SA ADC小,适用于高速小尺寸像素.

1 10位SS-SA ADC设计优化

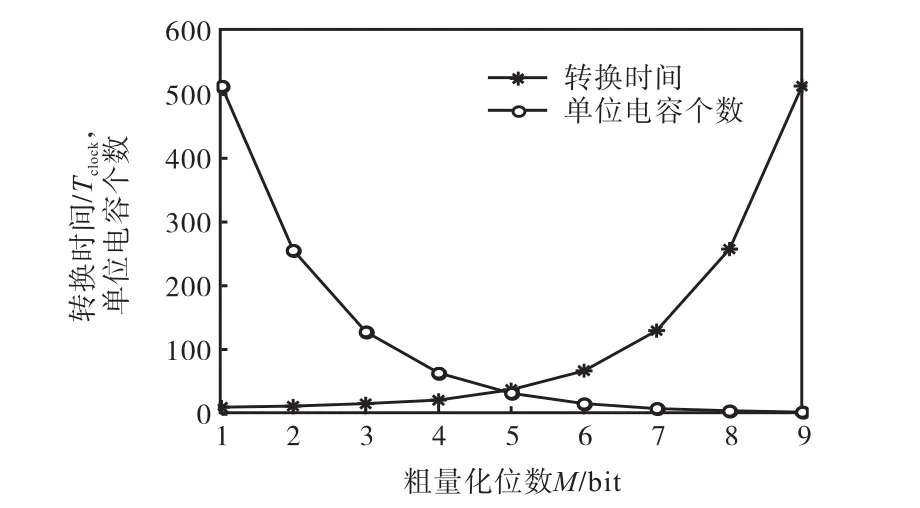

设计中首先需确定粗细量化的位数.N位SS ADC转换时间为2NTclock;N位SA ADC转换时间为NTclock,每列需一个N位DAC,采用二进制电容结构的N位DAC需2N个单位电容.假设10位SS-SA ADC中SS ADC负责M(0<M<10)位粗量化,SA ADC负责10-M位细量化,则10位SS-SA ADC完成一次转换所需时间T为

每列需一个10-M位DAC,采用二进制电容结构的10-M位DAC所需单位电容个数K为

图1所示为M的取值对10位SS-SA ADC转换时间和每列所需单位电容个数的影响,可见M=5,即SS ADC负责5位粗量化,SA ADC负责5位细量化,可达到速度与面积的最佳折中.

图1 10位SS-SA ADC中粗细量化位数的优化Fig.1Coarse and fine resolution optimization of 10,bit SS-SA ADC

2 10位SS-SA ADC电路实现

2.1 整体结构

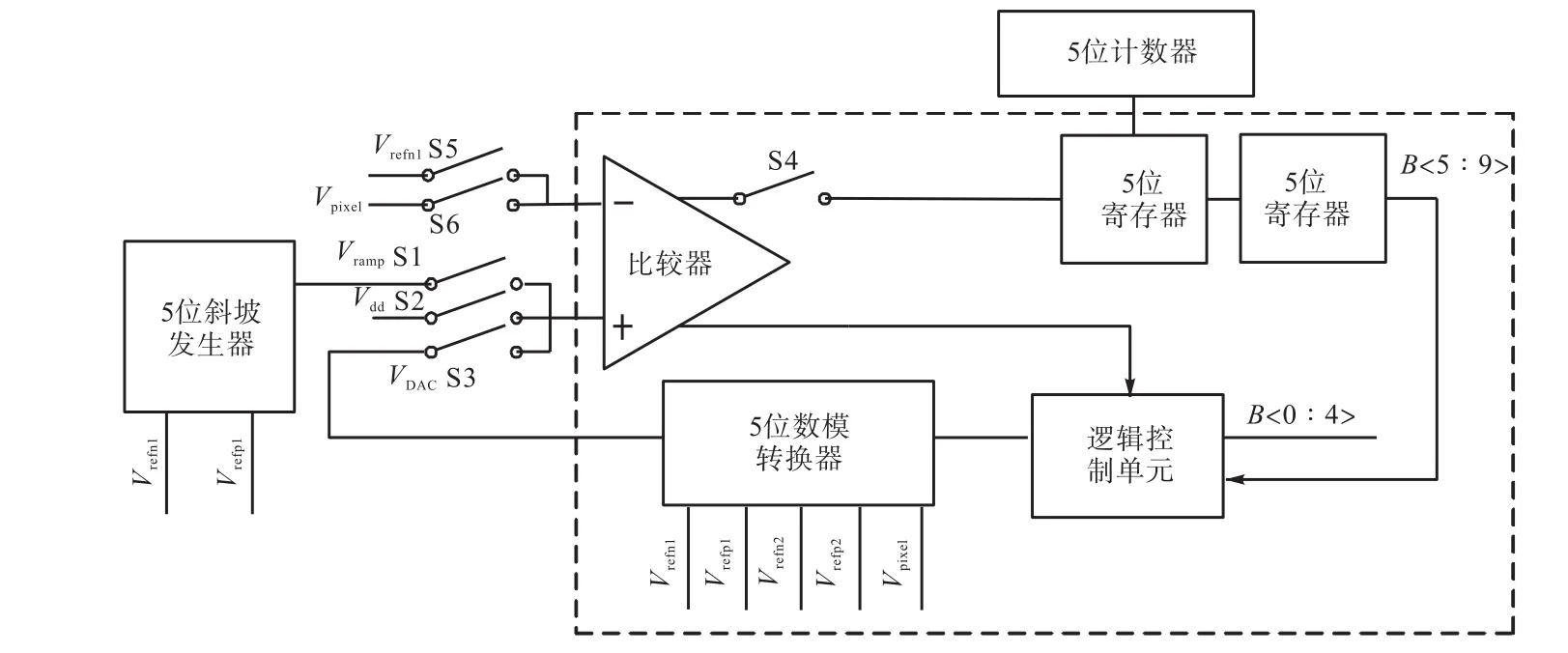

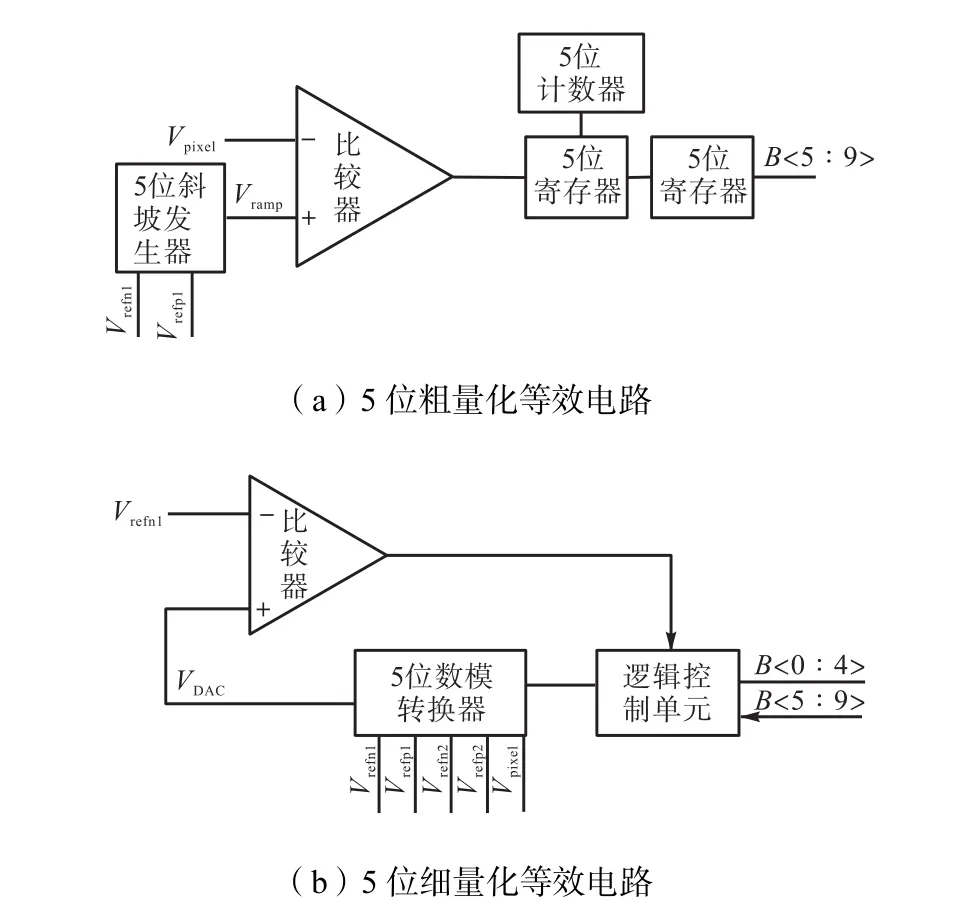

笔者提出的10位SS-SA ADC电路整体结构如图2所示,其中虚线框内部电路是每列必需电路,虚线框外部电路是每列共享电路.该ADC量化范围是Vrefn1~Vrefp1,Vpixel表示需量化的像素输出值,Vramp为斜坡输出值,Vdd为电源电压,VDAC为5位DAC的输出值,Vrefn2和Vrefp2为另一组参考电压,B<0∶4>、B<5∶9>为量化的10位码值.该ADC在工作时分为两个阶段,工作时序及工作波形如图3所示,当开关S1、S4、S6闭合,开关S2、S3、S5断开时,整体电路的等效结构如图4(a)所示,此时电路作为一个5位SS ADC工作,斜坡输出值和像素值直接比较,进行5位粗量化、5位粗量化结束后将开关S1断开,开关S2闭合,以防止输入信号超出斜坡量程导致比较器不翻转,之后将粗量化得到的高5位码值保存;当开关S3、S5闭合,开关S1、S2、S4、S6断开,整体电路的等效结构如图4(b)所示,此时电路作为一个5位SA ADC工作,像素值被5位DAC采样,5位DAC的输出值和低电平基准比较,进行5位细量化,从而得到低5位码值.转换结束后高5位码值和低5位码值一同输出.

图2 10位SS-SA ADC电路整体结构Fig.2 Structure diagram of the proposed 10,bit SS-SA ADC

图3 SS-SA ADC的工作时序及工作波形Fig.3 Timing diagram and working waveform of the proposed SS-SA ADC

图4 SS-SA ADC分步工作等效电路Fig.4 Equivalent diagram of step working of the proposed SS-SA ADC

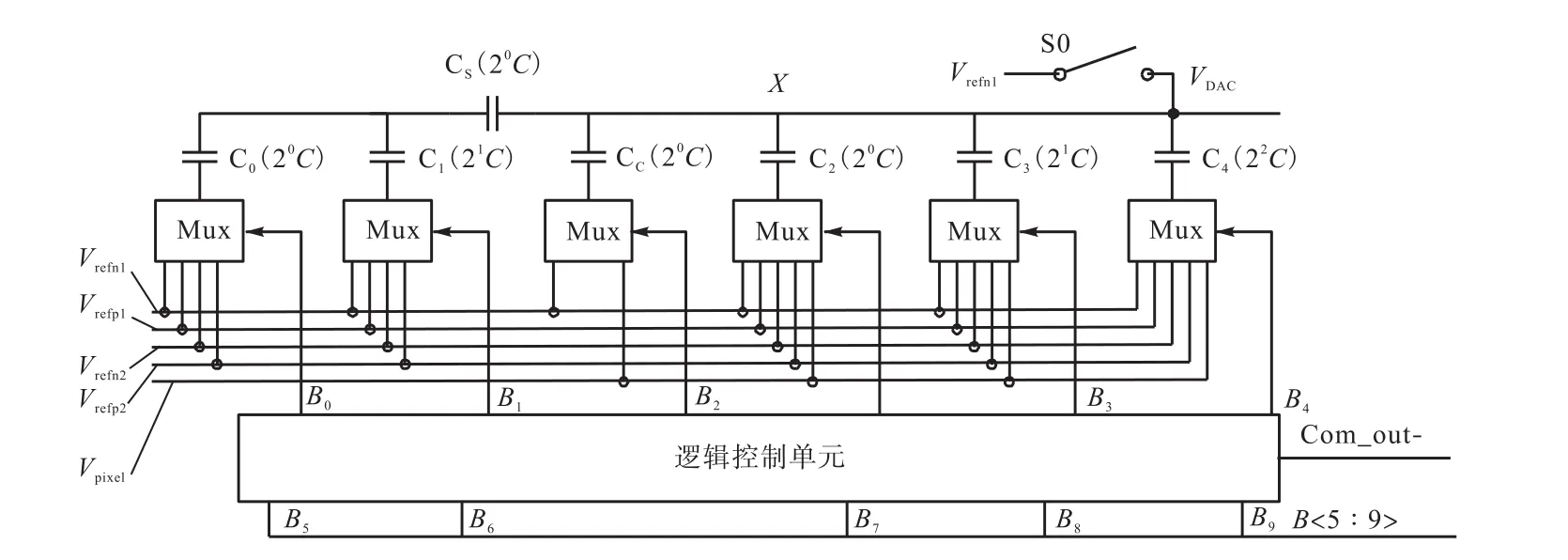

2.2 细量化SA ADC中5位DAC和逻辑控制单元

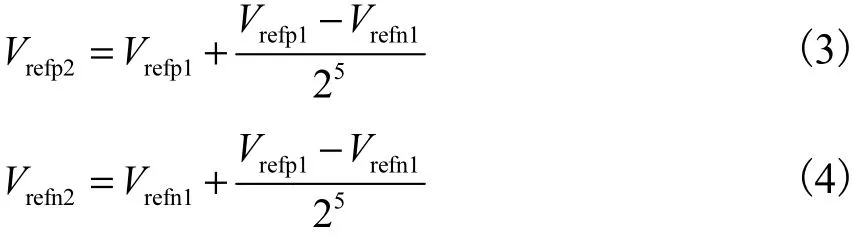

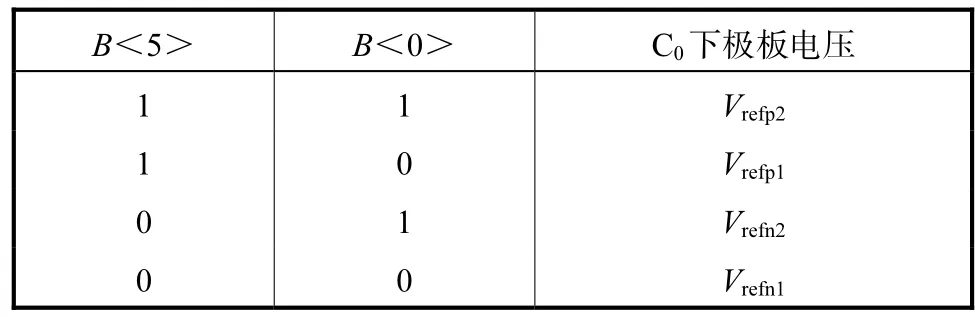

细量化SA ADC中5位DAC和逻辑控制单元的电路结构如图5所示,主体结构与两步SA ADC[6]类似,但桥接电容CS采用单位电容,补偿电容CC连接在分段电容阵列的高位输出.此结构的整个工作过程分为3个阶段:采样、保持和电荷再分配. 采样阶段,CC、C2、C3、C4的下极板接Vpixel,C0、C1的下极板接低电平Vrefn1,同时开关S0闭合,使DAC的高位输出端接低电平Vrefn1;保持阶段,开关S0断开,同时CC、C0、C1、C2、C3、C4下极板均接低电平Vrefn1;电荷再分配阶段,CC下极板始终接Vrefn1,C0、C1、C2、C3、C4下极板电压由B<0∶4>和B<5∶9>共同决定,以C0下极板电压为例,如表1所示,其中

表1 5位DAC中C0下极板电压Tab.1 Voltages of C0bottom plate in 5,bit DAC

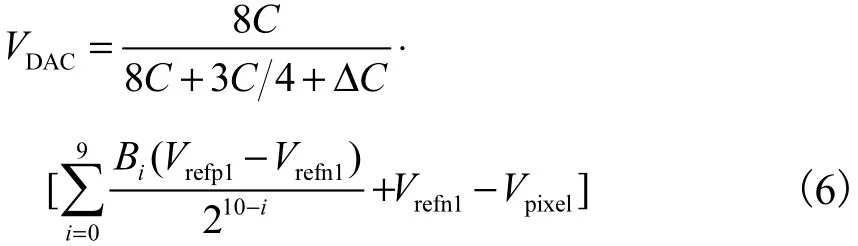

同理可得C1、C2、C3、C4下极板电压取值,该5位分段电容DAC输出为

式中C为单位电容.

该结构有2个优点.

(1) 桥接电容采用单位电容,提高了此电容与其他电容的匹配度,从而提高了ADC的精度.

(2) 该结构可屏蔽DAC高位输出端(X点)寄生电容的影响,若X点的寄生电容为ΔC,则该5位分段电容DAC输出为可见寄生电容只影响系数的大小,对ADC的精度没有影响,因此图2中S1、S2、S3和比较器的寄生电容对SS-SA ADC的精度无影响.

图5 5位DAC和逻辑控制单元的电路结构Fig.5 Structure diagram of 5,bit DAC and control logic

2.3 误差校正

上述10位SS-SA ADC中,SS ADC实现5位粗量化,SA ADC实现5位细量化,但当式(3)和式(4)中Vrefp2和Vrefn2出现偏差时,5位细量化的转换区间相应会出现偏差,进而细量化出的低5位码值出现偏差,从而降低了SS-SA ADC的整体精度.当Vrefp2和Vrefn2偏低时,细量化区间出现负向偏移,此偏移如图6(a)所示,从而导致低5位码值整体出现正向偏移,低5位码中部分最小码值不会出现;当Vrefp2和Vrefn2偏高时,细量化区间出现正向偏移,如图6(b)所示,从而导致低5位码值整体出现负向偏移,低5位码中部分最大码值不会出现,因此细量化时需进行误差校正.误差校正电路如图7所示,即将图5中的5位DAC和逻辑控制单元模块替换为6位DAC和逻辑控制单元模块,Vrefp2和Vrefn2替换为Vrefp3和Vrefn3,D0~D5为低6位码值,其中

图6 参考电压出现偏差时SS-SA ADC的工作波形Fig.6Working waveforms of the proposed SS-SA ADC when the reference voltage has offset

图7 6位DAC和逻辑控制单元的电路结构Fig.7 Structure diagram of 6,bit DAC and control logic

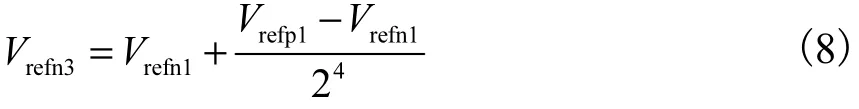

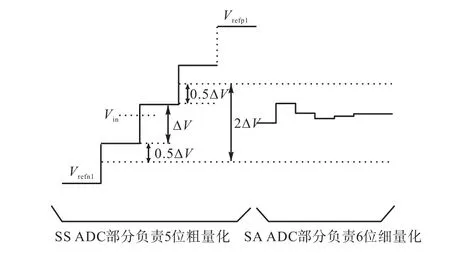

误差校正工作原理如图8所示.输入信号Vpixel接入SS-SA ADC,首先由SS ADC进行5位粗量化,转换码值为B<5∶9>;接着由图7中SA ADC进行6位细量化,高5位码值B<5∶9>决定细量化区间,Vrefp3和Vrefn3的引入将6位细量化区间上下均扩展5位细量化区间的1/2,相当于5位细量化区间的2倍.采用此方法,即使参考电压出现图6所示偏差,也可将细量化出的低位码值信息全部保留,只需进行简单的数学运算即可将高5位码值和低6位码值通过数字电路转换成10位码值输出.

图8 带有误差校正的10位SS-SA ADC工作波形Fig.8 Working waveform of 10 bit SS-SA ADC with error correction

3 仿真结果与分析

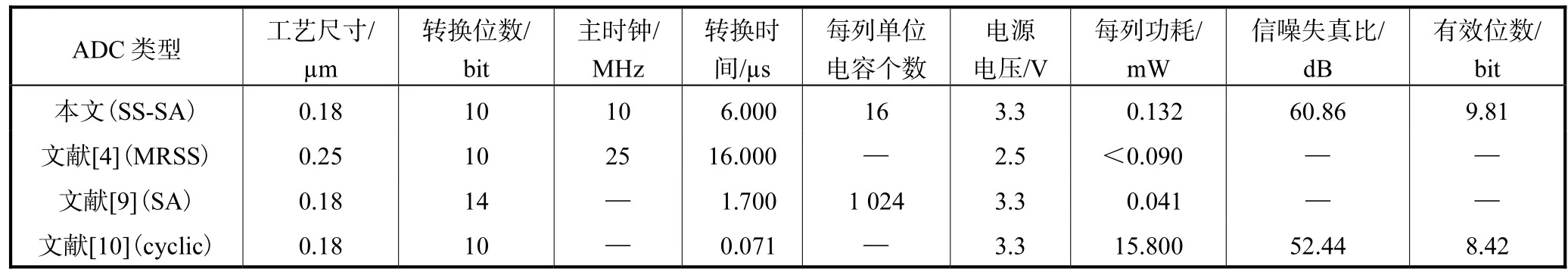

采用GSMC 0.18,µm 1P4M标准CMOS工艺对电路进行仿真,仿真结果表明:本文提出的10位SSSA ADC在167,kHz/s采样率和3.3,V电源电压下,有效位数9.81,每列功耗0.132,mW.通过仿真得到的10位SS-SA ADC整体性能指标与文献[4,9-10]的对比如表2所示.实际制作过程中由于存在工艺偏差,电容匹配精度下降,使得细量化SA ADC中DAC精度下降,从而会导致整体ADC精度有所降低.

3.1 速 度

10位SS-SA ADC的转换速度是多斜坡SS ADC[4]的6.7倍,由于多斜坡SS ADC[4]的转换速度是传统SS ADC的3.3倍,因此10位SS-SA ADC的转换速度是传统SS ADC的22倍.

3.2 版图面积

有误差校正的10位SS-SA ADC每列需1个比较器、1个开关、寄存器、1个6位DAC及逻辑控制电路,6位DAC采用分段电容结构需16个单位电容,当单位电容取为100,fF时,每列版图面积约15,µm×1,266,µm.文献[9]中14位SA ADC每列包含1个14位DAC,14位DAC采用RC结合方式需1,024个单位电容.

表2 10位SS -SA ADC整体性能与参考文献的对比Tab.2 Comparison between previous works and the proposed 10,bit SS-SA ADC

3.3 功 耗

ADC功耗比较采用FOM指数[9],FOM指数越大表示功耗越大.

由式(9)计算得10位SS-SA ADC的FOM指数为文献[10]中cyclic ADC FOM指数的1/3.

3.4 精 度

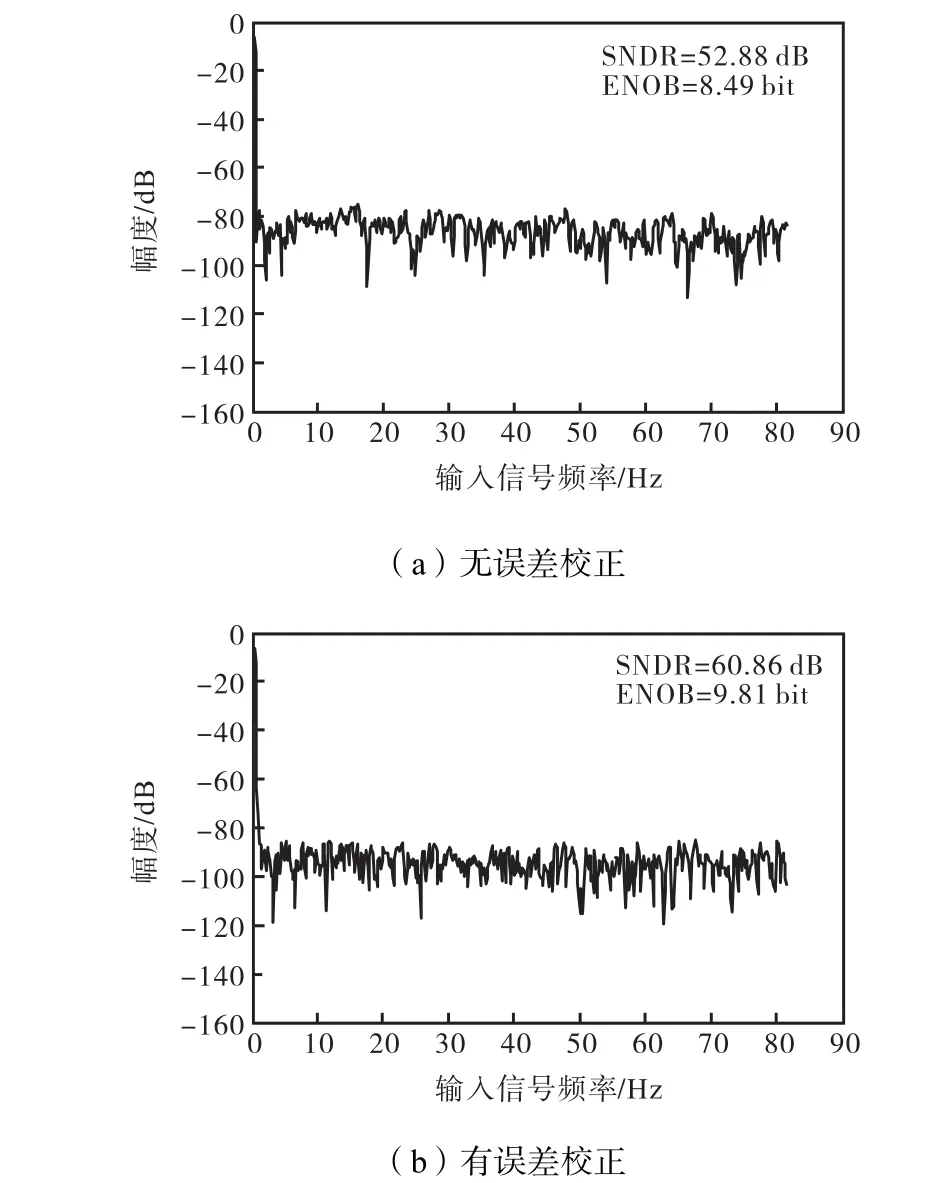

图9为10位SS-SA ADC FFT分析结果(ENOB为有效位数).采用输入范围为1.2~2.8,V、频率为163,Hz的正弦信号对ADC进行动态仿真,并利用Matlab软件对仿真结果进行FFT分析.其中,图9(a)为无误差校正的10位SS-SA ADC FFT分析结果,图9(b)为有误差校正的10位SS-SA ADC FFT分析结果,可见误差校正将10位SS-SA ADC的信噪失真比(SNDR)由52.88,dB提升为60.86,dB.

综上所述,10位列级SS-SA ADC速度与传统的SS ADC相比提高了22倍,每列版图面积比传统的SA ADC小,功耗与cyclic ADC相比降低,适合用于高速小尺寸像素的CMOS图像传感器.

图9 10位SS -SA ADC FFT分析结果Fig.9 FFT analysis results of 10 bit SS-SA ADC

4 结 语

笔者设计的10位列级SS-SA ADC将SS ADC与SA ADC结合,SS ADC实现5位粗量化,SA ADC实现5位细量化,SA ADC中5位分段电容DAC的桥接电容采用单位电容实现,提高了细量化的精度,并利用区间交叠方式实现了误差校正.采用SS-SA ADC,在满足高精度的同时,速度比传统的SS ADC提高了22倍,每列版图面积与传统的SA ADC相比减小,因此列级SS-SA ADC适用于高速小尺寸像素的CMOS图像传感器.

[1] Lim Seunghyun,Lee Jeonghwan,Kim Dongsoo,et al. A high-speed CMOS image sensor with columnparallel two-step single-slope ADCs[J]. IEEE Transac tions on Electron Device,2009,56(3):393-398.

[2] Mendis S K. CMOS active pixel image sensors for highly integrated imaging system[J]. IEEE Journal of Solid-State Circuits,1997,32(2):187-197.

[3] 高 静,姚素英,徐江涛. 高速列并行 10 位模数转换电路的设计[J]. 天津大学学报,2010,43(6):439-494.

Gao Jing,Yao Suying,Xu Jiangtao. Design of high speed column-parallel 10-bit ADC[J]. Journal of Tianjin University,2010,43(6):439-494(in Chinese).

[4] Snoeij M F,Theuwissen A J P,Makinwa K A A,et al. Multiple-ramp column -parallel ADC architectures for CMOS image sensors[J]. IEEE Journal of Solid-State Circuits,2007,42(12):2968-2976.

[5] Lee Jeonghwan,Han Gunhee. A/D converter using iterative divide-by-two reference for CMOS image sensor[C] // International SoC Design Conference. USA,2008:35-36.

[6] Shin M S,Kwon O K. 14-bit two-step successive approximation ADC with calibration circuit for highresolution CMOS imagers[J]. Electronics Letters,2011,47(14):790-791.

[7] Furuta Masanori,Nishikawa Yukinari,Inoue Toru,et al. A high-speed,high-sensitivity digital CMOS image sensor with a global shutter and 12-bit column-parallel cyclic A/D[J]. IEEE Journal of Solid-State Circuits,2007,42(4):766-774.

[8] Mase Mitsuhito,Kawahito Shoji,Sasaki Masaaki,et al. A Wide dynamic range CMOS image sensor with multiple exposure-time signal outputs and 12-bit columnparallel cyclic A/D converters[J]. IEEE Journal of Solid-State Circuits,2005,40(12):2787-2795.

[9] Matsuo Shinichiro,Bales Timothy J,Shoda Masahiro,et al. 8.9-megapixel video image sensor with 14-b column-parallel SA-ADC[J]. IEEE Transactions on Electron Device,2009,56(11):2380-2389.

[10] Lin Jinfu,Chang Soonjyh,Chiu Chinfong,et al. Lowpower and wide-bandwidth cyclic ADC with capacitor and opamp reuse techniques for CMOS image sensor application[J]. IEEE Sensors Journal,2009,9(12):2044-2054.

(责任编辑:金顺爱)

A 10-Bit High Speed Column-Parallel ADC for CMOS Image Sensor

Yao Suying,Xu Wenjing,Gao Jing,Nie Kaiming,Xu Jiangtao

(School of Electronic Information Engineering,Tianjin University,Tianjin 300072,China)

A column-parallel ADC for high speed and small pixel size CMOS image sensor is proposed. The proposed ADC not only improves speed but also decreases chip area by combining single-slope ADC(SS ADC)with successiveapproximation ADC(SA ADC). SS ADC converts the upper five bits,and SA ADC converts the lower five bits. The coupling capacitor of 5-bit segmented capacitive DAC in SA ADC is a unit capacitor. In addition,error correction is realized by interval overlap. The proposed ADC,which is designed in 0.18,µm 1P4M standard CMOS process,shows an effective bit number of 9.81 at 167,kHz/s. It dissipates 0.132,mW with a 3.3,V power supply. The speed is 22,times faster than that of the conventional SS ADC.

CMOS image sensor;column-parallel ADC;single-slope ADC;successive-approximation ADC

TN402

A

0493-2137(2014)03-0243-06

10.11784/tdxbz201205014

2012-05-04;

2012-09-12.

国家自然科学基金资助项目(61076024,61036004).

姚素英(1947— ),女,教授,syyao@tju.edu.cn.

高 静,gaojing@tju.edu.cn.