基于NiosII改进的多周期同步频率测量系统设计

陈芳红,张志文

(西安工业大学电子信息工程学院信控技术研究所,陕西西安 710032)

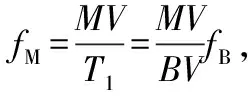

1 系统测频原理

改进的多周期同步法[1]是由多周期同步法基础发展而来,多周期同步法[2]的实际计数闸门是待测信号的整数倍,因此其相对误差与待测信号频率无关。改进的多周期同步法使得计数闸门是待测信号和时间基准信号的整数倍,对时间基准信号不存在误差。其原理如图1所示。在预置闸门T打开后,实际闸门T1并不立即打开,而是等到待测信号和时间基准信号的上升沿重合脉冲到来时,才打开实际闸门,开始分别对时间基准信号BS,待测信号MS开始计数,时间基准信号计数器记得值为BV,待测信号计数器记得值为MV,当预制闸门关闭时,实际计数闸门并不立即停止计数,而是等到待测信号和时间基准信号的重合脉冲到来时,才关闭实际计数闸门,停止计数。实际闸门是待测信号上升沿与时间基准信号脉冲上升沿相对重合。脉冲重合检测电路中存在脉冲上升沿重合的误差,因此控制待测信号上升沿与时间基准信号相对重合,使误差减小。实际闸门开启时待测信号与时间基准信号上升沿重合的时间差为Δt,脉冲上升沿重合脉冲控制最大误差为Δt,则|Δt1|≤Δt,|Δt2|≤Δt。T1=BV·fB,fB为时间基准信号的频率,不计时间基准信号的误差,实际闸门与时间基准信号同步,实际闸门为T1,待测信号的频率真实值为:

式中:δ为待测信号频率的相对误差为;fM为待测信号频率值。

待测信号的相对误差取决于脉冲重合检测电路的精度和预置闸门时间。

图1 全同步法原理图

2 电路原理图设计

如图2所示具体电路工作为:先粗测rm模块,为了保证测量的实时、高效率,要求采用测周法,就是在待测信号MS一个周期内对时间基准信号BS进行计数,Nios II根据粗测值MV0选择预置闸门时间STE;如果待测信号频率在0.1~1 Hz,预置闸门设置时间为10 s,Nios II向 OPG1写1,开启预置闸门1,如果频率在1 Hz~10 MHz,预置闸门时间设置为1 s,Nios II向OPG2写1,开启预置闸门2;PG模块作为产生预置闸门,用Verilog语言实现[3],分别在两个预置闸门时间内对时间基准信号进行计数;bmq模块为脉冲重合鉴别模块,获得脉冲重合的窄脉冲OP1;在预置闸门STE打开时,等到鉴别重合窄脉冲OP1到来时开启实际闸门,Q端输出实际闸门,对待测信号MS和时间基准信号BS同时计数,将计得数分别存入两个32位寄存器中,Nios II分别读取两计数器的值BV,MV。

图2 电路原理图设计

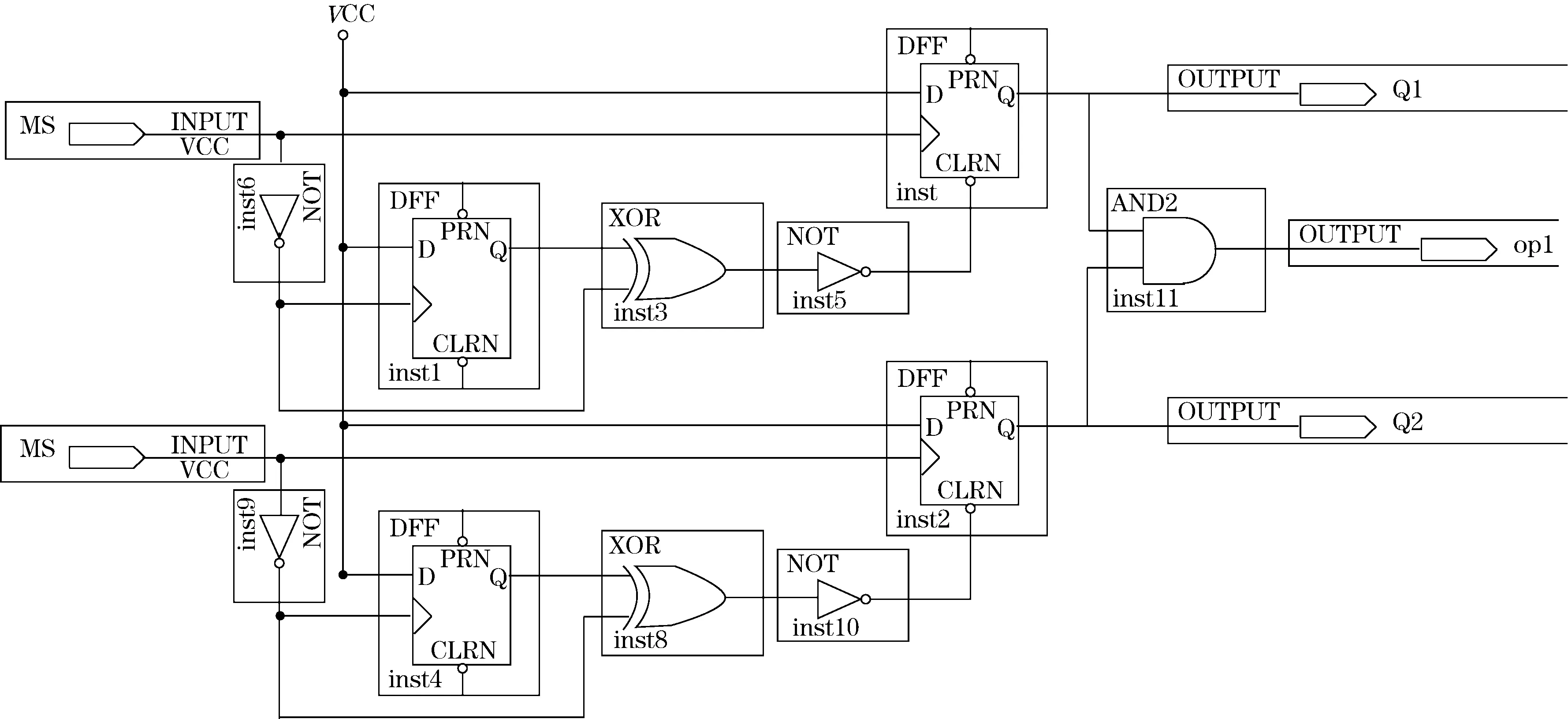

3 脉冲重合鉴别电路

脉冲重合鉴别电路如图3所示,由于时间基准信号的频率是50 MHz,周期为20 ns,将待测信号的窄脉冲与时间基准信号相与,得到脉冲重合的窄脉冲。最终产生窄脉冲op1;保证了待测信号,时间基准信号和实际闸门的整数倍。

图3 脉冲重合鉴别电路

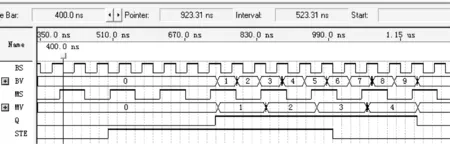

4 精测时序仿真图

精测计数仿真中,待测信号的周期为112 ns,在BS信号的周期为20 ns,预置闸门STE,计数器MSCT0,计数器BSCT0分别对待测信号MS和时间基准信号BS的计数,两计数器计数结果分别为MV,BV,预置闸门STE周期为1 μs,Q为实际闸门,系统精测时序仿真如图4所示。

图4 系统精测时序仿真结果

5 系统软件设计

5.1 NiosII软核定制

NiosII软核用户可以根据需要自定制,如图5所示显示了完整的系统配置和地址映射,在Quartus中启动SoPC Builder,添加CPU和外围设备,外部设备有定时器、2个32位的输入端口、1个1位的输出端口clr,片外存储器SDRAM,如图5所示。

图5 系统配置及其地址映射

5.2 NiosⅡ系统编程

NiosII集成开发环境(IDE)是NiosII系列嵌入式处理器的基本的软件开发工具,NiosII IDE 是 SOPC Builder 软件集成开发环境,具有编辑、编译、链接、调试、下载等功能[4]。该设计是在 NiosII IDE 开发平台上利用API函数编写完成。主要完成读数,向上位机发送数据,并对计数寄存器清零,系统软件主流程图如图6所示。

图6 系统软件主流程图

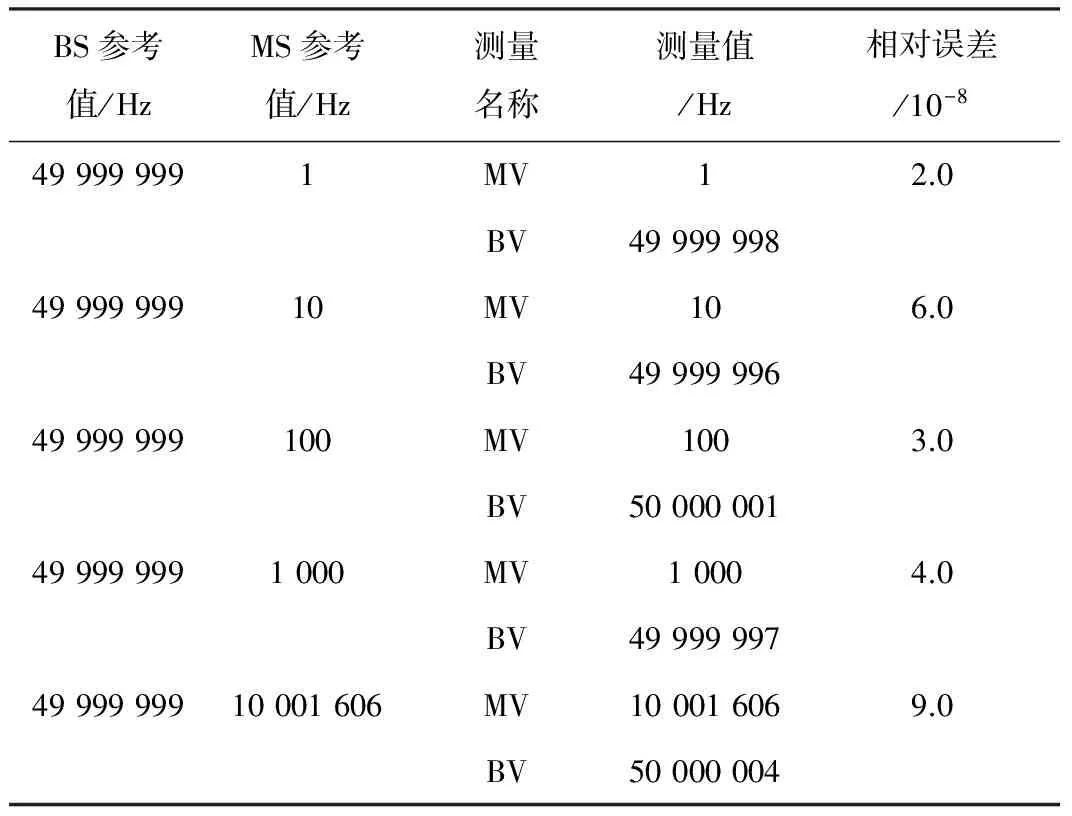

6 实验数据

表1 实验数据

7 结束语

通过设计基于NiosII全同步频率测量系统,将测频计数模块和控制模块集成在一块FPGA上,减少了硬件电路的复杂化,使得系统方便灵活;同时提高频率精度,解决了低频段频率测量精度低的问题。

参考文献:

[1] 徐秀妮.基于VHDL语言的全同步数字频率计的设计与研究:[学位论文].西安:长安大学,2011.

[2] 吴爱平,付青青.基于 NiosⅡ的等精度频率计设计.现代电子技术,2010(5) :84-85.

[3] 常晓明,李媛媛.Verilog-HDL工程实践入门.北京:北京航空航天大学出版社,2005.

[4] 李兰英.NiosⅡ嵌入式软核 SoPC 设计原理及应用.北京:北京航空航天大学出版社,2006:280-327.