基于SDIO与SPI接口的信号发生器

于小强,杨 晖,2,,杨海马,宋磊磊,李 军,V.Zivkovic,胡恒庆

(1.上海理工大学光学与电子信息工程学院,上海 200093;2.上海理工大学,上海市现代光学重点实验室,上海 200093;3.阿德雷德大学电气与电子工程学院,阿德雷德 5005 )

0 引言

目前,信号发生器广泛应用于通信、测控、医疗等领域,但是所采用的精密仪器大多成本过高,造成资源的浪费。所以,如何采用低成本实现高精度的信号发生器是亟需要解决的问题。通常,采用可编程DDS芯片[1-2]为核心,通过内置函数查找表的方式进行设计,如文献[1],不仅成本高且波形种类少;文献[2]中提出改进,在波形类型上加以扩充,但是在控制上及数据存储方面没有详细方案,幅频的精度调节可行性不高。结合上述方案提出文中的设计方法。

1 系统参数与设计

为了克服传统信号发生器[3]的可调节性差的缺点,该设计主要先进行以下改进:(1)具备波形数据存储空间;(2)波形输出频率10 Hz~20 kHz,输出幅值0~10 V,最大输出功率18 W;(3)幅频手动可控,幅值增益最小调节0.5 dB,自定义频率调节单位;(4)无波形数据输出时,噪声输出电压小于0.4 mV.

系统如图1所示,主要由数据存储单元、幅频调节单元及波形数据处理单元构成。主控器通过SDIO接口从FAT文件系统中获取波形数据文件,通过SPI总线将WAV数据流送至解码器,解码后高精度D/A输出,经过程控增益放大器调节幅值后送至功率放大器放大输出。程控放大器增益由主控器控制。

图1 系统结构

2 信号发生器硬件设计

2.1 硬件介绍

系统的主控制芯片采用的是32位处理器STM32F103ZET6,该芯片使用高性能的ARM Cortex-M3

32位的RISC内核,工作频率为72 MHz,内置高达512 K字节的闪存和64 K字节的SRAM.具有SDIO接口,最大数据传输速度48 Mbit/s.并且提供两个SPI串行接口,最大通信速率18 Mbit/s.

2.2 SDIO接口电路设计

主控器支持MMC卡系统规范4.2版中的3种数据总线模式:1 bit、4 bits和8 bits.文中采用2.0版本Micro SD卡,通过4 bits数据总线模式完成数据通信。SD存储卡与控制器的接口定义如下:

表1 SDIO接口定义

表1中,SDIO_CK时钟是通过PC12引脚连接到SD卡的,是SDIO接口与SD卡用于同步的时钟。所有命令及命令响应,都是通过SDIO_CMD引脚来传输的,4 bits数据总线是PC[8:11] 。主控器与Micro SD的硬件连接如图2所示,

图2 主控器与SDIO、SPI接口电路

2.3 SPI接口解码器电路设计

波形数据采用的是WAV数据流存储与解码,解码芯片采用高性能解码芯片VS1053,支持MP3及WAV数据流解码。且内部具有低功耗DSP 处理器内核VS_DSP4,为用户提供5 KB的指令RAM和0.5 KB的数据 RAM。通过SPI总线接收数据流,解码后18位高精度模拟量输出,且内置部分函数测试查找表。VS10534是通过7根线同主控器连接的,VS-XRST是复位信号线,低电平有效,VS-DREO是数据请求信号,通知主机是否可以接收数据,剩余的为SPI2四线接口,硬件电路见图1。

2.4 输出波形调节硬件电路设计

2.4.1 幅值调节电路

解码器模拟量输出后,为了达到高精度的幅值控制,采用程控增益放大器PGA2310。由于其增益调节范围为+31.5~-95.5 dB,最小调歩距为0.5 dB,且噪声低、失真小。硬件连接电路如图3所示,主控器通过PGA_CS、PGA_DATA、PGA_CLK引脚控制输出信号与输入信号之间的幅值比。由于解码器输出左右通道2路信号,程控增益放大器同样也具备;2路放大与输出,该设计只采用了图中的一路信号VSOUT1及一路增益输出信号POUT1。

图3 幅值控制电路

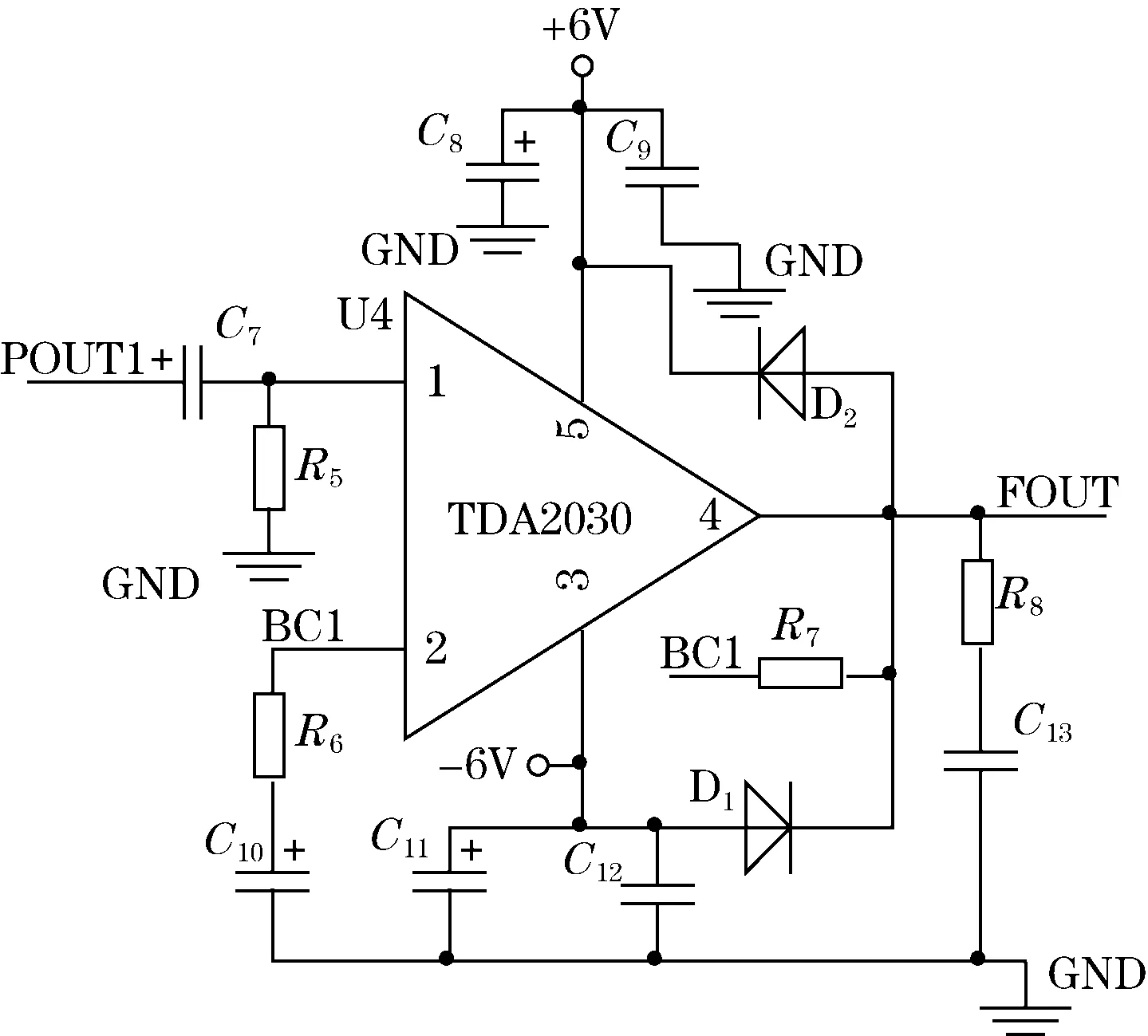

2.4.2 功率放大电路

解码器的信号输出端已足够驱动20 Ω的负载,但是考虑到信号发生器的输出信号所用的场合不同,输出级的负载也不同,所以设计功率放大电路以满足不同场合的需要。该设计采用TDA2030功率放大芯片,采用正负供电电源。该芯片具有上升速率高、失真小、输出功率大等优点,最大输出功率可达18 W,完全满足常用场合要求。程控增益输出信号通过1 μF的极性电容后与TDA2310的1号脚相连。如图4所示:

图4 功率放大电路

3 软件设计

3.1 波形数据提取及幅频调节

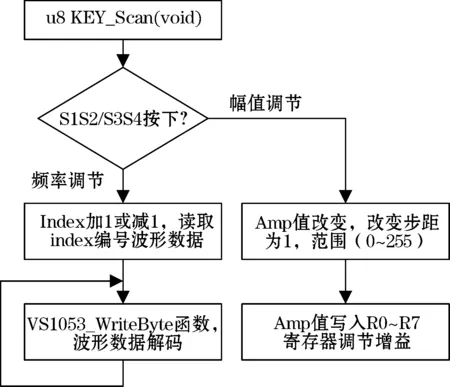

为了实现不同种类的信号输出,利用SDIO接口将波形数据存储在Micro SD卡中,并且在SDIO底层硬件驱动的基础上移植FAT文件系统。以正弦波数据存储为例,波形数据是以数字序号为文件名的WAV音频文件。不同频率的波形以不同数字作为文件名。FAT文件系统通过函数将存储区的WAV波形文件名信息读取出,可通过结构体finfo访问:f_mount(0,&fs);//注册工作区,初始化盘符为0f_opendir(&dirs,path);//打开卡的根目录,并将这个根目录关联到dirs这个结构指f_readdir(&dirs,&finfo);//读取目录信息result=strstr(finfo.lfname,".wav");//判断文件名图1中,4个按键控制幅值与频率,通过调用函数KEY_Scan()进行按键扫描,按键S1、S2调节输出波形幅值,按键S3、S4调节波形频率。如图5。

图5 波形幅频控制流程

3.2 WAV数据流解码输出

通过SPI2接口对VS1053解码器进行配置及数据流的传输。解码器的写时序如图6所示,读写过程相似,都是先发指令后发地址,最后传输数据,数据通过SI端写入,SO维持低电平,通过判断DREQ电平决定是否进行下一步操作。

图6 解码器写时序

下面以一次数据传输为例:复位VS1053,调用VS_Soft_Reset();配置工作寄存器,调用WriteRegister(3,0x98,0x00),设置VS1053的时钟3倍频,调用WriteRegister(5,0xBB,0x81),采样率设置为48 K;传输波形数据,调用VS1053_WriteByte( buffer[count] ),一次最大32个字节,解码数据流并模拟量输出。

4 实验结果及分析

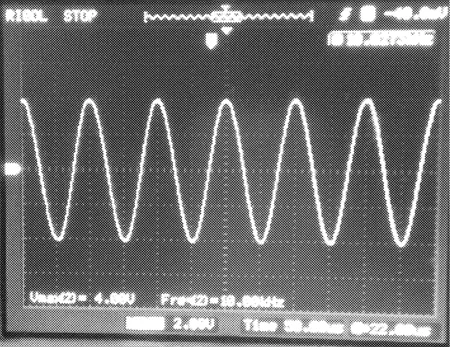

采用上述配置,在Micro SD卡中存储频率10 kHz,幅值为0.4 V的正弦波形,解码后,经过程控增益放大器10倍增益放大,FOUT端信号输出,示波器测得波形图如图7所示。

图7 10 kHz正弦波形

由示波器测得结果可见,幅频可控且波形频率精确,最大误差小于0.5%。无输入时,基本无电压。

5 结语

设计了基于SDIO及SPI接口的信号发生器,移植了FAT文件系统作为系统存储,采用按键及串口进行幅频调节,实验证明可实现不同种类的波形输出,且幅频调节精度高。

参考文献:

[1] 王丹.采用DDS频率合成的虚拟信号发生器研究.传感技术学报,2007,20(3) :586-591.

[2] 郝迎吉.基于VS1003 解码器的信号发生器.仪表技术与传感器,2013(2):19-20.

[3] 卢华英.基于LabVIEW和FPGA的模拟信号源设计.测控技术,2013(5):9-11.