石墨烯晶体管的加工及测试研究

王永存,薛晨阳,刘耀英,田学东,张文栋,李 铁

(1.中北大学,仪器科学与动态测试教育部重点实验室,电子测试技术重点实验室 山西太原 030051;2.中国科学院上海微系统与信息技术研究所,上海 200050)

0 引言

石墨烯(Graphene)是一种由碳原子构成的零带隙二维纳米结构的新材料,2004年由英国曼彻斯特大学物理学家安德烈-海姆和康斯坦丁-诺沃肖洛夫从石墨中分离出来,证明了二维材料石墨烯可以稳定存在。石墨烯是现有材料中最薄的,它的厚度只有0.335 nm,但它却是现有材料中最坚硬的。同时石墨烯的导热系数高达5 300 W/(m·K),这一数值高于金刚石,常温下石墨烯中电子的迁移率约为15 000 cm/(V·s),远高于硅中电子的迁移率。由于石墨烯具有优异的电学特性,所以它非常适合用来制造电子元件,科学家认为石墨烯有望替代硅成为下一代半导体材料[1-4]。石墨烯的制备方法主要有机械剥离法、化学气相沉积法和热分解法等。机械剥离法可以制备晶格完好的高质量石墨烯,但是不适合大量生产;热分解法可以制备大面积石墨烯,但是条件苛刻,需在高温高真空下进行;化学气相沉积方法是最适合大面积制备石墨烯薄膜的方法。化学气相沉积法具有工艺限制条件少和可控性高等优点,现在大面积制备石墨烯薄膜多采用这种方法[5-6]。

石墨烯晶体管以石墨烯薄膜作为导电沟道,一方面石墨烯薄膜厚度很薄,可以加工成几纳米宽的条状,大大缩小晶体管器件尺寸,延续摩尔定律;另一方面,石墨烯电子迁移率高,可以提高晶体管的响应速度,使晶体管具有更高的截止频率[7-8]。该试验通过转移化学气相沉积法制备的石墨烯薄膜到Si/SiO2基底,制作了顶栅石墨烯晶体管和背栅石墨烯晶体管,比较两种结构晶体管的电学性能。

1 试验

通过化学气相沉积法在铜箔衬底上制备出石墨烯薄膜,图1为石墨烯薄膜的拉曼测试图。然后,在石墨烯薄膜表面旋涂一层聚甲基丙烯酸甲酯PMMA薄层,溶解掉铜箔,再将附在PMMA上的石墨烯转移到Si/SiO2基底上,去除PMMA使石墨烯吸附在Si/SiO2基底上,通过退火提高石墨烯与Si/SiO2基底的结合,图2为Si/SiO2基底上的石墨烯边缘形貌图。

图1 石墨烯的拉曼测试图

图2 石墨烯表面图

通过电子束光刻和氧等离子体刻蚀工艺实现石墨烯薄膜图形化。电子束光刻将图形转移到石墨烯薄膜上,利用光刻胶作为氧等离子体刻蚀的掩膜层,保护作为晶体管导电沟道部分的石墨烯薄膜,从而将其他部分的石墨烯薄膜刻蚀掉。这步工艺要注意氧等离子体刻蚀的功率和时间,功率过大或者时间过长会刻蚀掉部分的光刻胶导致石墨烯导电沟道存在缺陷,时间过短会导致石墨烯薄膜无法刻蚀干净,通过几次验证,试验中选择功率为200 W、刻蚀时间为5 min的刻蚀条件,这样既可以刻蚀干净石墨烯薄膜又保障光刻胶不会被刻蚀掉,图3为刻蚀后的石墨烯薄膜图。

图3 刻蚀后的石墨烯图形

然后电子束光刻和电子束蒸镀制作石墨烯晶体管的源极、漏极和栅极,源极、漏极和栅极金属选择Cr/Au(Cr 10 nm,Au 80 nm)。图4为石墨烯薄膜制备了源极和漏极之后的结构图。对于顶栅结构的石墨烯晶体管,需要在石墨烯薄膜上利用ALD沉积一层5 nm厚的Al2O3作为栅介质层,这层介质层的质量直接决定了顶栅结构的晶体管的性能,所以在ALD沉积Al2O3之前要充分做好前处理工艺。

图4 石墨烯晶体管源和漏极

加工过程中,光刻胶和清洗液等都会对石墨烯薄膜造成污染,所以整体工艺完成后还要进行一步退火工艺,进一步提高器件性能。

2 结果与讨论

石墨烯晶体管尺寸参数:沟道长度1 μm,宽度100 μm.图5为石墨烯晶体管的总体结构图。利用安捷伦半导体分析仪对加工的顶栅结构的石墨烯晶体管和背栅结构的石墨烯晶体管进行测试。首先是栅调制测试,在几个变化的栅压VG下测量石墨烯沟道电流ID随源漏之间电压VD的变化,其中VD为源极和漏极之间的电压,VG为栅极电压,ID为石墨烯沟道电流。

图5 石墨烯晶体管总体结构图

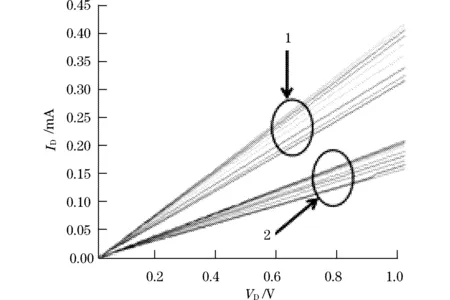

图6是两种结构的石墨烯晶体管的I-V曲线,其中电流较大一簇(曲线1)是顶栅结构石墨烯晶体管的I-V曲线,电流较小的一簇(曲线2)是背栅结构石墨烯晶体管的I-V曲线。图中,曲线1、2的VG由上至下依次为4 V,3 V,2 V,1 V,0 V,-1 V,-2 V,-3 V,-4 V.图6中,随着VD增大ID增大,ID-VD呈线性关系,VD/ID即为石墨烯沟道电阻。随着栅压变化石墨烯沟道电阻值也在变化,即栅压对石墨烯的调制作用。从图6的曲线得出相同VD下,顶栅结构的石墨烯导电沟道电流ID随栅压变化而产生的变化更大,说明顶栅结构的石墨烯晶体管的栅调制效果好于背栅结构的石墨烯晶体管。

图6 石墨烯晶体管I-V特性曲线

石墨烯导电沟道的狄拉克点测试是在VD恒定的情况下,扫描一定范围内的VG,测量石墨烯导电沟道的电流ID.石墨烯的狄拉克点对应石墨烯中载流子最少,导电性最差,即电阻最大的点。纯净的石墨烯其狄拉克点对应栅压为零的位置,图7中石墨烯的狄拉克点偏移了,这是由于石墨烯吸附水分子和加工工艺中引入了杂质导致的,其中曲线1对应顶栅结构的石墨烯晶体管,曲线2对应背栅结构的石墨烯晶体管。图7显示出石墨烯导电沟道的最大电流和最小电流,通过计算可以分别得出两种结构石墨烯晶体管的开关比。顶栅结构的石墨烯晶体管的开关比约为20,背栅结构的石墨烯晶体管的开关比约为5,可以知道顶栅结构晶体管的开关比略大于背栅结构晶体管的。但是两种结构石墨烯晶体管的开关比都较小,这是由于石墨烯的禁带宽度为零,电流无法无法完全截止,通过对石墨烯进行禁带宽度调控可以有效提高开关比。

图7 石墨烯晶体管Dirac点测试图

3 结论

通过对化学气相沉积法制备的石墨烯薄膜进行转移和加工,制备出顶栅结构的石墨烯晶体管和背栅结构的石墨烯晶体管,通过对两种结构的石墨烯晶体管进行测试,得到顶栅结构的石墨烯晶体管和背栅结构的石墨烯晶体管的I-V和狄拉克点的测试曲线,结果表明顶栅结构的晶体管在栅调制和开关比上优于背栅结构的石墨烯晶体管,为石墨烯材料的研究奠定了基础。

参考文献:

[1]KANG H C,KARASAWA H,MIYAMOTO Y,et al.Epitaxial graphene top-gate FETs on silicon substrates.Solid-State Electronics,2010,54(10):1071-1075.

[2]WANG W R,CHEN L,WANG Z,et al.Weak localization in few-layer graphene grown on copper foils by chemical vapor deposition.Carbon,2012,50(14):5242-5246.

[3]CHAMPLAIN J G.Champlain.A physics-based,small-signal model for graphene field effect transistors.Solid-State Electronics,2012,67(1):53-62.

[4]KANG H C,KARASAWA H,MIYAMOTO Y,et al.Epitaxial graphene field-effect transistors on silicon substrates.Solid-State Electronics,2010,54(9):1010-1014.

[5]BRITNELL L,GORBACHEV R V,JALIL R,et al.Field-effect tunneling transistor based on vertical graphene heterostructures.science,2012,335(6071):947-950.

[6]CHEN B D,LIU H Z,LI X,et al.Fabrication of a graphene field effect transistor array on microchannels for ethanol sensing.Applied Surface Science,2012,258(6):1971-1975.

[7]WANG Y J,HUANG B C,ZHANG M,et al.Optimizing the fabrication process for high performance graphene field effect transistors.Microelectronics Reliability,2011,52(8):1602-1605.

[8]SHAHI K M F,BALANDIN A A.Thermal properties of graphene and multilayer graphene:Applications in thermal interface materials.Solid State Communications,2012,152(15):1331-1340.