基于FPGA的SATAII协议物理层实现

叶勃宏

(西安电子科技大学CAD研究所,陕西西安710071)

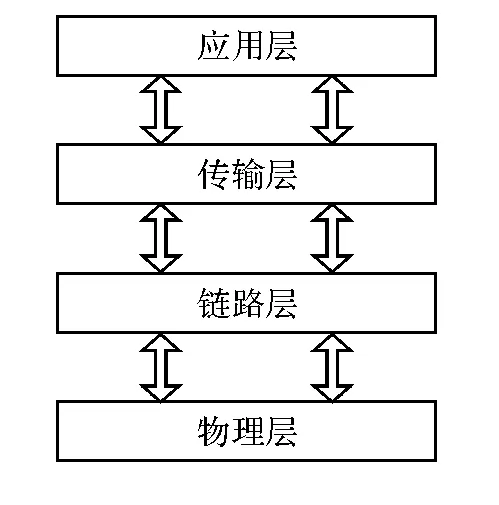

SATA作为一种高速串行链路已取代了IDE作为硬盘的标准接口。该高速差分链路使用吉比特传输和8B/10B编码技术,其相比于IDE、PATA接口具有传输速度更高、设备升级更简单和配置使用更便捷等优势[1]。首先,作为一种高速点对点的传输方式,SATA解决了直流偏置、信号偏移、码间干扰等问题,并提高了传输的带宽。同时具备了更完善的查错和纠错能力,传输质量和传输可靠性得到了大幅提升。其次,SATA接口相比于传统的并行接口具有更少的引脚数目,更利于PCB板级的设计、装配和散热。最终,SATA总线还支持热插拔并具有更低的功耗。SATA接口协议具有层次化的结构[2-3],如图1所示,从下到上分别是物理层、数据链路层、传输层和应用层。其中物理层负责低压差分信号的发送和接收,并实现接口的初始化过程和速率的自动协商。

1 物理层功能

图1 SATA协议层次结构

在发送过程中,物理层从链路层接收并行的数据将其转为串行数据,然后以3 Gbit·s-1的线速度向硬盘侧发送LVDS NRZ高速比特流。在接收过程中,将串行数据转化成并行数据,在串行数据流中检测其中的K28.5字符,使得输出的并行数据对齐[4]。物理层提供的具体功能如下:(1)发送侧和接收侧提供100 Ω电阻进行内部端接,以此来消除反射,保证信号的完整性。(2)向链路层提供不同位宽的接口。(3)用CDR技术从高速的串行比特流内恢复出时钟和数据。(4)K28.5字符检测,以此来对齐接收到的数据。(5)发送和检测OOB(Out-Of-Band)信号,进行硬盘和FPGA的同步和协商。(6)向上层报告物理层的工作状态。(7)提供电源管理功能,以此降低功耗。(8)支持接收和发送阻抗匹配。(9)解决扩散频谱时钟引起的输入数据频率波动。(10)响应远端发出的测试请求。

2 OOB信号

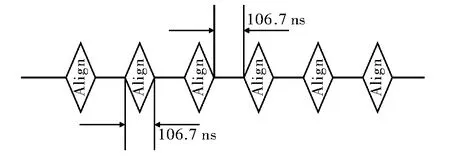

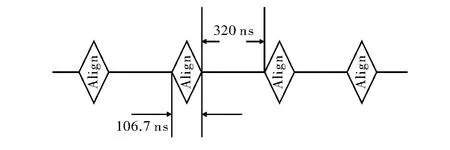

SATA协议使用OOB信号来完成初始化过程和速率协商过程。OOB信号不属于数据信号,所以称之为带外信号。OOB是一种低频信号,具体含有3种模式:COMRESET、COMINIT和COMWAKE。COMRESET,如图2所示,由主机端发送,用来设备复位和链路的初始化,其由突发长度为106.7 ns的Align原语和320 ns的空闲共模电平分隔。COMINT,如图2所示,格式与COMRESET相同,与后者的区别在于,其是由设备侧向主侧发送的。COMWAKE,如图3所示,与前两者的区别在于其的空闲间隔为106.7 ns,且设备侧和主侧均可以发送。

图2 COMRESET/COMINIT信号

图3 COMWAKE信号

3 物理链路建立过程

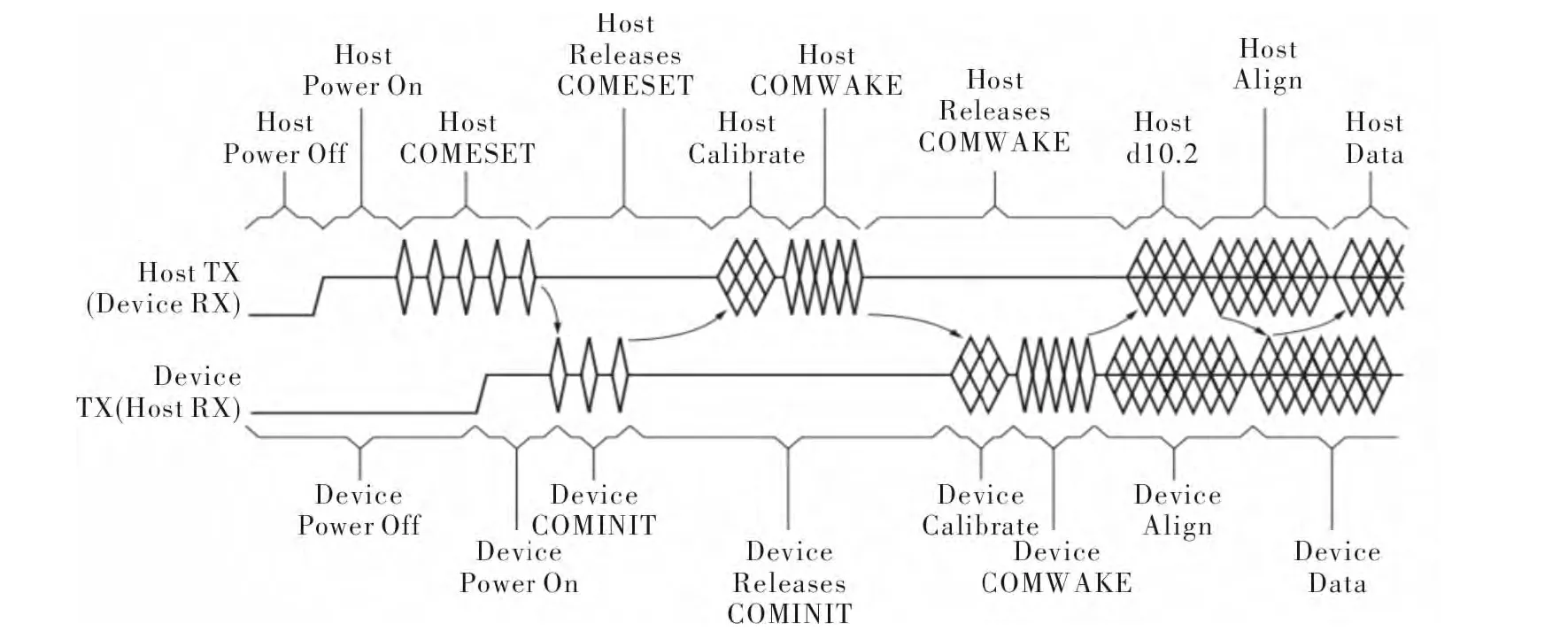

在上电和硬件复位期间,主机通过OOB信号来建立通行链路,其中包括速度协商、时钟恢复、阻抗校准和自我诊断等。具体上电过程如图4所示,由以下10个步骤组成:(1)主侧FPGA和设备侧硬盘处于断电状态。(2)系统上电,主设备侧将发送和接收差分对拉到共模电压。(3)主设备侧发送COMRESET信号。(4)当上电复位结束后,主设备侧停止发送COMRESET信号并将串行总线置于空闲状态。(5)当硬盘检测到COMRESET信号,其开始发送COMINIT信号作为响应。硬盘可在任何时间点通过发送COMINIT信号来建立新的通信连接。(6)主设备侧进行校准且发送COMWAKE信号。(7)当硬盘在其的接收线上检测到COMWAKE信号后,其开始校准发送器。完成校准后,硬盘发送突发长度为6的COMWAKE信号然后连续发送Align原语。当连续发送54.6 μs的Align原语后还未收到来自主设备侧的回应,而硬盘侧则进入错误状态。(8)当主设备侧检测到COMWAKE信号后便以所支持的最低速率开始发送D10.2字符。于此同时,主设备侧开始锁定Align原语,当准备好便以与接收到相同的速度向硬盘侧发送Align原语。若在880 μs内主设备未接收到Align原语,主设备便重新开始复位。(9)硬盘锁存到Align原语序列,并在准备就绪后,发送SYNC原语表明可正常运行。(10)当主机侧接收到非Align原语,链路建立完成,则可进行正常的数据传输。

图4 链路建立过程图

4 实现过程

SATA协议物理层的实现由3部分组成,分别是整体流程图的设计、时钟部分和速率协商状态转移设计。

4.1 整体设计流程图

初始化的过程严格按照SATA协议的规定。整个过程流程如图5所示。主机端上电后首先发送持续时间为1 μs的COMRESET信号,然后等待COMINIT信号,当Rxstatus等于100时,再发送持续时间为1 μs的COMMWAKE信号。在接收到COMMWAKE信号后且线路处于空闲的状态,接着发送D10.2字符。若在880 μs内接收到了Align原语,则发送Align原语且开始等待SYNC原语,否则将重新开始发送COMRESET信号[4-7]。

图5 设计整体流程图

4.2 时钟控制设计

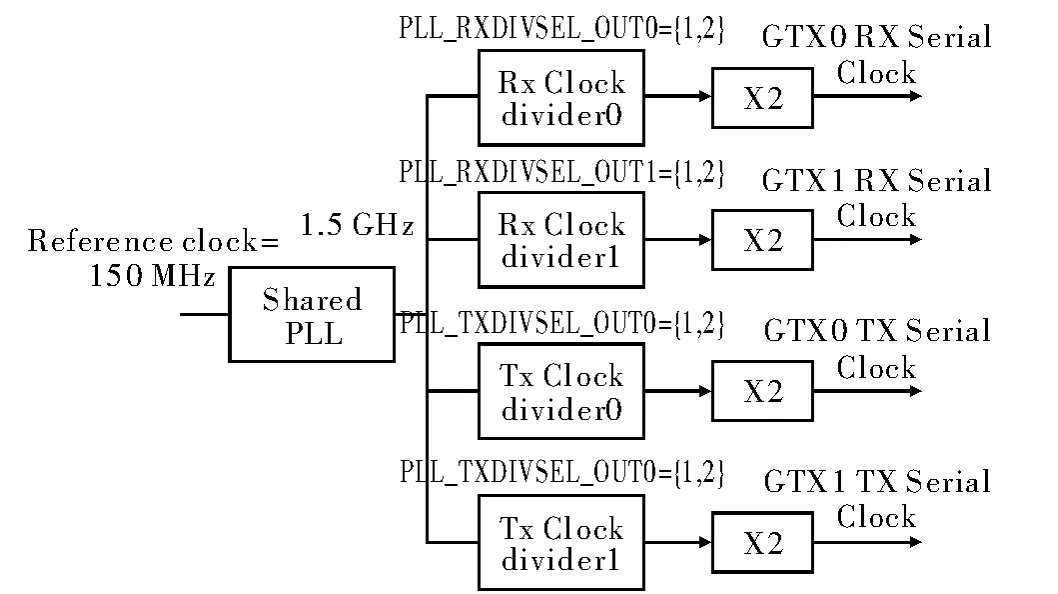

SATA协议物理层的实现是基于Xilinx公司的FPGA,利用FPGA内部提供的高速Serdes接口实现高速比特流的发送、接收和串并转换。其中一个高速串行收发器GTX由两个TILE组成,为节省功耗,两个TILE由一个锁相环,如图6所示提供时钟。由外部提供给GTX中锁相环的参考时钟频率为150 MHz,其中锁相环的PLL_DIVSEL_FB参数设置为2,PLL_DIVSEL_REF参数设置为1,INTDATAWIDTH参数设置为1,在这种设置条件下锁相环输出的倍频时钟PLLCLK为1.5 GHz,如图7所示。该倍频时钟分别提供给发送器和接收器。提供给发送器的参考时钟由参数PLL_TXDIVSEL_OUT设定,接收器则由参数PLL_RXDIVSEL_OUT决定。参数PLL_TXDIVSEL_OUT、PLL_RXDIVSEL_OUT的可能取值为1和2。参数取值由协商的速率决定,可在协商的过程中通过DRP接口动态地改变。提供给FPGA逻辑部分的时钟由GTX提供给链路层的数据位宽决定[8-11]。锁相环模块对外提供的接口信号如下:(1)CLKIN信号用来向模块提供参考信号。(2)INTDATAWIDTH信号用来决定GTX串行收发器内部的数据宽度。(3)PLLDET信号用来表示锁相环内部的VCO压控振荡器的输出范围是否在可接受的有效范围内。(4)PLLDETEN信号用来使能内部的锁定功能。(5)REFCLKOUT频率等于CLKIN,其可为上层的逻辑电路提供参考时钟。

图6 锁相环结构图

图7 锁相环输出时钟图

整个SATA物理的时钟网络结构,如图8所示,由4部分组成[8],分别是高速串行收发器部分、OOB信号控制部分、DCM数字时钟控制部分和SNC同步控制部分,其中高速串行收发器向逻辑控制部分提供DRP动态控制接口。GTPRESET信号用来对整个收发器进行全局的复位。TXDATA接口用来接收将要发送的并行数据。RXDATA接口用来将串并转化后的并行数据提供给上层。TXCOMSTART用来指示收发器何时开始发送OOB信号,并将其置1时开始发送OOB信号,置0不发送OOB信号。TXCOMTYPE用来指示发送OOB信号的种类。TXCHARISK信号用来指示所发送的数据是否是K字符。RXSTATUS用来表示串行收发器的状态。

图8 FPGA内部时钟结构图

REFCLKOUT时钟信号由串行收发器模块输出,经全局时钟缓冲器BUFG进入FPGA的全局时钟专用网络,最后进入DCM和SNC模块。从DCM输出CLK0时钟和CLK2X时钟,分别通过BUFG后向收发器提供并行的收发时钟。SNC模块可通过动态地改变收发器的状态达到速率自动协商的功能。OOB模块用来控制带外信号的发送和接收。

4.3 速率协商设计

速率协商的状态转移过程如图9所示。该设计方案可根据设备硬盘侧挂载的硬盘型号,自动的改变主FPGA这一侧的线速率。若硬盘支持I代接口,则FPGA自动调整GTX线速率到1.5 Gbit·s-1,若硬盘支持II代接口,则FPGA自动调整线速率到3 Gbit·s-1。

具体的调节过程如下:

(1)设备复位后,改变接收器的线速率为3 Gbit·s-1,通过DRP动态接口读取并修改地址为0X46寄存器的值为1。(2)等待16个时钟周期。(3)改变发送器的线速率为3 Gbit·s-1,通过DRP动态接口读取并修改地址为0X45寄存器的值为1。(4)复位OOB信号控制模块,此时FPGA和硬盘进行速率协商。(5)等待链接建立,若在3.5 ms时间内链接建立完成,则物理层准备好,此时给上层一个PHYRDY的信号。(6)若未建立好,则改变接收器的线速率为1.5 Gbit·s-1。通过DRP动态接口读取并修改地址为0X46寄存器的值为0。(7)等待16个时钟周期。(8)改变发送器的线速率为1.5 Gbit·s-1。通过DRP动态接口读取并修改地址为0X45寄存器的值为0。(9)等待链接建立,若3.5 ms内链接建立,则硬盘和主FPGA协商的速率为1.5 Gbit·s-1,向上层报告链路建立可进行正常的数据传输,若未建立,则从过程(1)开始重新循环,直至速率协商好为止。

图9 速率协商过程图

5 结束语

代码调试完成后下载到Xilinx提供的ML507评估板中,利用Chipscope工具抓取的波形如图10和图11所示。图10中speed信号为低,表示速率协商到1.5 Gbit·s-1。在图11中,SOF信号带来一个高脉冲后,RXDATA信号线上的数据是硬盘与FPGA建立连接后由硬盘发送的一帧报告硬盘状态信息的寄存器类型帧。帧的有效长度介于SOF的高脉冲和EOF的高脉冲之间。帧的长度是6个双字,最后4 Byte为CRC校验值,其中所有的数据均经扰码加扰。从图中可看出,物理层完成了速率协商和链接建立的过程。

图10 协商速率结果图

图11 帧信息

[1] 罗彬.硬盘的接口方式及技术指标解析[J].计算机与网络,2007(z1):37-39.

[2] IntelliProp Inc.IntelliProp serial ata device interface core[M].USA:IntelliProp Inc,2009.

[3] 欧阳干.PCI Express物理层的设计与实现[D].长沙:国防科学技术大学,2006.

[4] Xilinx.Virtex-5 FPGA rocketIO GTX transceiver user guide[M].MA USA:Xilinx Conpration,2008.

[5] 赵峥嵘,兰巨龙.RocketIO几个关键问题的解决方案[J].电子技术应用,2005(12):51-53.

[6] 欧阳科文,黎福海,唐纯杰.基于RocketIO的SATA物理层高速串行传输实现[J].计算机测量与控制,2009(5):937-939.

[7] 高世杰,吴志勇.基于RocketIO的多路相机数据传输系统的设计[J].光通行技术,2008(5):46-48.

[8] 唐纯杰.SATA协议分析及其FPGA实现[D].长沙:湖南大学,2009.

[9] 李江涛.RocketIO高速串行传输原理与实现[J].雷达与对抗,2004(4):48-50.

[10] SATA-IO.Serial ATA Revision 2.5:serial ATA international organization[S].USA:SATA-IO,2009.

[11] Xilinx.Xilinx xapp870(v1.0)[M].MA USA:Xilinx Conpration,2008.