基于FPGA的梯形波冲击试验测控系统

王 琳,董振华

(1.西安铁路职业技术学院,陕西西安,710016;2.西安捷盛电子技术有限责任公司,陕西西安,710119)

基于FPGA的梯形波冲击试验测控系统

王 琳1,董振华2

(1.西安铁路职业技术学院,陕西西安,710016;2.西安捷盛电子技术有限责任公司,陕西西安,710119)

为了评定试件在受到梯形波冲击时的耐冲击强度,提出了一种基于FPGA的梯形波冲击试验测控方案。实际测试表明此设计方案具有较高的灵活性,可靠性及稳定性。

FPGA;梯形波冲击;波形测量

0 引言

冲击试验用于验证装备上的元件、部件承受预计力作用的能力,评价装备上的元件、部件在此环境下的结构完好性、性能可靠性,是军用装备必不可少的试验装备。GJB150A、GJB548A、GJB360A、美军标MIL-STD-810F、MIL-STD-883E、MIL-STD-202E均把冲击试验作为军用装备重点试验之一。目前,国内冲击试验虽已普遍展开,但受试验设备限制,试验波形仅限于半正弦波形,就试验目的而言,半正弦波适用于模拟线性系统的撞击或线性系统的减速所引起的冲击效应;梯形波通常用于空间运行装置和飞行器发射等爆炸性环境的冲击效应,随着航天技术不断发展,很多单位都急切需要利用梯形波冲击试验完成产品测试,提高产品可靠性。

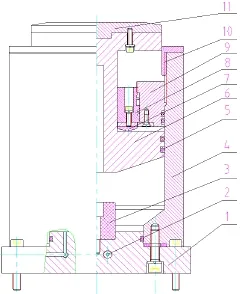

梯形波发生器的结构如图一所示。

它主要由底座1、气缸4、缓冲安全垫3、活塞6、调节块8、调节块9、定位圈10以及冲头11等组成。工作台和试验件一起跌落撞击活塞,活塞向下运动压缩主气室气体气室压力随气室容积缩小急剧变大过程,产生梯形波的上沿;气室压力随气室容积变化趋于平稳阶段,产生梯形波中段;气室压力随气室容积增大急剧变小,产生梯形波的下沿。通过调节气室容积、气室初始压力可以改变气态方程常数。从而改变梯形波上升与下降斜率及峰值加速度和脉冲持续时间。在气缸容腔内充入不同大小压力的气体,可改变活塞6受到力的大小,从而获得不同加速度峰值A,不同冲击脉冲持续时间D的脉冲波形,及相同A、D,不同质量m时的F (t)~Z(t)曲线,冲击持续时间靠活塞相对于气缸位移程度即台面的跌落能量(高度)调整,冲击加速度的峰值靠气缸气体压强调整。

1 总体方案

图一梯形波发生器结构图

由于可编程逻辑器(FPGA)具有丰富的可编程性与丰富的I/O引脚,使得它在数字系统中的应用越来越广泛,如同自行设计集成电路一样,可节省电路开发的费用与时间。因此本文就提出了一种基于FPGA的梯形波冲击试验测控方案。

系统组成如图二所示,上位机将动作电平输入FPGA,FPGA根据相应的电平变化发出继电器控制信号,控制系统进行提升、活塞杆下降、跌落等动作,并通过气动伺服阀控制气缸气体压强,通过不断修正气缸气体压强、缓冲高度等参数完成相应的梯形波发生,同时高速AD进行台面冲击波形采集并送至上位机进行分析,最终得到满足试验要求的梯形波冲击波形。

图二 系统组成

2 系统硬件实现

模块由FPGA触发存储控制、USB2.0传输和AD7865数据采集部分构成。采用Cyclone系列EP1C12Q240C8型号的FPGA控制芯片,其Bank3 I/O口与AD7865相连,有源晶振提供了48 MHz的时钟频率。

2.1 采集模块

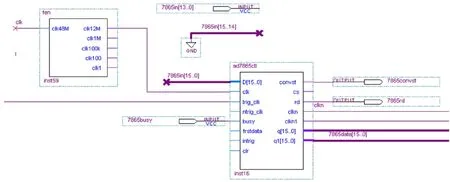

AD7865是美国Analog Device公司生产的一种高速,低功耗,四通道同步采样的14位AD转换器,采用+5V供电。芯片内部有一个2.4 μs的逐次逼近的ADC,4个跟踪/保持放大器,内部2.5V参考电压,片上时钟振荡器和一个高速并行接口。采样模块如图三所示。

由于冲击波形的脉冲宽度变化从1ms到45ms,因此采集模块需要控制采集的采样速率在从100K至2K间变化。解决方法是在准备采集前通过ad7865ctl模块的trig_clk端输入随采样脉宽变化的采样频率时 钟,继而通过编制采样状态机来控制ad7865时序,当trig_clk接到触发时钟上升沿后,busy变高电平,当一次采样结束后busy端变低电平,连读两次将双通道数据锁存,并给数据的第15位添加通道标志,使得后续处理数据更加方便,其中。当采样长度达到设定值后,采样频率被中断ad7865进入低功耗运行状态并等待下次采样启动。

图三 采样模块

2.2 触发及存储

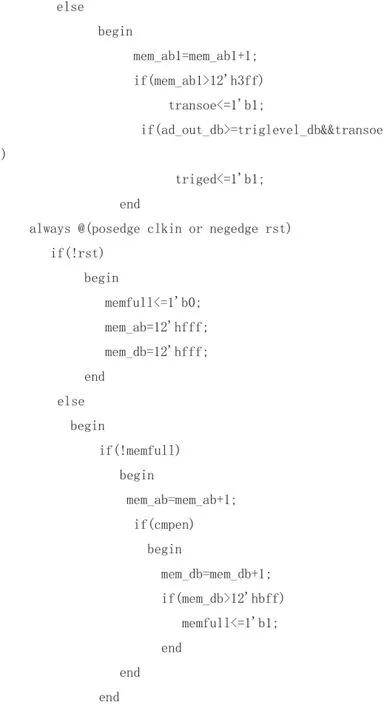

当上位机通过usb2.0通信接口设置好触发窗长度、触发点电平时,启动采集命令AD7865开始进行采集,当锁存一次数据后,ad7865ctl输出一个clkn的触发同步信号,使得触发模块进入trigger状态,在此状态中不断判断采样数据是否达到触发电平,并将数据写入环形存储器中,当满足触发条件后,触发模块输出环形存储器的触发地址并锁存,写数据直到满足触发模式的触发深度。其部分源代码如下所示。

always @(posedge clkin or negedge rst)

2.3 USB2.0数据传输

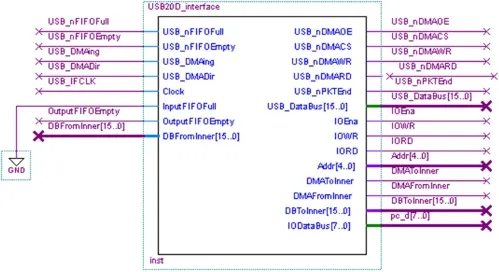

数据存入FPGA内部开辟的环形存储单元后,通过专用的CY7C60381芯片进行DMA传输,DMA操作允许控制器与功能接口之间数据的透明传输。一旦设置了DMA操作,则不需要微控制器的干预。每个端点有一对DMA_REQ和DMA_ACK信号,通过编写相应的FPGA控制代码,CY7C60381芯片在数据传输s时被视为一个高速FIFO,通过系统高速时钟同步写入,再通过上位机的动态链接库函数以DMA方式高速读出,其控制原理与FPGA接口模块如图四所示。

3 结束语

通过实际测试,表明此设计方案与预期要求基本一致。由于可编程逻辑器件(FPGA)具有丰富的可编程性与丰富的I/O引脚,此方案可方便的进行在线修改而不需改动硬件电路,具有较高的灵活性,可靠性及稳定性,此方案也可应用于频率测量、冲击类设备的测试等领域。

[1] 彭鹏,田书林,邱渡裕.基于FPGA的CPU多UART的串行通信接口实现[J].自动化信息,2008,03,41

[2] 周润景,图雅,张丽敏 基于Quartus的FPGA/CPLD数字系统设计实例[M].北京 电子工业出版社,2007

[3] 华清软件嵌入式培训中心 FPGA应用开发入门与典型实例[M].北京.人民邮电出版社,2008

王琳.男,(1961-),陕西西安人,从事电气控制理论的教学和研究工作

Terminal Velocity Test Technology of Incline Impact Tester Based on FPGA

Wang Lin1,Dong ZhenHua2

(1.Xi’an Railway Vocational & Technical institute,Xi’an Shanxi,710016; 2.Xi’an JieSheng Electric Co’LTD,Xi’an Shanxi,710119)

In order to assess specimen when hit from trapezoidal wave resistance to impact strength,this paper proposes a trapezoidal wave impact test measurement and control system based on FPGA.According to practical test,the project proved to be flexible,reliable,stabile.

FPGA;Trapezoidal Wave Impact;Shock Wave Test

图四 控制原理与FPGA接口模块