一种基于中频信号的雷达原理实验仪

甘 轶, 邓有为, 张智军

(空军工程大学 航空航天工程学院,陕西 西安 710038)

0 引 言

电子类课程体系中“雷达原理”课程占据十分重要的地位,但由于其概念抽象,原理深奥,模型复杂,工作和处理方式多,学习难度较大。受限于雷达实装缺失、雷达实验仪器昂贵稀少等因素,院校难以有效开展雷达原理方面的实验。另一方面,随着计算机技术、数字信号处理技术的发展,雷达信号产生、信号处理完全可以依靠先进的数字处理器件DSP和大规模集成电路FPGA予以实现。这种趋势下,使得基于雷达中频信号建设一个仿真各种雷达信号及其工作状态以开展雷达原理实验内容的低成本实验室成为可能[1-5]。

本文介绍一种基于雷达中频信号的原理实验仪的设计与研制,能够实现真实雷达中频信号产生、接收处理、解析上报,能通过计算机进行通信控制和结果显示,为雷达发射信号测试、回波测试、处理演示、抗干扰等一系列课程内容提供了实验手段,对深化学员理解雷达理论具有重要的意义。

1 系统功能与指标设计

1.1 功能设计要求

(1) 提供关键信号节点的输入输出接口;能够与计算机进行通信,受计算机(上位机)操作软件的控制,并能将处理结构上报到上位机进行显示;

(2) 基于PD雷达体制,产生60 MHz中频信号,并按控制要求形成中频信号的波形调制,可以设置简单脉冲、PRF可变,PM调制、LMF连续波等信号形式;可设高、中、低重频模式;

(3) 能够设置成搜索扫描模式和跟踪模式。在任意模式下,完成中频信号的采样、加权处理、FFT、脉冲压缩、CFAR、MTI、模糊解算等处理,并解算出模拟目标参数;

(4) 能够产生设定模式下的干扰信号,并根据指令调整模拟目标与干扰信号的幅度,实验不同干扰信号下的处理效果。

(5) 模拟天线扫描,关联数据处理过程与结果。

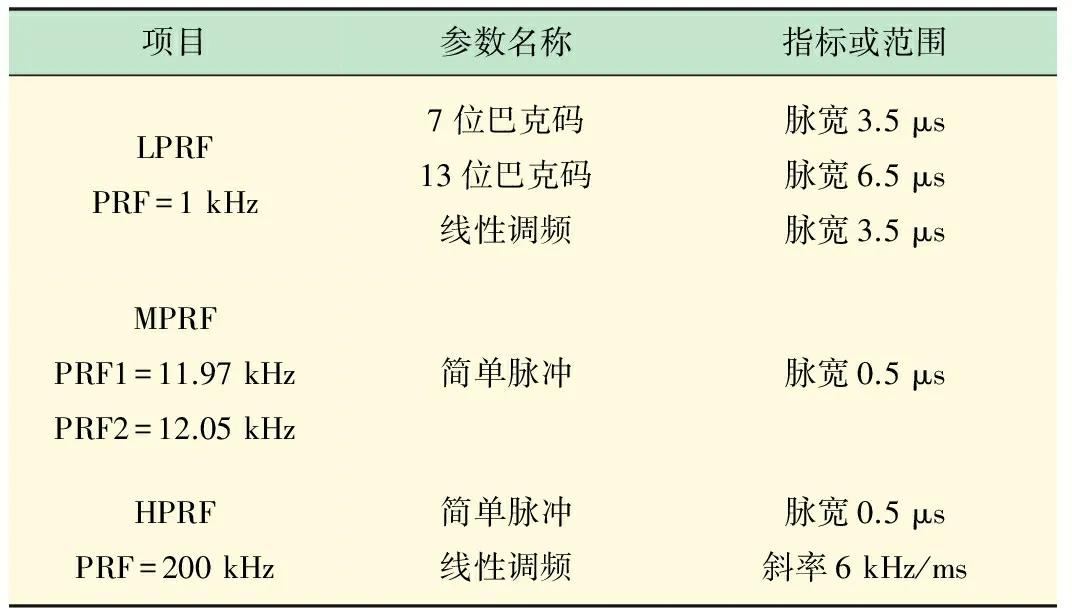

1.2 关键指标设计

实验仪主要指标设计包括脉冲重频、脉冲宽度、信号样式与带宽;其主要参数如表1所列。

表1 关键设计指标

而对于实验仪自身产生的模拟目标和干扰信号,两者具有独立的频率和幅度控制。其中按照雷达工作波长λ=0.03 m设计,模拟目标多普勒频移范围为±60 kHz;干扰信号预置不同干扰样式,预置高斯白噪声调幅干扰信号样式。模拟目标回波与干扰信号强度分别可设定,模拟目标幅度设定采用256等级,干扰设定64等级。

对于信号处理环节,设定可选处理模式和门限参数。处理模式分为相参、非相参处理。对于门限调整则按照CFAR处理机制,预置参考门限。

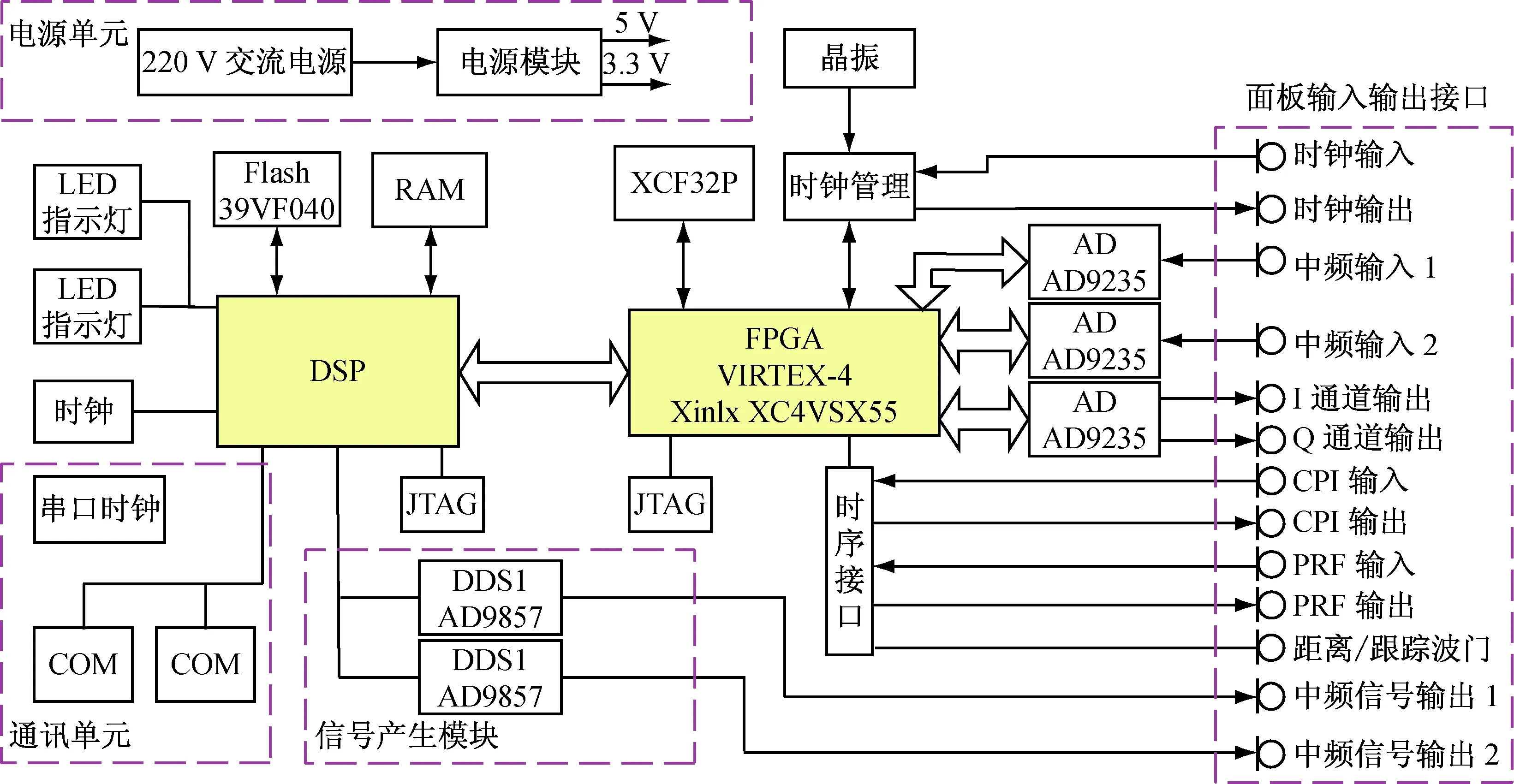

2 总体技术方案

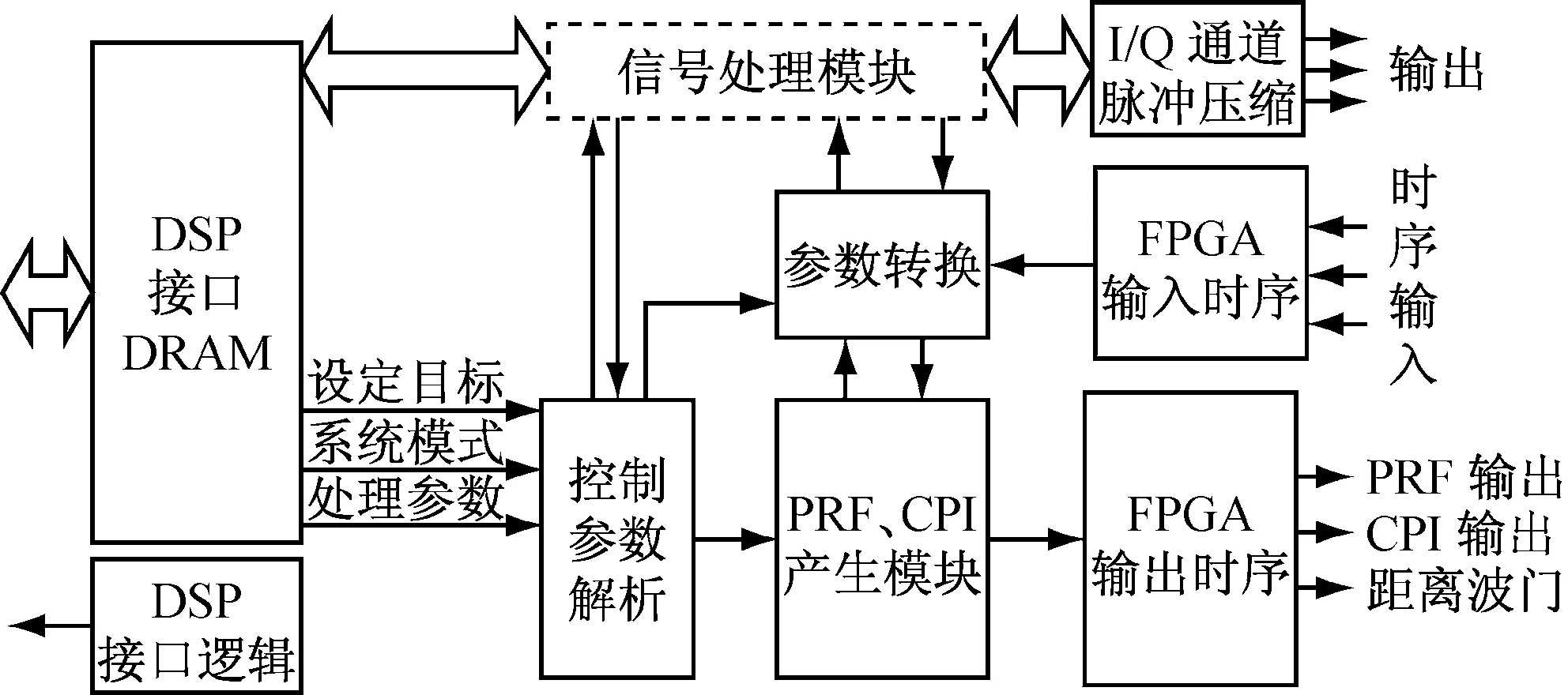

规划实验仪主要针对雷达中频信号进行硬件设计,实现采样、数字信号处理,完成雷达核心功能,并能输出节点的实际信号,用于实验。基本方案是基于DSP和FPGA用硬件构成中频信号产生、目标模拟、采样、雷达信号处理的小型系统,实现雷达发射信号模拟、回波信号模拟,提供时序脉冲输出,能够通过上位机实现参数设置与结果输出[6-8]。其总体技术方案框图如图1所示。

图1 总体构成框图

实验功能主要依靠DSP和FPGA构成的处理系统实现。其中DSP主要负责与上位机的通讯,解析上位机的控制命令,按要求进行中频信号产生的控制,并能接收FPGA模块对信号的一次硬件处理结果,按照PD雷达数据处理机制实现对目标数据处理、解算,最终将目标数据和状态通过通讯单元上报给上位机显示。

FPGA模块主要负责对输入信号的AD数据流进行处理,完成模拟回波信号的加权、脉冲压缩、FFT以及恒虚警等信号处理,并将处理结果通过并行总线输出给DSP模块[9]。FPGA模块中还实现了时序逻辑的输出,依据上位机的控制指令要求,产生不同的脉冲重复频率PRF,形成雷达处理节拍CPI时序,并按距离设置和跟踪波门产生距离/跟踪波门[10-11]。上述信号均能通过视频脉冲形式进行输出,方便测试。其中主要器件选型列表如表2所示。

3 主要功能设计与实现方法

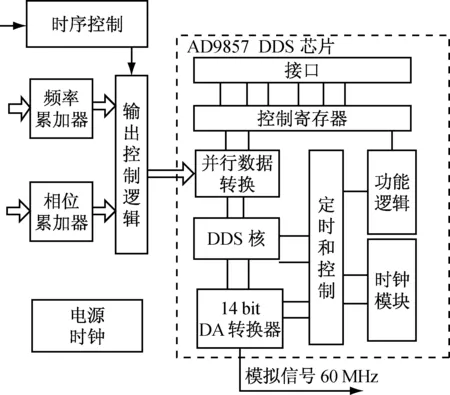

3.1 回波与干扰信号产生

回波与干扰信号的产生是依赖于两个DDS模块实现的。其中一个模块负责完成雷达目标回波信号产生,而另一个主要负责按照设定的干扰样式进行干扰信号形成。核心芯片为AD9857,是一款14 bit高性能的数字上变频器,内部集成一个32 bit正交DDS,实现8 bit的输出幅度控制;其信号产生结构如图2所示。

表2 主要器件选型表

图2 信号产生结构

基带信号参数改变时,DSP芯片更新基带信号波形并写入存储器。

模拟目标参数是按照上位机设定的初值进行,可以设定为距离-速度关联。其中模拟目标距离R指标要求为0.15~150 km,距离分辨为50 m。本设计中采用50 MHz时标,距离设置采用16 bit,则距离迟延数值N(R)与目标当前距离设定值R的控制关系为:

(1)

模拟目标多普勒频率相位累加器时钟采用10 MHz,16 bit字长,保证2 bit有效相移位,采用14 bit-ADC,相位累加器的加数N(F)与fd的控制关系为:

(2)

当fd小于零时,N(F)为补码。在最高速度下,变化单位距离所用时间作为软件定时时间,采用16 bit累加法控制距离运动,满足距离-多普勒同步运动。

将回波基带信号通过DDS调制和转换输出,中心频率为60 MHz。干扰信号的产生与目标回波信号产生类似。

3.2 采样与处理

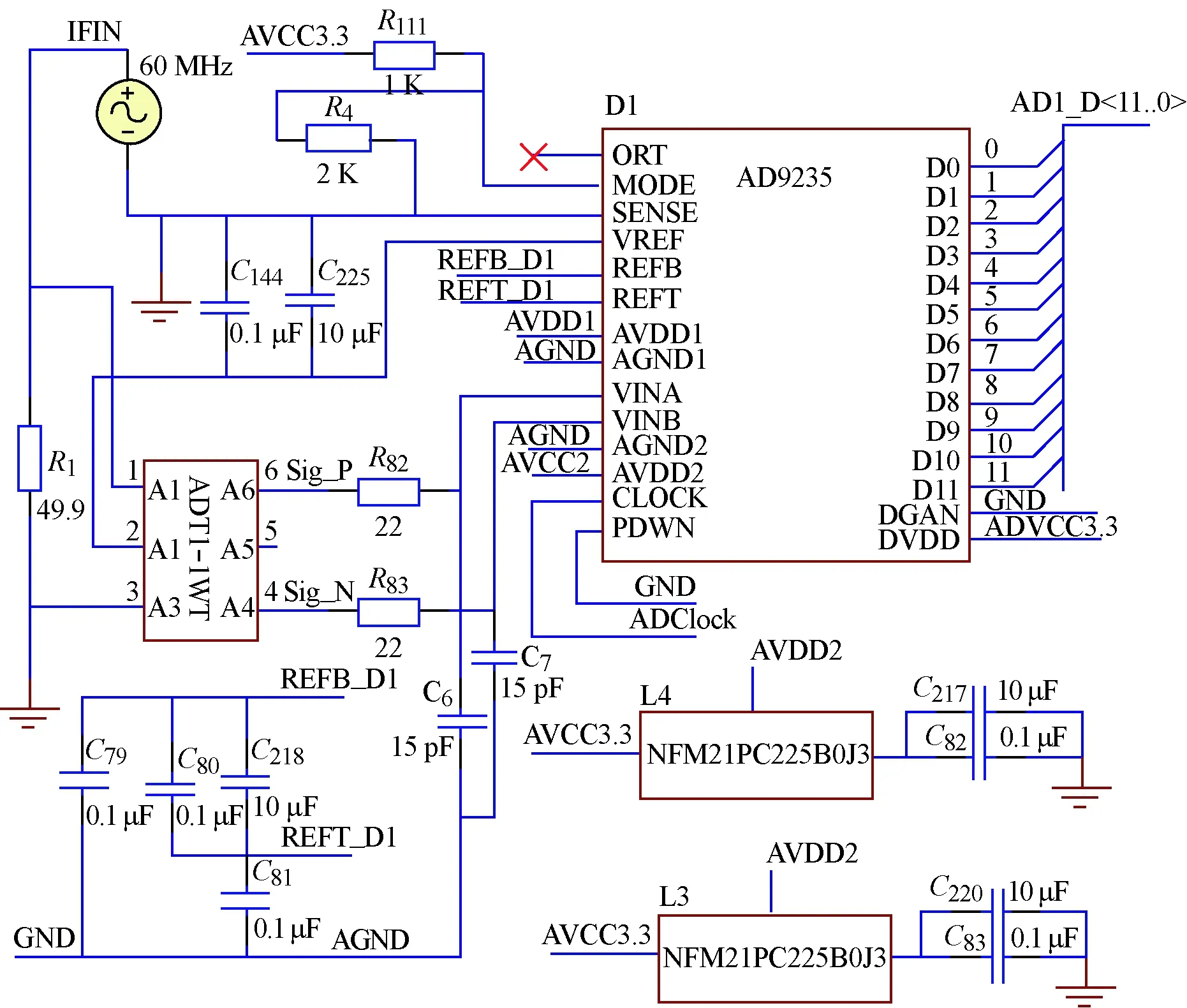

系统设计是在限定信号带宽的基础上进行的[12]。采样电路采用AD9235进行设计,其转换精度12位,采样频率48 MHz。通过数字混频、滤波方式实现信号的变化。由于中频60 MHz,采样48 MHz,故混频NCO频率为12 MHz。其中采样电路部分设计如图3所示。

图3 采样电路的设计

考虑到滤波器的影响,经过抽取后的数据率应大于等于信号带宽的1.25倍,在信号带宽为2 MHz条件下,抽取后的数据率应大于2.5 MHz。在LPRF及MPRF模式下,选取抽取率为8,则抽取滤波器的阶数为160阶,抽取后数据速率为6 MHz。在HPRF模式中,选取数据抽取率为16,抽取后数据速率为3 MHz(48 MHz/16)。

3.3 信号处理与检测

雷达信号处理与检测主要依靠Xilinx公司的一片XC4VSX55高性能的数字信号处理FPGA实现,该器件具有SLICE、BLOCK RAM、DSP48、DCM等丰富资源,功能强大。对信号的主要处理结构如图4所示[10-11,13]。

图4 信号处理主要结构

根据处理结构和外部接口关系,可以把FPGA进行功能分区,如图5所示。

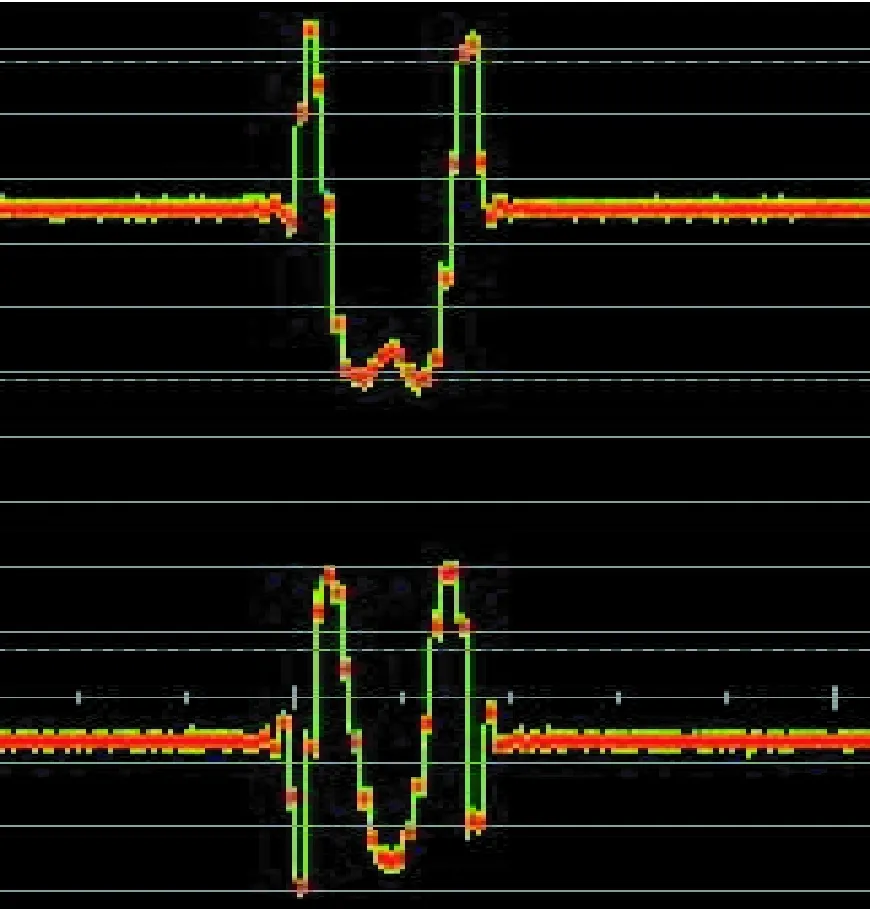

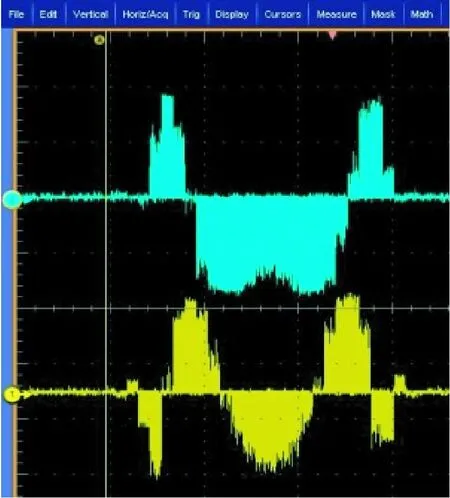

下变频后信号I、Q由AD9765芯片进行DA转换为模拟信号,并通过AD8047进行两级放大输出,供测试观察。在LPRF模式下(线性调频)实测的波形如图6所示(测试仪器Tektronix DP07054)。

[7]的仿真图对比,IQ通道信号输出正确。另外设计中MTD采用8点FFT实现,恒虚警采用两边单元距离单元平均算法[14],保护单元为2,平均单元为8。在HPRF时进行频率分析,FFT点数为1 024点。

图5 FPGA的功能分区

图6 实测的IQ通道信号

3.4 数据处理

数据处理部分以TI公司的TMS320C6416高性能定点数字信号处理器为核心进行设计。该器件最高工作时钟600 MHz,可达4 800 MIPS。主要硬件资源有128 Kb L1P cache, 128 Kb L1D cache, 8 Mb L2 cache。两个外部存储器接口(EMIF),EMIFA为64 bit,EMIFB为16 bit,共1280M字节外部地址。

数据处理部分主要完成MPRF、HPRF模式下解模糊计算。其中MPRF模式下距离模糊解算依据PRF1、PRF2下测得距离Rprf1、Rprf2确定。在HPRF模式中以CPI为单位时间进行处理,对节拍内不同的PRF上同一个距离单元的数据做FFT运算。关于信号强度估计、距离门、频率量一次给出在DSP中进行目标参数确定[12-13]。

3.5 输出与通讯接口

试验仪设计了时钟、中频RF、CPI、PRF等信号的输入、输出接口。工作时,单机可以依靠输入输出接口自环进行工作,以可以双机互联工作。互联时,一台设备及上位机实现目标初值设置,产生目标,并提供时间基准输出;另一台设备接收处理完成目标检测处理和上报显示。

与上位机的通讯采用串口通信。波特率为115.2 kb/s,分别设计上下行通讯协议。协议按包进行,每包数据自定义数据字帧头、类型标识、数据内容、校验与帧尾。其中数据内容包括目标方位、俯仰、距离、速度、备份字节构成,每信息2 byte。下行协议主要传输上位机给出的状态控制、初值设定。

4 结 语

基于DSP与FPGA构成信号处理系统,可以方便地对系统进行升级和功能扩展,方便、灵活的模拟产生不同雷达信号样式、设置不同目标的参数,开发不同的处理方法,为雷达信号处理提供了有效的调试平台,加深了对雷达工作机理的理解,大大降低了对雷达实装的依赖,具有很好的应用前景。

参考文献(References):

[1] 梁 丽. 基于FPGA的雷达信号处理系统设计[D].南京:南京理工大学,2006.

[2] 杨 剑. 数字化雷达通用信号处理机设计[J].电路与系统学报,2009,14(4):25-28.

YANG Jian. Design of digital radar universal signal processor[J].Journal of Circuits and Systems,2009, 14(4):25-28.

[3] 张智军,夏海宝. 雷达信号处理教学实验系统的研制[J].实验室研究与探索,2012(4):0148-04.

ZHANG Zhi-jun,XIA Hai-bao. Development of an Experimental System for Radar Signal Processing Teaching[J]. Research and Exploration in Laboratory, 2012,31(4):0148-4.

[4] Skolnik M I. Introduction to Radar System[M]. 3rded. New York: McGraw-Hill Companies, 2001.

[5] 任宇峰. 基于虚拟仪器技术的雷达信号模拟器设计[J].现代电子技术,2010,33(19):67-70.

REN Yu-feng. Design of Radar Echo Simulator Based on Virtual Instrument Technology[J]. Modern Electronics Technique,2010, 33(19):67-70.

[6] 杨鸿鹄, 许蕴山. 基于FPGA+DSP的雷达回波发生器设计[J].电子技术应用,2009,35(12):57-60.

YANG Hong-hu, XU Yun-shan. Design of a radar echo generator based on FPGA and DSP[J]. Application of Electronic Technique, 2009, 35(12): 57-60.

[7] 孙实泽,杜春鹏. 多体制雷达视频模拟器设计及实现[J] .中国雷达技术论坛, 2008, 31(7):014-04.

SUN Shi-ze, DU Chun-peng. Design and Realization of Multi-system Radar Emulator[J]. Modern Electronics Technique, 2008, 31(7):014-04.

[8] 邱燕军,申功勋. 基于DSP+FPGA的高速信号采集与处理系统的信号完整性分析[J]. 测控技术,2007,12(26):12-15.

QIU Yan-jun, SHEN Gong-xun. Analysis on Signal Integrity of High Speed Signal Collection and Processing System Based on DSP and FPGA[J].Measurement & Control Technology, 2007,12(26):12-15.

[9] 周 杰,刘 鎏. 一种TMS320C6000 DSP与FPGA通讯方法的研究[J].硅谷, 2010(24):88-89.

ZHOU Jie, LIU Liu. Study of a communication method between TMS320C6000 DSP and FPGA[J].Silicon Valley, 2010(24):88-89.

[10] 张建华.PD雷达接收机及信号处理系统仿真研究[D]. 成都:电子科技大学,2006.

[11] 刘冬利.雷达中频信号直接采样与正交相干检波的设计与实现[J].现代雷达,2001,23(3):38-41.

LIU Dong-li. The Design and Implementation of Radar IF Signal Sampling and Quadrature Coherent Detection[J]. Modern Radar,2001,23(3):38-41.

[12] 车志超.基于FPGA的数字中频接收机设计[J].探测与定位,2011,6(2):35-39.

CHE Zhi-chao. Design of Digital IF Receiver Based on FPGA[J]. Detection and Location, 2011,6(2):35-39.

[13] 戈 稳. 雷达接收机技术[M].北京:电子工业出版社,2005.

[14] 马 健,王晟达. CMCAM恒虚警检测器性能分析[J]. 空军工程大学学报, 2009(4):29-32.

MA Jian,WANG Sheng-da. Performance analysis of CMCAM CFAR[J]. Journal of Air Force Engineering University,2009(4):29-32.

[15] 郭 博. 机载PD雷达系统的模拟与仿真[D].西安:空军工程大学工程学院,2009.

[16] 向道朴. 一种通用雷达回波模拟器的设计与实现[J].现代雷达,2007,29(10):84-86.

XIANG Dao-pu. Design and Implementation of a General Digital Radar Echo Simulator[J]. Modern Radar, 2007,29(10):84-86.