一种低功耗水下多通道实时采集存储装置的设计

宋 丹,任勇峰,姚 宗

(中北大学仪器科学与动态测试教育部重点实验室,太原030051)

随着科学研究深度的日益提高,要求采集存储装置在能满足各种信号采集调理的同时,可实现低功耗、高可靠性、高集成度以及能适应复杂多变的环境。

1 系统总体结构设计

该数据采集系统主要由信号调理电路、A/D转换器、FPGA控制器,FLASH存储器、USB单片机、电源管理电路、时统信号接口电路等构成。其中,FPGA作为内部控制器,控制整个系统完成信号采集存储、读数、擦除等操作。

系统由外部启动触点启动上电,FPGA配置完成后进行系统状态检测,即USB硬件接口检测。

状态检测结束后,若确认USB电缆未与上位机连接,在FPGA的控制下,系统通过锂电池负责给压力传感器和惯性组合传感器供电,并对10路压力信号和6路姿态信号分别进行调理后送入一组16选1模拟开关,选通输出模拟信号,并经过跟随、分压、跟随电路调理后,送入A/D转换器转换,转换后的数字量由FLASH进行存储。

状态检测结束后,若确认USB电缆与上位机连接,此时可对系统进行读数/擦除操作。上位机发出读数/擦除指令后,通过USB接口芯片处理相应指令后,FPGA启动读FLASH模块并将数据送往上位机进行存盘和处理或启动擦除FLASH模块对FLASH进行擦除操作。系统框图如图1所示。

图1 采集系统框图

2 压力、姿态信号调理电路设计

2.1 压力信号调理电路

系统选用的10路压力传感器要求采用1.5 mA恒流源激励,传感器内部采用惠斯通电桥结构,差分输出,输入输出阻抗典型值为3.5 kΩ,最大值为4 kΩ。根据传感器供电要求,本设计采用LM134构成1.5 mA恒流源激励给传感器供电,考虑到传感器最大输出阻抗为4 kΩ,产生的共模电压达6 V,根据LM134最小供电压差2.5 V要求,此处采用9 V电源作为LM134的供电输入[1]。

本设计采用单电源(+3 V~+12 V)供电的仪表放大器AD623,其可通过改变增益可调电阻实现增益编程,最高增益设置达到1 000倍。其中增益可调电阻计算公式为 Rg=100 kΩ/(G-1)[2]。

根据传感器信号输出范围-10 mV~145 mV,要将其调理到0~5 V送给采集电路,AD623设计放大倍数为30.4倍,可得信号的输出范围-0.304 V~+4.408 V,再加上+0.5 V的参考电压,则最终信号调理输出范围为+0.196 V~+4.908 V。压力传感器供电及调理电路如图2所示。

图2 压力传感器供电及信号调理电路

2.2 姿态信号调理电路

在6路姿态输出信号中,3路加速度输出信号范围为0~5 V,采用电压跟随电路设计,如图3所示。跟随电路作用:提高输入阻抗,降低输出阻抗,提高其驱动负载的能力,使抗干扰能力大大提高。

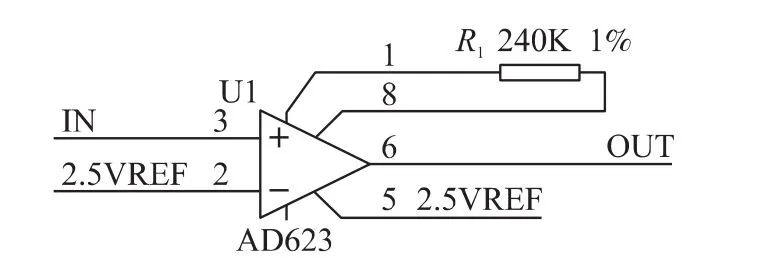

三轴向角速度输出共模电压为2.5 V,差模电压峰峰为3.3 V,该信号由AD623进行放大调理,其中AD623为差分输入,设计差分正端输入角速度信号,差分负端输入2.5 V参考电压,进行1.42倍放大到0~5 V范围,仪表放大电路如图4所示。

图3 电压跟随电路

图4 姿态信号仪表放大电路

3 电源管理电路

3.1 自保持功能

启动信号为无源触点,启动信号闭合后系统上电,并具有自保持功能。当启动触点闭合后,电池电源对电容C1~C3充电以建立电压,起到上电延时的作用,有效地防止了误启动。当电压达到电源芯片使能端有效阈值时,电源芯片输出工作电源系统上电,之后内部控制系统产生有效使能信号ENAVDD完成供电自保持,如图5所示。

3.2 防止水中误启动的措施

针对系统浸入水中工作的情况,我们对系统进行了防止水中误启动的电路设计,并进行了水中工作测试试验。

测试水域阻抗为8 kΩ,若系统内部的串行启动电阻太小,会导致启动线通过水介质构成通路,启动上电,且在记录完毕后不能掉电。按冗余设计考虑,水域阻抗为3 kΩ,最终启动触点接口电路如图5所示。

图5 启动触点接口电路

此次设计选用的电源模块MIC29302的阈值电压为1.4 V,整个系统采用两节锂电池供电,正常工作电压(电池供电输入)在7 V~8.4 V之间,经过二极管后电压(BATVCC)保持在6.3 V~7.7 V之间,设计应保证:(1)两根启动信号线未浸入水中时,启动触点闭合后,在最低的电压6.3 V仍可以正常使能启动。(2)两根启动信号线浸入水中时,系统在最高的电压7.7 V仍不发生自行使能启动。经计算可知,在第一种情况下,电源的使能电压为1.44 V,高于电源模块的阈值电压,系统正常工作。在第2种情况下,水的阻抗按照3 kΩ进行计算,电源的使能电压为1.34 V,低于电源模块的阈值电压,防止了水中误启动。

经过实际测试,当水的阻抗大于3 kΩ时,系统启动线浸入水中后,不会自行启动上电。

3.3 低功耗的实现方式

系统设计时选用低功耗器件,自身功耗相对较小。同时设计保证:当系统检测到与上位机连接后,可进行读/擦除等操作,此时由USB接口对系统供电(USB总线可提供5 V电压、500 mA电流,对于功耗较小的设备来说这是非常有效的[3-4])。工作流程为:内部控制系统有效使能信号ENAVDD,通过电源管理模块给系统掉电,此时恒压源和恒流源不给传感器供电且采集电路也未工作。整个系统采用USB接口供电,有效地降低了电池的功耗。如图6所示。

图6 USB接口给系统供电电路

4 时统信号接口设计

时统信号是整个系统的时间基准,其到来时刻作为系统的时间零点,因此有效接收时统信号对系统至关重要[5]。

4.1 硬件电路设计

FPGA端的初始状态由上拉电阻R3保持高,外部时统触点闭合后,驱动光耦给FPGA输出时统信号,此时FPGA端为低,表明时统信号到来。

图7 时统触点接口电路

4.2 时统信号接收消抖逻辑设计

在实际使用过程中,系统往往受到复杂的电磁干扰,时统信号在闭合过程中伴随着信号抖动,这就导致时统信号可能在低有效的情况中出现高电平的尖峰脉冲干扰,我们在时统信号接收逻辑中采取了有效消抖方式,确保时统信号接收的及时可靠[6]。

常用的消抖方式为信号延时消抖,原理是对外部信号进行高频采样,当连续采到N个点发生跳变,消抖后的内部信号随之改变[7]。该种方式的缺陷是:若出现均等时间的干扰脉冲,且干扰信号周期小于采样信号周期,那么消抖后的内部信号始终不会发生跳变。如图8所示。

图8 延时消抖缺陷示意图

时统信号属于电平信号,本设计选用抽样判决法对时统信号进行消抖。该消抖算法是基于概率统计方法的。系统每隔时间τ对时统信号进行一次采集,在FPGA内部调用15 bit的内部寄存器,将第1次采集的信号放在寄存器的第1位,然后每采集一次,内部寄存器移位一次,相当于对时统信号进行加窗判断,并滚动执行。直到判断出15 bit的寄存器中有10 bit的低有效,那么便认为是有效的时统信号。如图9所示。

图9 抽样判决消抖示意图

设寄存器的位数为m,寄存器中低电平的个数设为n,且

该实例中:当η≥66.7%,认为输入状态发生了由高到低的变化,真正的时统信号到来。当η<66.7%,认为出现了干扰信号。为了使系统运行可靠,可根据实际触点的抖动情况对寄存器的位数以及百分比例进行调整,从来对干扰信号进行有效的剔除。

5 逻辑设计

阶段时刻标记S1~S7内容如下:

S1 启动触点闭合;

S2 采集装置上电复位待机;

S3 采集装置通过USB接口与上位机连接,由外部USB电源供电,并进入上电复位待机状态;

S4 判断USB在线指令USB_ONLINE,若USB不在线USB_ONLINE=“1”,则FPGA下发供电自保持指令有效ENAVDD=“1”,系统由内部电池供电工作,同时启动采集装置进入采编存储状态。在该状态下,先从前向后依次判断存储器16个分区是否记满,若有空区域,则将本次上电采编数据存入该空着的存储分区中,并启动30s采编存储计时器计时;若判断到16个存储分区已记满,则直接跳入S7,系统掉电。

若USB在线USB_ONLINE=“0”,则FPGA下发供电自保持指令无效ENAVDD=“0”,系统由上位机USB电源供电工作,采集装置进入暂停读数的待机状态,此时可由上位机软件控制进行采集装置分区读数与擦除操作。

S5:接收到采集装置时统信号;

S6:采集装置时统信号经过30ms消抖判断有效时,采编帧计数清零;

S7:停止采集,FPGA下发供电自保持无效指令ENAVDD=“0”,系统掉电。

S8:上位机操作完毕,USB电源断开后,采集装置掉电。

图10 工作时序设计

6 数据的分区存储设计

根据技术指标要求以及上电时间、采样率和帧格式要求,经计算知:系统一次上电记录数据量约为12 Mbytes,为保证冗余设计,将系统分为16区,每区均为16 Mbytes的容量设计。

系统上电后,每次都从第1区开始顺序检测是否有数据,如果第1区没有数据,则把该次启动采集的数据写入第1区,系统每次上电工作30 s后自动掉电完成此次记录;若第1区有数据,则依次检测剩下各区的记录情况,直到检测到某区无数据才把该次启动采集的数据写入该区。若16区都已记满,再次启动采集后,系统上电后自动掉电,不论怎样启动采集也不会把数据覆盖后再写入,除非执行擦除操作把存储器中的数据清空[8]。

数据的分区存储设计,保证了系统在不擦除的情况下实现多次启动存储操作,若发生误启动状况,确保数据的及时有效存储,提高了系统的冗余性和可靠性。

7 结束语

经过多次试验,系统能有效接收上位机命令并执行相应操作、能采集数据并进行多次启动后分区存储。在水中测试过程中未出现误启动状况,系统运行稳定可靠。该设计方案已在某试验中得到应用。

[1]LM134.Data Sheet[EB/OL].http://www.national.com,2000,3.1-14.

[2]AD623.Data Sheet[EB/OL].http://www.analog.com,1997 ~2008,16.1-24.

[3]萧世文.USB 2.0硬件设计[M].北京:清华大学出版社,2002:8-10.

[4]范延滨.微型计算机系统原理、接口与EDA设计技术[M].北京:北京邮电大学出版社,2006:389-392.

[5]李玉峰,韩晓红,刘洋,等.基于FPGA的高速数据采集系统的实现与性能分析[J].电子器件,2012,35(6):709-712.

[6]姚宗.某型固态数据记录器的研制[D].中北大学,2010.

[7]常高嘉,冯全源.基于FPGA的高速数据采集系统的设计与实现[J].电子器件,2012,35(5):615-618.

[8]文丰,赵艳利,甄国涌.基于FPGA的高速数据采集存储系统设计[J].电子科技,2009,25(5):235-238.