基于PDP扫描驱动芯片的LQFP封装热特性研究*

于 冰,张 頔,刘斯扬,孙伟锋

(东南大学国家专用集成电路系统工程技术研究中心,南京210096)

近年来,由于半导体集成电路和封装产业的蓬勃发展,功率集成电路逐渐朝着大功率、小尺寸、大量生产及低成本的方向发展,芯片的发热密度显著提升[1~2]。如果不能将产生的热量及时有效地散发出去,就会造成芯片内部热量的积累,使得结温上升[3~4],影响芯片的可靠性,甚至造成芯片功能失效[5]。因此,深入研究芯片热特性对实际驱动电路及芯片的设计将能起到很好地辅助作用。

在实际应用中,常常会通过减小芯片面积的方式来减小生产成本,但这必须是以芯片可以正常工作为前提的。本文以实验室研发的LQFP封装的96路PDP扫描驱动芯片为载体,以减小芯片面积为切入点,使用有限元法对该封装类型的芯片热特性进行了较为全面的研究。为实际的芯片封装及外围设计提供了一定理论指导。

1 集成电路热流路径与热阻网络

为了评估芯片的散热性能,必须建立一个有效的封装热模型来预测,这种方法可以为集成电路的设计提供指导,并及早地提供可行的解决方案。

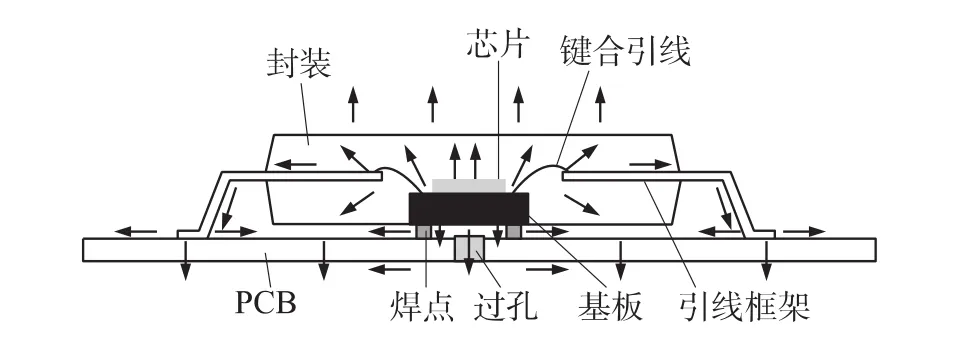

由已有的研究可知[6~10],热阻是一个可以用来很好地表现封装热特性的参数。如图1所示,是一个简单的LQFP封装芯片的结构以及散热路径示意图,暴露在外的散热基板提供了一条主要的散热途径。稳态热阻的标准定义为Rth=(T-Tref)/P,其中,T是我们所关心的温度(如结温),Tref是参考温度,P是稳态功耗[11]。

该类型封装芯片的两条主要散热途径的等效热阻网络如图2所示:①通过封装上表面与空气进行对流换热;②通过基板向PCB传导,然后通过PCB

图1 芯片结构及散热路径示意图

与空气进行对流换热。

图2 芯片散热热阻网络

其中,Rjc_b指结到封装下表面的热阻;Rpcb指封装下表面到PCB下表面的热阻;Rpa指PCB与空气对流换热的等效热阻;Rjc_t指结到封装上表面的热阻;Rta指封装上表面与空气对流换热的等效热阻。

高的热阻意味着差的散热能力,这可能会导致芯片过热问题。而低的热阻可以充分发挥芯片的性能,延长芯片的使用寿命,有利于满足客户高性能和低功耗的需求。因此,理解热阻的含义对于封装的热设计和热分析都是非常有用的。

2 模型假设

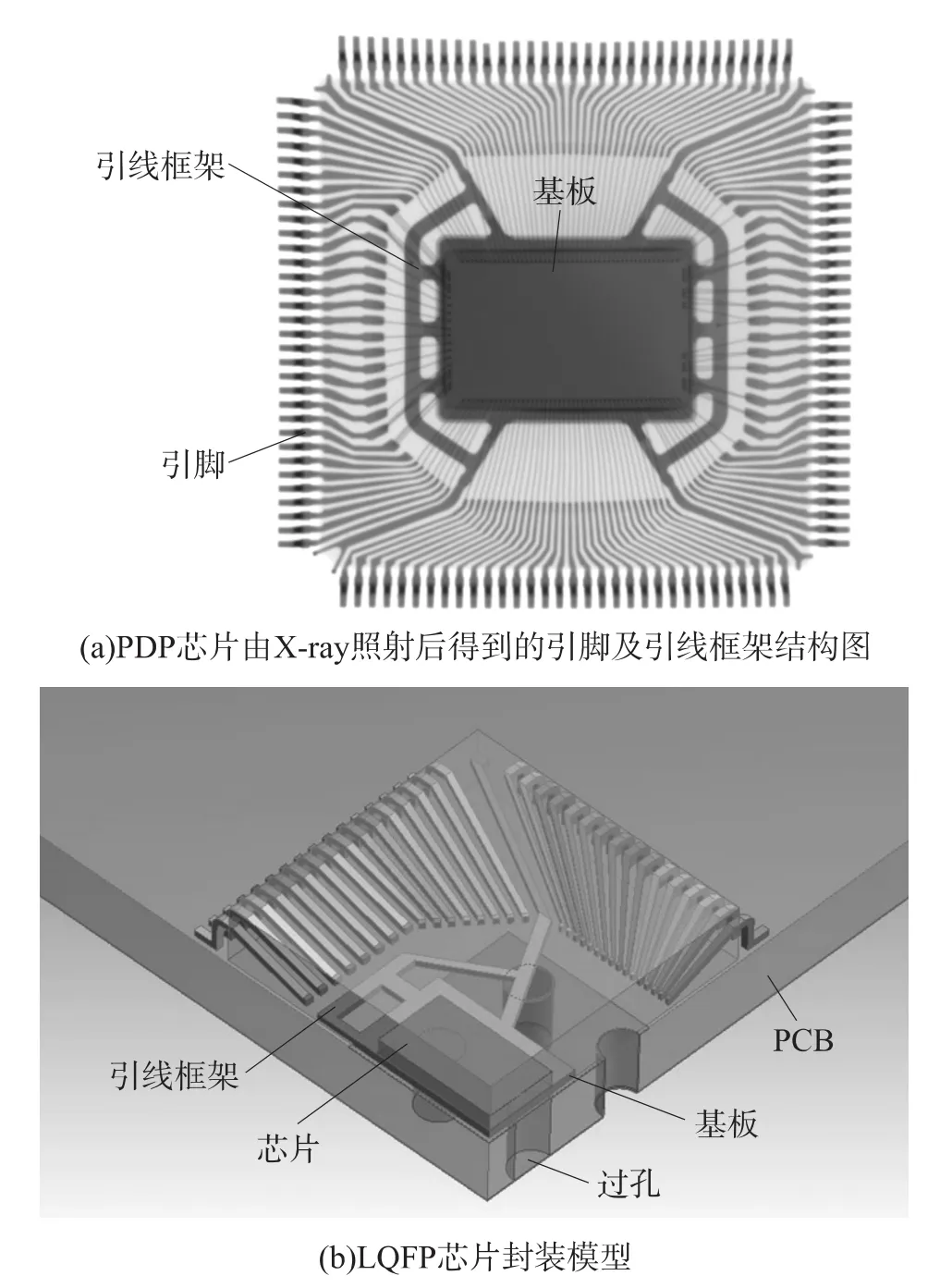

由于实验芯片是完全对称的结构,所以这里只需要构建1/4的芯片封装模型即可。图3(a)为PDP芯片由X-ray照射后得到的引脚及引线框架结构图,借助有限元分析软件ANSYS Workbench构建如图3(b)所示芯片模型。

以上封装数值模拟的条件为:环境温度为22℃,空气对流换热系数12.5 W/(K·℃),输入功率1.5W。模型中PCB详细参数如表1所示。

表1 PCB板各项参数

图3

模型中,我们假设材料间的界面接触是理想的,而且材料的物理属性是固定的且各向同性的,详细参数如表2所示。

表2 材料热导率

3 仿真与测试结果对比研究

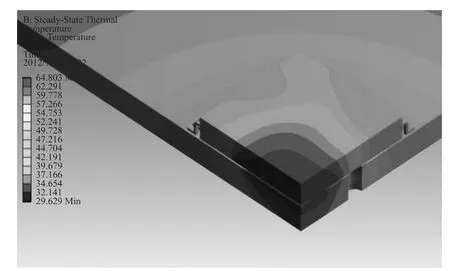

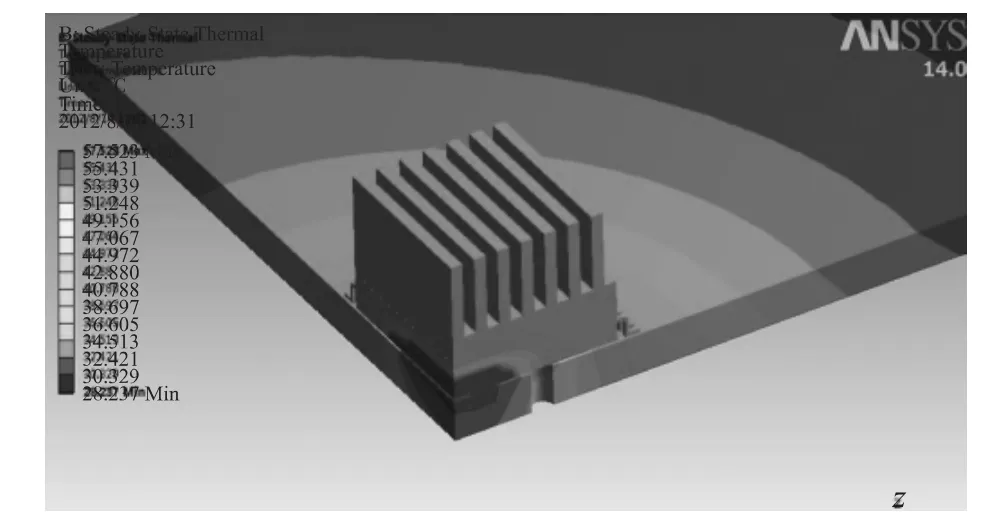

对上面建立的模型进行数值计算,图4为求得的稳态温度分布图。为了对整个芯片的温度分布有一个更直观的认识,图5为全芯片的稳态温度分布图,对比可以发现其温度分布是一致的。

以下是实验室研发的前后三代PDP驱动扫描芯片的硅片尺寸参数,如表3所示。

图4 1/4芯片稳态温度分布图

图5 全芯片稳态温度分布图

表3 3种型号芯片的硅片尺寸

稳态热仿真结果如表4所示。

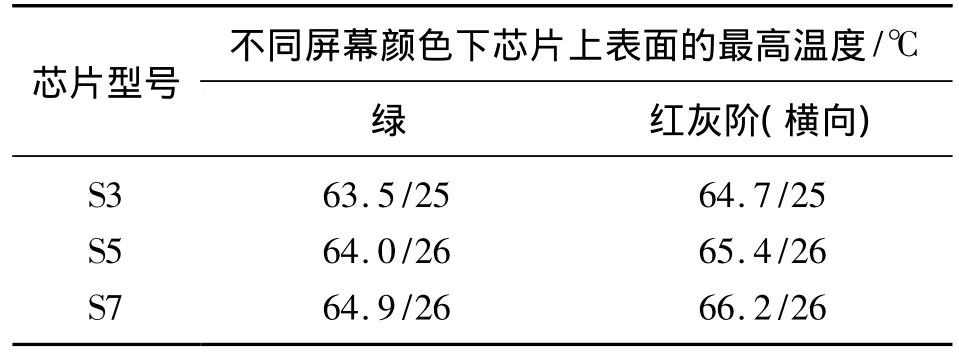

表5所示为的S3、S5和S7 3款芯片上表面最高温度的实际测量结果。

表5 S3、S5和S7芯片上表面最高温度测试结果

分析仿真结果,可以发现S3和S5的最高结温相差很小,而S7的最高结温升高也并不明显,仅比S5高不到1℃。这一结果在实测数据中得到了验证,因此也证实了模型仿真的准确性。

为了理解上述仿真和测试结果,可以从热阻的角度来分析这个问题。表6所示为3种芯片的热阻,其中,Rja为结到空气的热阻。

表6 3种型号芯片的热阻比较 单位:℃·W-1

3种型号的芯片的热阻比较如图6所示,可以发现,结壳热阻Rjc_t和Rjc_b与结到环境的热阻Rja相比是非常小的,改变芯片面积对Rjc_t和Rjc_b有着较明显的影响,尤其是对Rjc_b,但是相对于Rja,其影响却可以忽略不计。而最高结温则是由环境温度和结到环境的热阻决定的,因此,在这种情况下,硅片面积的改变对于芯片的散热性能影响不大。

图6 3种型号芯片的热阻比较

在热仿真中,芯片的最高结温反映了其热可靠性的水平。最高结温是关于封装结构、材料属性、输入功率、环境变量,以及PCB等因素的一个复杂的函数。

4 影响芯片热特性的因素研究

为了进一步比较两条散热途径对整个芯片散热的贡献,并以芯片的最高结温为目标函数进一步提出优化方案,设计了以下4个实验进行比较:

①模拟芯片在实际工作中的情况,对实际中存在空气对流的表面均做对流换热处理;

②在①的基础上,对封装上表面和侧面做绝热处理,即无空气对流换热,其他不做改变;

③在①的基础上,对PCB表面进行绝热处理,即无空气对流换热,其他不做改变;

④在③的基础上,将封装体的热导率由0.3 W/(m·K)提高为400 W/(m·K)(近似于铜)。

4种情况下,仿真所得最高结温如图7所示,分别为65.806℃、68.219℃、373.85℃和330.54℃。

图7 4种实验环境散热能力的对比

由图7可以看出通过PCB散热是该实验情况下的主要散热途径。另一方面,也可以看出单纯提高封装热导率对散热效果的提升并不明显,也就是说通过增加热导率来减小Rjc_t以提升散热性能,其效果并不显著。不难理解,这主要是因为封装上表面的表面积非常有限,Rjc_t相对于Rta小很多,这样结到空气的热阻Rja的减小并不明显。

从图6中,可以发现结到空气的热阻Rja中,结壳热阻Rjc(Rjc_b和Rjc_t)只占了较小的一部分,大部分则是封装到空气的热阻(Rpcb、Rpa和Rta)。这种情况下,要较明显地提高系统热性能,应主要致力于减小封装到空气的热阻。

下面将分别就影响封装到空气的热阻和结壳热阻的因素来进行分析。

4.1 影响封装到空气热阻的因素

封装到空气的热阻主要是由外围电路系统的设计决定的,大致包括以下几个方面:

4.1.1 PCB覆铜面积

不同的PCB覆铜面积下仿真结果如表7和图8所示。

表7 PCB覆铜面积对最高结温的影响

图8 覆铜面积对最高结温的影响

可以发现,增大覆铜面积对于散热性能的提高具有显著的作用。从图9也不难看出,这是因为增大PCB覆铜面积可以较大幅度的减小结到环境的热阻Rja。

图9 PCB覆铜面积对结到空气热阻的影响

4.1.2 PCB过孔数量

分别对基板正下方PCB过孔数为2、6、12、24的情况进行模拟。为了进一步挖掘过孔数量对散热性能影响的潜力,引入了一种理想的极限情况:假设基板正下方全是过孔且注满焊锡,即基板正下方包括PCB板部分在内,全部替换为锡。仿真结果如表8和图10所示。

表8 过孔数对散热性能的影响

图10 过孔数对散热性能的影响

显然,适当的增加过孔数可以有效增强芯片的散热能力。对比24孔和理想情况,其散热性能非常接近,也就是说,当过孔数达到一定数量时,PCB上表面和下表面的热交换已经趋于饱和,此时继续增加过孔数的效果就不那么明显了,当然,这与实际的工作环境是相关的。

4.1.3 空气流速

图11和图12分别为不同空气对流换热条件下芯片的最高结温和热阻值。

从图11和图12可以看出,随着对流换热系数增加,Rja明显减小,最高结温迅速降低。因此,在条件允许的情况下,增大空气流速是增强芯片散热能力非常有效的手段。

图11 最高结温与空气对流换热系数的关系

图12 结到空气热阻与空气对流换热系数的关系

4.1.4 散热片

设计一组对比试验:①不添加散热片;②添加一规则长方体散热片于芯片上表面,材料为铜,厚度3 mm;③将规则长方体散热片改为具有肋片的散热结构,如图13所示,材料为铜,其高度为3 mm。

图13 带肋片的散热片示意图

仿真结果如表9和图14所示。

表9 散热片对散热性能的影响

图14 散热片对散热性能的影响

可以看到,添加散热片对提高散热特性具有很好的效果,它有效地增大了上表面与空气的接触面积,增强了空气对流换热。理论上,肋片越多,其散热越好,但出于成本、生产工艺以及实际情况考虑,肋片数是有限的,这就需要我们去综合考虑了。

综上所述,在电路设计中,尽可能增加PCB有效覆铜面积、过孔数量,以及基板和PCB的接触面积,都能有效地提高系统的散热性能。若不考虑成本,添加散热片和增大空气流速也是行之非常有效的办法。

4.2 影响结壳热阻的因素

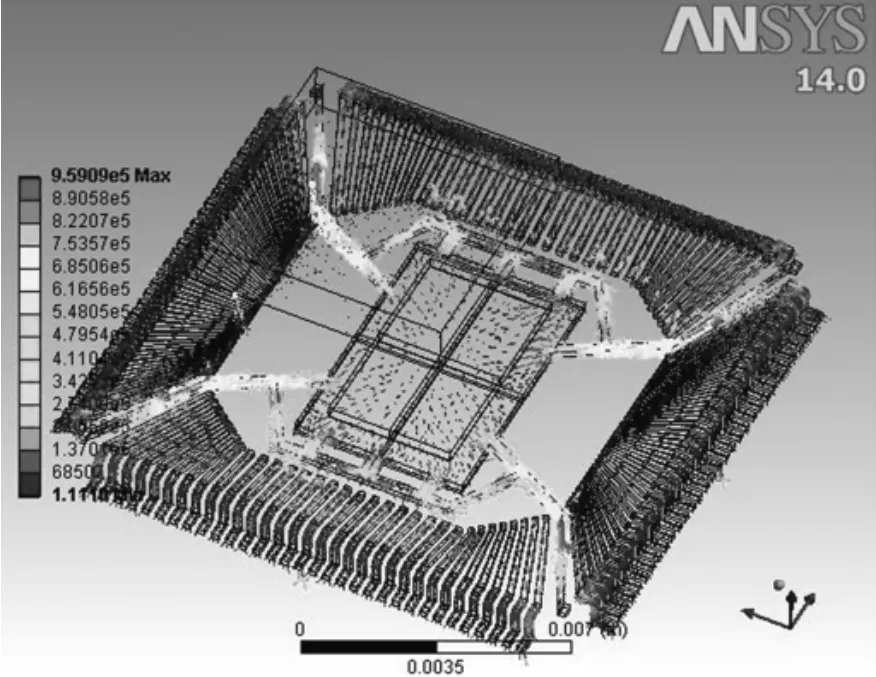

结壳热阻则主要取决于集成芯片设计本身,主要影响因素有封装结构及材料和基板面积等。为此,单独建立芯片工作的模型(不考虑外围电路,PCB板等的影响),仿真结果如图15所示,基板和引线框架对于整个芯片温度的分布有着非常重要的作用,这是因为基板和引线框架热导率非常高,对于热的传导是非常有利的。

图15 芯片稳态温度分布图

图16 芯片热通量图

如图16所示为热通量仿真结果,可以看到引线框的热通量相对于其他部位是非常大的,也就是说引线框在将热量散发到芯片周围这一点上起着很大的作用。因此,增大引线框架的横截面积,合理设计引线框架布局对于提升芯片散热性能有着重要意义。

仿真结果表明,影响结壳热阻的主要因素是基板面积和引线框架设计,以及封装体热导率。封装体热导率与工艺相关,在一定情况下,更改并不现实。所以,基板和引线框架的设计是较为重要的。在工艺和成本允许的情况下,尽可能增大基板的面积、优化引线框架的设计是较为有效的措施。当然,在实际应用中,芯片与基板的连接情况(如是否存在空洞或脱离等)也会对结壳热阻产生很大的影响[12~13]。

图17为基板面积对于芯片热特性的影响(芯片独立工作,不考虑外围电路),其中,缩放因子是对于基准尺寸的长宽所乘的因数。可以看出,基板面积对于芯片热特性有着较显著的影响,在集成电路设计时,可以尽可能地增大基板面积以提高其散热性能。

图17 基板面积对于芯片热特性的影响

5 结语

从以上研究中,可以得出以下结论:①通过在有限元分析工具中构建有效的芯片封装热模型,进而对芯片热特性进行预测,这对于集成电路的设计及应用来说都是非常有意义的。②对于基板裸露的LQFP封装结构而言,通过基板和PCB散热是芯片散热的主要途径,增大PCB板的有效覆铜面积,增加PCB板的有效过孔数,增大空气流速,以及在芯片顶部添加含有肋片的散热片都是增强芯片散热能力的有效手段。③在集成芯片封装设计时,尽可能增大散热基板面积,优化引线框架结构,提高封装体热导率都能使芯片的散热性能得到提升。

为了快捷有效地提高芯片的散热性能,就需要分析芯片的热阻结构,进而确定影响结到空气热阻的主要因素,从主到次进行调整。当然,充分考虑集成芯片设计和实际应用电路设计两方面可以使系统散热性能更为优良。

本文主要针对LQFP封装类型的芯片,论述了影响芯片热特性的主要因素,有着特定的应用背景,有些结论并不适合于其他类型芯片,但其研究方法是相同的,是值得借鉴的。

[1]Szekely V M,Rencz B Courtois.Tracing the Thermal Behavior of ICs[J].IEEE Design and Test of Computers,1998,2(15):14-21.

[2]Roger R Schmidt.Challenges in Chip/Processor Level Thermal Engineering[C]//2004 Inter Society Conference on Thermal Phenomena,2004:738-739.

[3]Anghel C,Io Sierranescu A M,Hefyene N.Self-Heating Characterization and Extraction Method for Thermal Resistance and Capacitance in High Voltage MOSFETs[C]//European Solid-State Device Research,ESSDERC ’03.33rdConference,2003:449-452.

[4]Jenkins K A,Franch R L.Impact of Self-Heating on Digital SOI and Strained-Silicon CMOS Circuits[C]//IEEE International SOI Conference,California,2003:161-163.

[5]Oettinger F F,Blackbum D L.Thermal Resistance Measurements[M].NIST Special Publication 400-86 from Series on Semiconductor Measurements Technology,1990.

[6]贾松良,朱浩颖.集成电路陶瓷封装热阻RT-JC的有限元分析[J].半导体技术,1997,12(6):6-11.

[7]Gao Guohua,Wang Honghui,Yang Guoji.Thermal Numerical Simulation for Advanced Package Development[C]//2009 International Conference on Electronic Packing Technology and High Density Packaging,2009:238-241.

[8]Chen Zhaohui,Luo Xiaobing,Liu Sheng.Thermal Analysis of 3D Packaging with a Simplified Thermal Resistance Network Model and Finite Element Simulation[C]//2010 11th International Conference on Electronic Packaging Technology and High Density Packaging,2010:737-741.

[9]毛章明,罗小兵,刘菊.一种计算DIP芯片结温的热阻模型[J].工程热物理学报,2011,32(2):303-307.

[10]何伟,杜平安,夏汉良.建立封装芯片热阻网络模型的方法研究[J].微电子学,2011,41(1):120-123.

[11]JEDEC.51-1 Integrated Circuits Thermal Measurement Method-E-lectrical Test Method[S].http://www.jedec.org:JEDEC,1995,12.

[12]Lee Han Meng.Thermal Simulation Study of Die Attach Delamination Effect on TQFP Package Thermal Resistance[C]//34th International Electronic Manufacturing Technology Conference,2012.

[13]何延强.功率VDMOS器件失效分析与可靠性研究[D].哈尔滨:哈尔滨理工大学,2010.