基于Siwave与ADS的高频仿真

刘 肃,闫胜刚,王 永

(兰州大学微电子所,兰州730000)

随着高速芯片的快速发展,系统工作频率和布线密度的不断提高[1],信号网络的反射、串扰、振铃效应越来越明显,电源网络的同步时序开关噪声、过冲、地弹等各种电源噪声也越来越严重;随着工作电压的不断降低,电源和信号的噪声容限[1]却在不断变小。这样在大量高速开关器件切换状态时,就会产生噪声,干扰芯片的正常工作,严重时可能造成误操作,甚至损坏芯片。

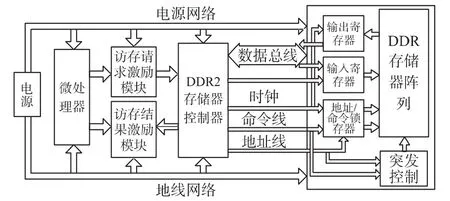

本文以一个8层的PCB和2层的PKG(Package)为研究对象,仿真板上供给到存储器上的电源和信号,针对网络中的完整性问题,采用合适的修改措施,使其能为存储器提供干净理想的电源和信号[2],保证存储器的正常工作。块组成[3],具体结构如图1所示,每个模块都需要电源不断的提供驱动电荷,同时相互之间需要信号线进行信息传递。本文只考虑控制器和存储块上的电源网络阻抗,以及控制器到存储块之间的数据、命令、地址线上的噪声效应。

图1 存储器电路结构

1 存储器结构

2 电源配送网络

存储器的工作主要由微处理器、控制器和存储

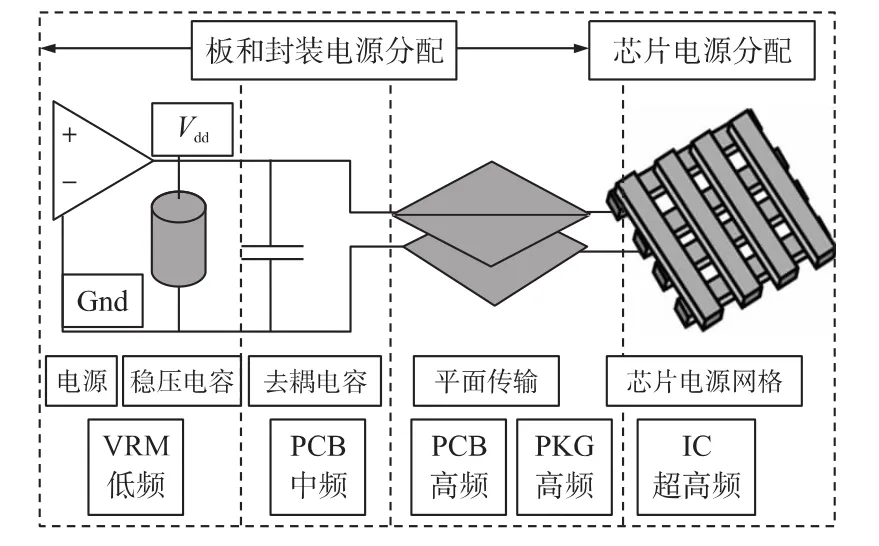

存储器上电源网络的作用是为系统内晶体管提供足够的电荷,理想的电源网络没有阻抗,电压源能为晶体管提供足够的电荷[4]。实际中电源配送网络在不同频率时,存在不同的输入阻抗,当瞬时大电流通过时,会产生电压降和电压波动。配送到控制器和存储块上的高频电源网络结构如图2所示,由稳压块、去耦电容、平面对和芯片网格组成。VRM(Voltage Regulator Module)的频率范围为0~1 kHz,电解电容的频率范围为1 kHz~1 MHz,贴片电容的频率范围为1 MHz~100 MHz(现在也有可用于更高频率的贴片电容),平面对的频率范围在100 MHz以上[1]。

图2 电源网络结构组成图

存储器的工作方式决定了电源网络的配送方式,供给到存储块上的电源直接给内部的晶体管充放电,供给到控制器上电源通过封装主板与存储块通信。在此分别称为内核电路和I/O电路。

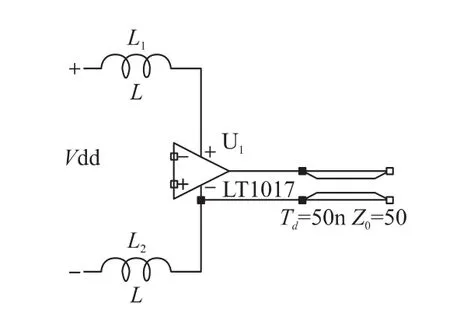

内核电路的工作方式如图3所示,L1和L2为电源网络上输入路径和返回路径的感抗,U1为开关,在开关打开的瞬间,为了保证晶体管高速改变状态,瞬时必须提供足够大的电流,而L1限制了电流的瞬间增大,使一部分电压落在电感上,降低了充电电压,延缓了充电时间,若同时有多个开关打开,则瞬时需要更大的电流为晶体管充电,电感的压降增大,充电时间进一步增长。

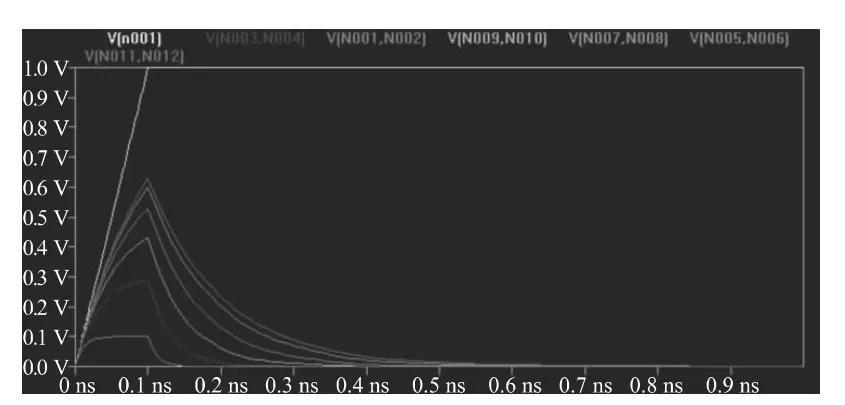

图4 为分别同时打开 1、2、4、6、8、10 个晶体管的仿真结果,可见在不同的电流噪声下,电源网络的阻抗不同程度的降低了供电电压。在放电时地线网络上的L2会有同样的效果。

图3 内核电路简化结构

图4 内核电路充电时PDN上的电压噪声

I/O电路的工作方式如图5所示,连接I/O电路传输线的特征阻抗为了端口匹配是一定的,输入传输线的电压根据电压分配定律vo=zT/zI可得,如果同时要开通多个晶体管,就需要多条传输线,传输线越多并联阻抗降低,相应分配的电压降低,这样输出电压波形退化,可能引发误操作或延缓触发事件[5]。减小电源网络上的阻抗可使传输线上分配应有的电压,避免误操作。由于并联传输线阻抗降低分配同样的电压所需的电流增大,同样电感会抑制瞬态大电流,减缓电压的上升时间。

图5 I/O电路简化结构

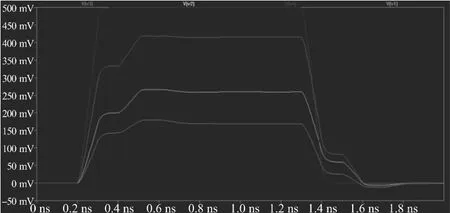

图6为同时给1、2、4、6条传输线供电时的仿真结果,随着传输线的增多,由分压定律可见电压退化非常明显,这样给多条传输线供电时显然会引发误操作。

图6 I/O电路传输线上分配的分压

图7为减小PDN(Power Distribution Network)的阻抗后的仿真结果,随着传输线数目的增多,电压退化作用减小,但是由于瞬时电流的增大,PDN上的电感效应增强,电压的上升时间延缓。

图7 I/O电路降低PDN阻抗后传输线上的电压图

由此可见,不够理想的电源网络可能延缓晶体管的充放电时间,引发误操作,过冲损坏晶体管等问题。

3 电源完整性分析

由上述电源网络的分析可知同步开关噪声、地弹噪声、过冲现象等各种问题的最终原因是电源网络入射线和地线的电感作用抑制了电流的瞬时变化。为消除电感的影响,在不同位置加去耦电容及时提供足够的电荷,防止电压降以及电压波动。而在引入去耦电容时由于电容引线上存在电感,若此电感上的压降较大,则引入的去耦电容可能毫无意义。由贴片电容的封装可知电容值的大小和引线电感值成正比关系,这样在靠近高频IC端只能接很小的去耦电容,尽管小电容的稳压作用有限,需要外部网络不断的给小电容充电,但是降低了外部网络的工作频率,这样外部电源网络上就可以接更大一点的去耦电容,如此这样随着电源网络距IC的距离的增加,所加的去耦电容值也不断加大。在高频PCB设计中电源地平面对有着不可替代的作用,临近的电源地平面的电容作用可有效的稳定电压。但是这种结构相当于无数个小电感和电容的串并联会形成谐振腔,谐振电压波会在平面内传播形成驻波,对临近的电路和信号产生干扰[6]。因此有效的消除谐振是合理应用平面电源网络结构的关键。

在电源网络设计中,添加去耦电容可以供给瞬时电流,但是在特定频率下电容和电感发生谐振,这样不仅不能提供电荷反而会增大阻抗。因此在加去耦电容时要特别注意添加位置以及电容值的大小,避免谐振。添加去耦电容以及采用平面网络最终的目的是能为用电器提供稳定的电压。检验PDN上去耦电容的添加及平面放置的合理性可以从IC端测试PDN的阻抗来判断,由ΔV=Z×dI/dt可知在瞬时电流一定的情况下电压噪声和阻抗有关,因此PDN的设计要尽量减小阻抗,降低电压噪声,通常用电器的电压噪声容限为5%。由于在电源网络的不同位置工作频率不一样,因此在不同位置根据工作频率和电压噪声容限可计算出来一个最大可允许阻抗及目标阻抗,图8所示为不同位置的工作频率以及相应频率下的目标阻抗,设计的PDN阻抗不能超过目标阻抗,可以通过测试PDN阻抗来分析,来检验去耦电容和平面对的添加的合理性,如果测试阻抗超过目标阻抗应该在适当位置添加或修改去耦电容,调节平面对,直到测试阻抗满足目标阻抗为止。

图8 PDN的目标阻抗

4 电源完整性仿真

由上述电源完整性的分析可知,设计电源网络的关键是采用平面和添加去耦电容,检验电源网络的关键是平面的谐振问题和从存储器端所看到的电源网络的阻抗问题。

4.1 谐振分析

把PCB和PKG合并导入到Siwave中,进行谐振分析,分析频率范围选100 MHz~1 GHz,选择谐振比较严重的一个仿真结果,图9所示为频率在0.8 GHz时板上Vdd与GND平面对的谐振情况,图中不同的颜色区域表示不同的谐振电压,根据左边的颜色和谐振电压对比条,可知黄色区域是谐振较严重的区域。为了避免谐振影响,IC器件应该放置在远离谐振的地方,但这是不现实的,因为在此频率下PCB板的大部分面积都有振荡,在此可减小Vdd和GND的间距来抑制振荡,或者加旁路电容。在此用旁路电容的方法,在PCB板上Vdd和GND平面对之间选择振幅较强的多处位置加去耦电容,电容值为1 nF串联电感为40 pH调节串联电阻的值为5 mΩ时,重新仿真的结果如图10所示,整个区域显示绿色,表示谐振电压接近0,谐振电压大大减小。因为振荡波峰相当于平面的等效电感和电容发生反谐振,加上电容后改变了反谐振频点,在此需要调节旁路电容的串联电阻,使阻抗和平面阻抗匹配减小反射,在实际中采用可控串联电阻的陶瓷旁路电容。

图10 0.8 GHz下添加旁路电容后的谐振电压

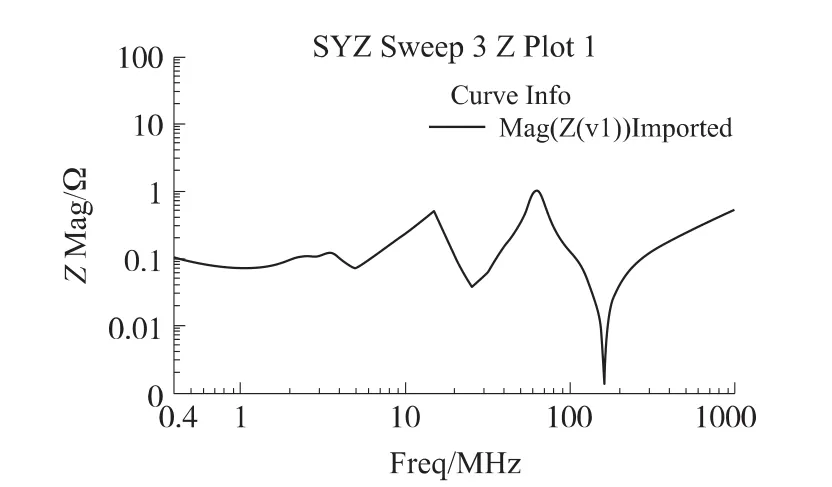

4.2 电源阻抗测试及优化

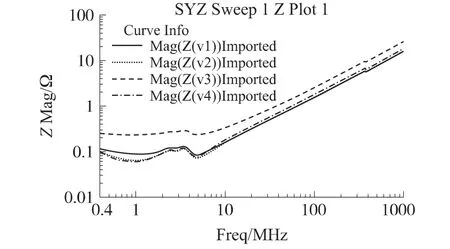

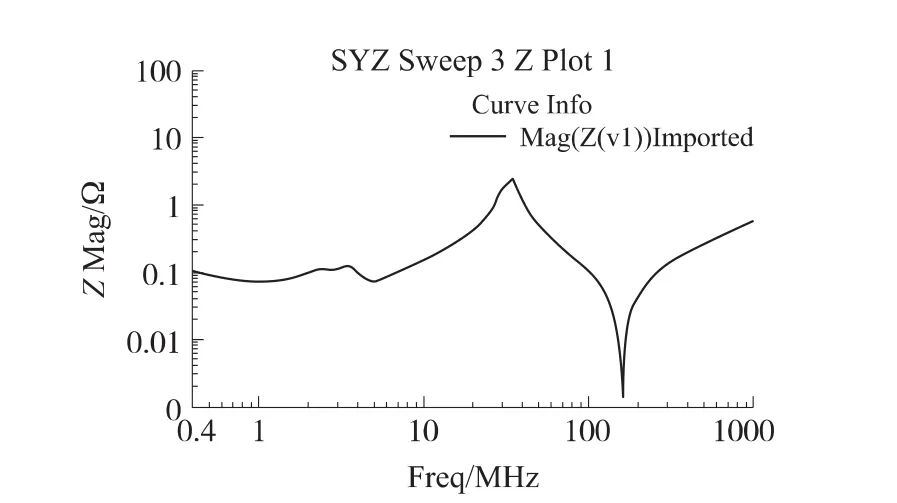

在Siwave下在控制器和存储块接口端添加port在0.1 MHz~1 GHz下进行S、Y、Z参数扫描,从而得到图11所示的阻抗结果。由图可见在频率升高到100 MHz时,实际阻抗在1.5 Ω~3 Ω之间,也超出目标阻抗,由于PKG上的电源线较细,随着频率的升高阻抗不断增大。为了降低实际阻抗,在最靠近晶体管端添加去耦电容,为高频电流提供电荷。图12为添加寄生电感为100 pH串联电阻为1 mΩ的1 nF电容后的结果,此去耦电容的谐振频率为GHz,可以看到频率在100 MHz~1 GHz内阻抗下降到1 Ω以内,但是在35 MHz处有个反谐振点,此点阻抗为2.5 Ω,超出目标阻抗,为了使阻抗线尽量低、尽量平滑,需要降低此反谐振点处的阻抗,再在PCB上距PKG最近的位置加50 nF去耦电容(寄生电感为400pH串联电阻为1 mΩ),重新仿真结果如图13所示,这样整体阻抗就低于1 Ω,满足目标阻抗的要求。

图9 0.8 GHz下平面对上的谐振电压

通过谐振分析和阻抗分析以及电源网络的优化后,电源网络阻抗减小,从而能为高速工作的存储器提供较为理想的电源。

图11 4个IC端口所测得电源网络阻抗

图12 在IC入口处PKG上加10 nF去耦电容后的阻抗

5 信号完整性分析

信号完整性是指构成信号的电压电流波在信号网络上传播时不断感受信号网络的阻抗变化,如果信号网络阻抗发生变化,信号就会在变化处发生反射,导致信号畸变退化。在高频电路中信号完整性问题主要包括延迟、反射、振荡、串扰等问题。延迟是信号在传输线上的传播延时,延迟对系统的时序有很大的影响。反射是由于阻抗不匹配而造成的信号能量不能完全吸收,线路的拐角、过孔、线宽突变、端接不匹配等都可能引起反射,是信号畸变的最主要原因。振荡是由于传输线上过度的电感和电容谐振引起的。串扰是传输线上的信号受到其他传输线上信号的干扰而发生畸变[7]。加大传输线间距,减小平行传输线的平行长度可有效抑制串扰。实际信号的完整性问题是多方面问题综合的结果。

图13 在PCB上最靠近PKG处加50 nF去耦电容后的阻抗

在存储器高速工作过程中,控制器和存储块之间的数据总线、命令线、地址线在传输信号时可能发生各种完整性问题,将导致存储器命令误操作、读写数据的不正确以及存取地址的错误等问题,严重影响存储器的正常工作。因此在电路设计时信号线宽要合适减小反射,线长要一致避免个别信号的时延,采用蛇形走线减小信号线的平行长度。最后为了保证信号线的设计合理,必须通过完整性仿真,进行验证。

在对信号线进行仿真时,选择合理的分析模型准确反映信号完整性问题是非常重要的。在此采用S参数和IBIS模型进行仿真,S参数用于描述不同频率下信号在某一端口入射波进过网络传输后到另一端口的反射波的电压关系[8],包含了时延、串扰等各种问题,是综合所得的结果,因此能够准确的反应信号网络的全部信息。对于信号输入端口和输出端口,由于IBIS模型是从实际的器件中提取得到的,能够较准确的反应管脚信息,且可以免费从生产商得到,所以端口采用厂商提供的IBIS模型[9]。有了这两个模型就可以在ADS下搭建平台进行仿真优化,解决信号完整性问题。

6 信号完整性仿真

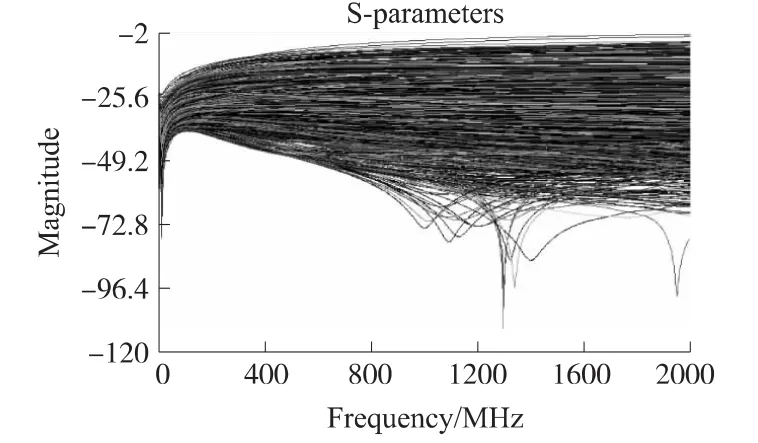

6.1 S参数提取

在Siwave下,在连接控制器和存储块的数据线、地址线、命令线两端加测试点port,然后在0~2 GHz的频率范围内进行S参数扫描。扫描结果如图14所示,为控制器和存储器间24根信号线的S参数。

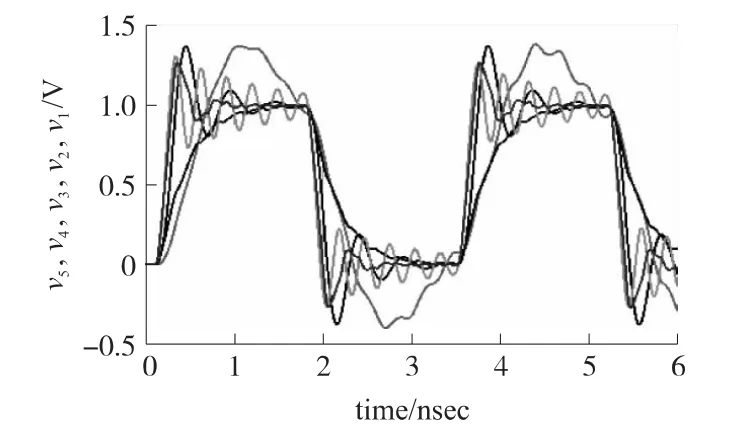

6.2 ADS下仿真

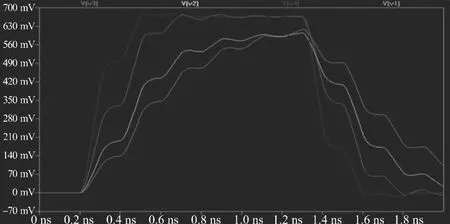

在ADS下搭建平台,把Siwave下得到的S参数导入到信号网络中,并把从生产厂商得到的控制器和存储块的IBIS接口模型导入到ADS中的端口模型中,在控制端为仿真电路提供周期为3.4 ns,上升沿和下降沿为200 ps的信号激励源。在存储块的IBIS接口端测试电压,由于24根传输线的仿真结果放在一起较为混乱,现选取5条有代表性的传输线在存储块接口端的电压仿真结果如图15所示,由图可见信号v1的过冲电压较大,v2有较长的时延且峰值较大,v3有明显的反射现象,v4有较长时间的振铃效应,v5也不够理想。

图14 24根信号线的S参数仿真结果

图15 5根信号线输出端口的电压波形

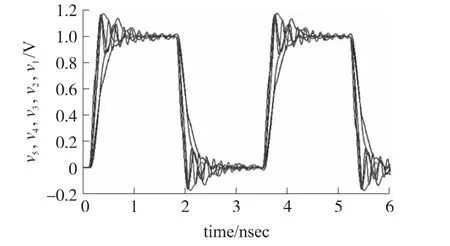

6.3 信号网络优化

从上述的仿真结果可见,信号网络并不理想,存储器在这样的信号下不可能正常工作。在此需要对PCB和PKG上的信号线进行修改,在修改过程中既要遵守信号优化的基本规则,又要根据不同信号线的具体问题进行具体处理。在此对v1和v3信号线应特别注意信号线阻抗的突变和过孔处理,v2信号线应注意线长和其他信号线长的差别以及线上是否有比较明显的寄生电容,v4信号线注意线上是否寄生了过多的电感和电容,v5可能受其他信号的干扰较大。经过优化后的PCB和PKG板,再次提取S参数,并在ADS下仿真,结果如图16所示,可见信号质量有明显的改进,如果改进后的信号网络还不能满足要求,则需要进一步优化。

通过S参数和IBIS模型在ADS下的仿真能够检查信号网络的完整性问题,并通过优化可改善信号质量,减少存储器的错误操作。

图16 优化后5根信号线输出端口的电压波形

7 结论

由于电路设计的高密度、高速度要求,电源完整性和信号完整性问题越来越受到重视。由于低成本的要求、生产周期的限制以及越来越激烈的市场竞争,通过测试PCB板的完整性问题,再进行改进将越来越没有竞争力。通过Siwave和ADS仿真能很好的优化电源和信号网络的完整性问题,避免了由于高频效应引发的问题,并且极大的缩短了产品的开发周期,提高了设计的成功率,节约了成本。因此基于Siwave和ADS集合进行的前仿真是十分有意义的。

[1]闫静纯,李涛,苏浩航.高速高密度PCB电源完整性分析[J].电子器件,2012,35(3):296-299.

[2]陆飞,吴建军,田晓明.移动终端DDR SDRAM数据总线布线仿真与设计[J].电子器件,2009,32(1):76-79.

[3]桑野雅彦(日).存储器IC的应用技巧[M].王庆,译.科学出版社,2006:113-128.

[4]斯瓦米纳坦(美),恩金(美).芯片及系统的电源完整性建模与设计[M].斯瓦米纳坦,译.科学出版社,2012:58-74.

[5]许云飞,吴明赞,李竹.基于HyperLynx的断路器状态监测无线节点 PCB 设计[J].电子器件,2011,34(5):529-532.

[6]董辉,朱义胜,赵柏山.基于滤波器应用的PCB平面电感的电磁辐射研究[J].电子器件,2007,30(1):183-186.

[7]李广辉,庄奕琪,曾志斌.基于信号完整性分析的一种视频处理系统设计[J].电子器件,2007,30(4):1325-1328.

[8]Eric Bogatin.Signal Integrity:Simplified[M].电子工业出版社,2005:136-145.

[9]李成,程晓宇,毕笃彦.基于HyperLynx的高速DSP系统信号完整性仿真研究[J].电子器件,2009,32(2):445-451.