基于SOI工艺的高可靠有源像素研究*

田 犁,苗田乐,危 峻*,汪 辉

(1.中国科学院上海技术物理研究所,上海200010;2.中国科学院上海高等研究院,上海201210)

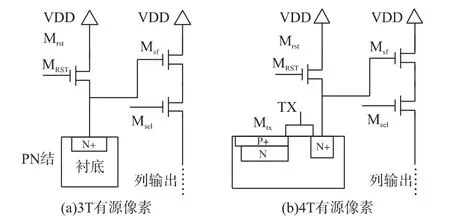

CMOS图像传感器能够兼容标准的CMOS制造工艺,已逐渐成为图像传感器领域的主流产品[1]。随着在航天等特殊领域应用的增多,CMOS图像传感器的抗辐照性能日益重要[2]。在CMOS图像传感器中,最常用的是3T和4T型有源像素结构,其具体实现电路如图1所示。

图1 3T型结构和4T型结构

1 SOI工艺高可靠有源像素设计

1.1 SOI高可靠性工艺介绍

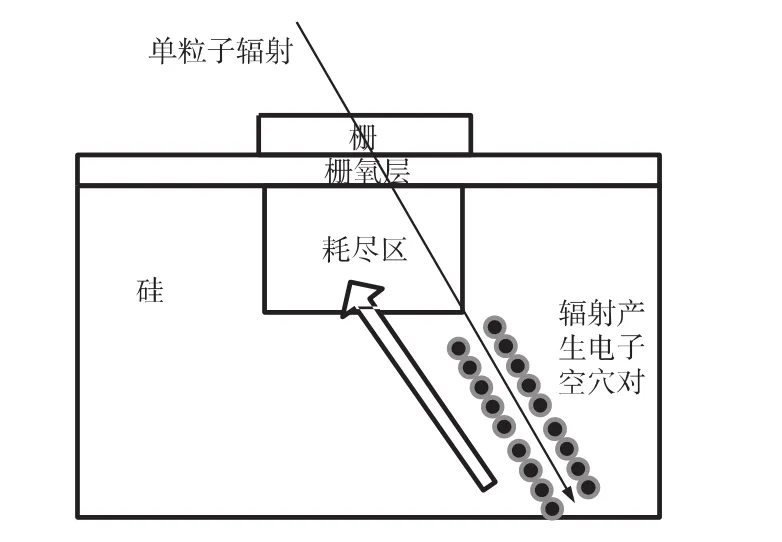

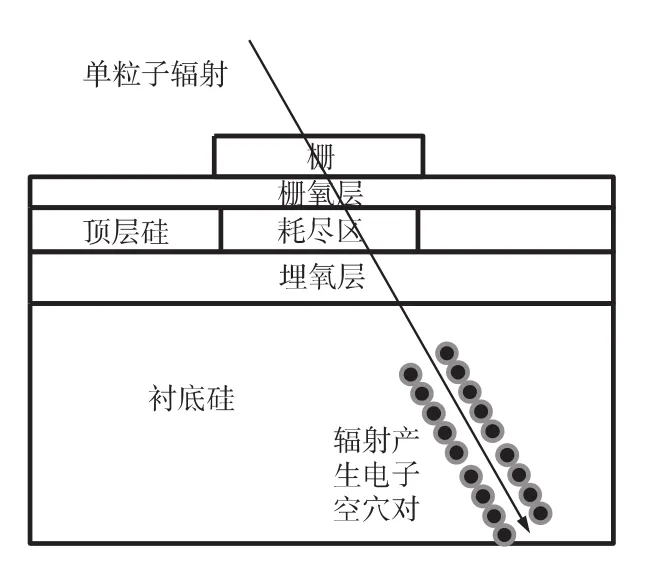

SOI(Silicon-On-Insulator,绝缘衬底上的硅)技术是在顶层硅和衬底硅之间引入一层埋氧层(BOX)的半导体工艺。SOI材料以衬底硅作为机械支撑,其厚度约为几百微米,而顶层硅则用于制造半导体器件。由于埋氧层的存在,实现了集成电路中器件和衬底之间的介质隔离,使得SOI技术与体硅技术相比具有了许多独特优点,比如避免了体硅的闩锁效应、具备良好的抗单粒子入射和抗瞬时辐照特性[4](如图2和图3所示)等,成为解决CMOS图像传感器高可靠性应用的理想工艺技术[3]。

如图2、图3所示,由于埋氧层的阻挡,与体硅器件相比,SOI器件显著降低了耗尽区对单粒子入射电离电荷的收集能力。因此,SOI工艺中顶层硅上形成的MOS电路具有较强的抗单粒子和瞬态辐照特性。

图2 传统体硅器件

图3 SOI器件

CMOS图像传感器像素点对于光波的吸收与材料特性有关。半导体材料通常能强烈地吸收光能,当光强为I的光入射进入半导体材料中时,光强的变化和吸收系数的关系为:

式(1)中α为吸收系数依赖于光的波长α=1/λ,与光的波长和材料有关系,x为深度,设定边界条件为I(x)x=0=I0,可以得到式(2):

由式(2)可知,CMOS图像传感器中作为感光器件的感光二极管要有足够的纵向深度才能充分吸收可见光,而对于全耗尽型SOI工艺来说,由于顶层硅很薄(一般不超过200 nm)[6],直接用于制造CMOS图像传感器将导致传感器像素点对于可见光的吸收极为有限,从而影响成像性能。将图像传感器4T结构的感光二极管和转移晶体管TX制备于SOI衬底硅层的像素设计方法[7],目的在于克服因SOI顶层硅很薄而无法形成良好感光的难题,但该方法存在一些局限性:首先,从平面制程工艺的角度,刻蚀去除SOI顶层硅及埋氧层、并在暴露的衬底硅中制备像素感光器件的工艺步骤所形成的像素感光区域与读出电路区域之间具有一厚度差,对于光刻加工过程中的曝光对准有不利影响,使得在制备4T型像素结构中的转移晶体管TX时容易产生较大的制造误差,导致图像传感器均匀性下降,从而引入更多的固定模式噪声(FPN)[8];其次,在衬底硅中制备的感光二极管缺乏埋氧层的保护,在器件工作过程中容易吸收衬底硅中因辐射产生的电子空穴对,造成更高的暗电流,大大降低像素感光器件性能[9];最后,受辐照像素在吸收因辐射产生的沉积电荷后,会与相邻未受辐射像素形成电荷分享,从而进一步恶化CMOS图像传感器的成像质量。

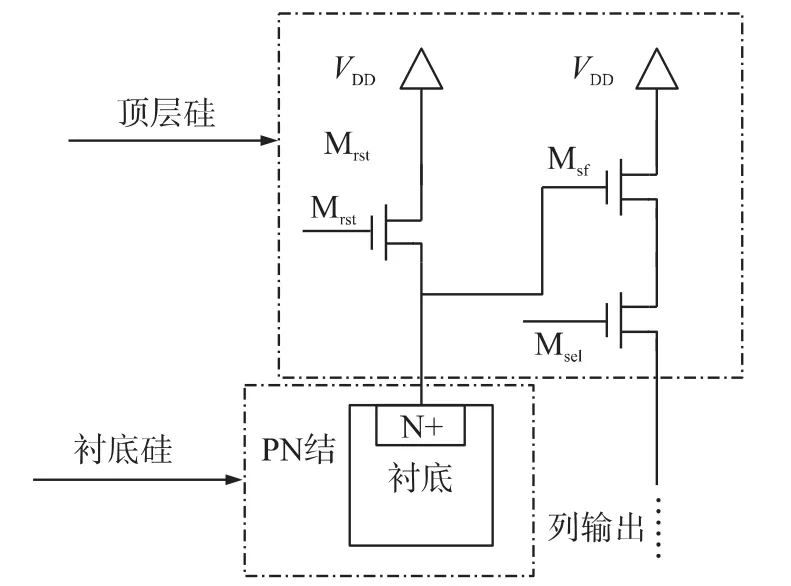

有鉴于此,这里采用不含转移晶体管TX的3T型有源像素单元,并尝试在像素单元周围引入P+重掺杂保护层的方法来抑制像素之间的电荷分享效应,并进行了二维器件的建模与仿真工作。

1.2 像素设计及相关工艺参数选择

如图4所示,像素设计采用3T型有源像素单元结构。3T型有源像素单元由感光二极管、复位晶体管Mrst、行选择晶体管Msel和源极跟随器Msf构成。其中,感光二极管形成在衬底硅上(Handle Wafer),而复位晶体管Mrst、行选择晶体管Msel和源极跟随器Msf则形成在顶层硅(Top Silicon)上。

图4 SOI工艺下3T型有源像素单元

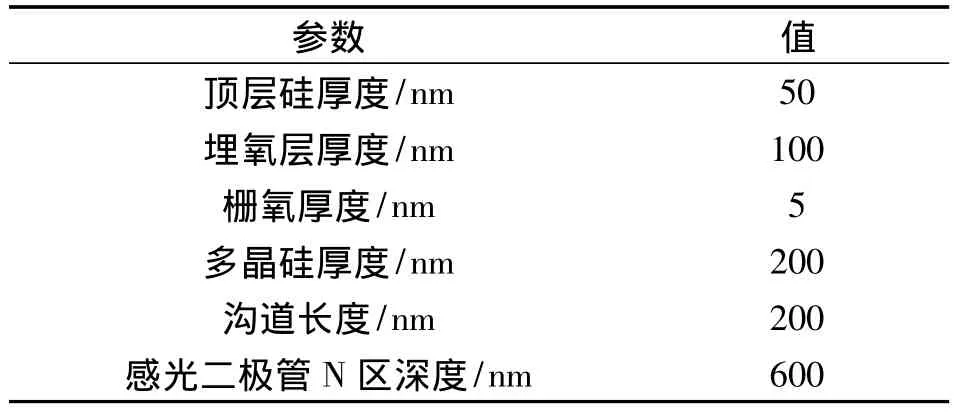

利用仿真工具对3T型有源像素单元中的感光二极管和复位晶体管Mrst进行重点研究,建模工艺参数基于日本OKI的0.2 μm FDSOI CMOS工艺,相关工艺信息[10]如表1所示。

表1 仿真工艺参数

1.3 器件结构

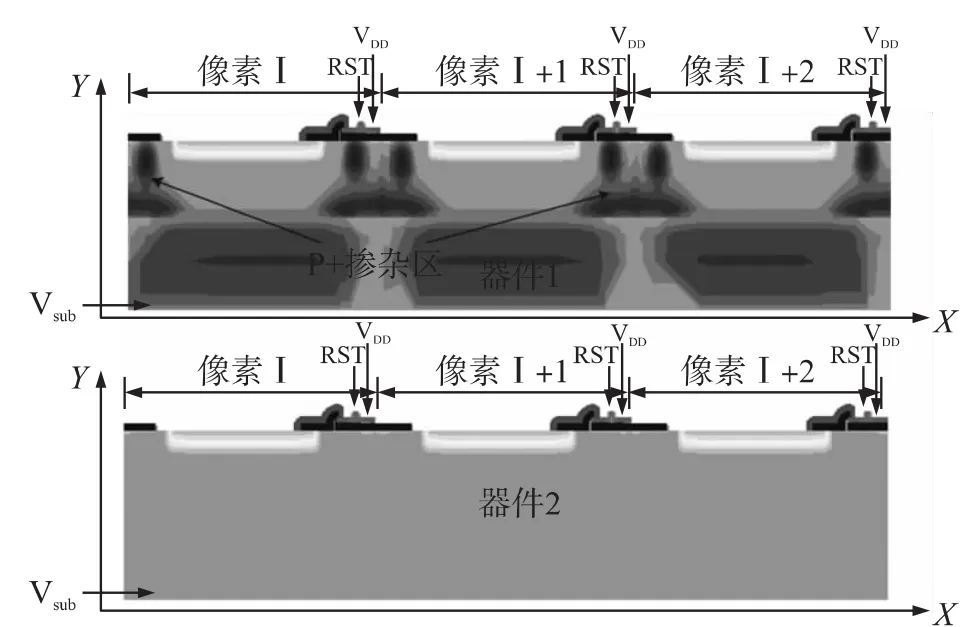

如图5所示,仿真器件定义为:器件1,工作电压3.3 V,其左侧像素定义为像素I,相邻右侧的两个像素依次定义为像素I+1和像素I+2,像素I、I+1、I+2四周及下方均环绕有P+重掺杂保护层;器件2,对比器件,工作电压及像素定义均与器件1相同,但其像素结构周围无P+掺杂区。

图5 仿真器件1和器件2定义

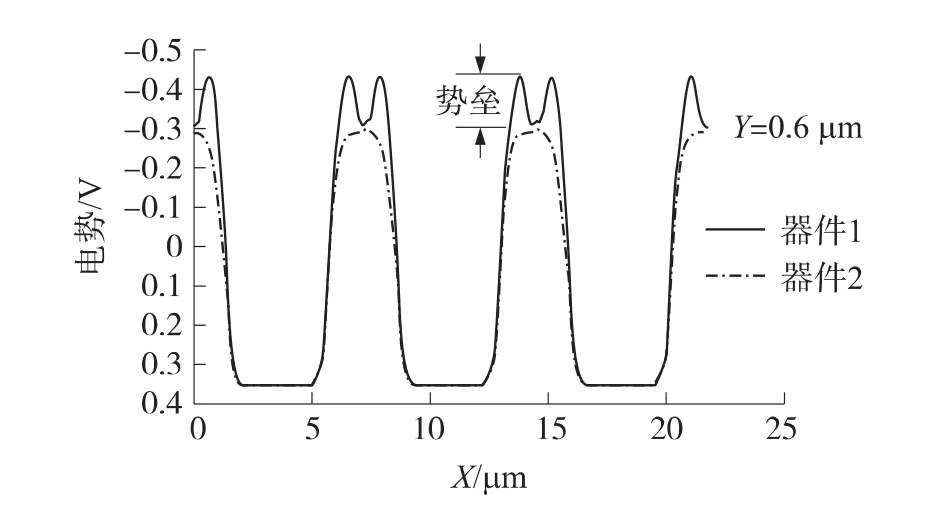

仿真器件中定义的3个电极分别对应图4中的RST、VDD和衬底电压Vsub。生成器件后,沿着Y=0.6 μm的方向做切线查看电势变化的情况,如图6所示,根据器件1和器件2电势分布对比可知,由于引入了P+重掺杂区,器件1中像素之间的势垒比器件2更高,势垒宽度为2 μm。

图6 器件1和器件2电势分布(Y=0.6 μm)

1.4 辐照模型

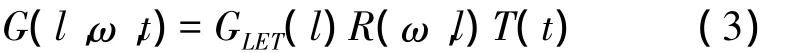

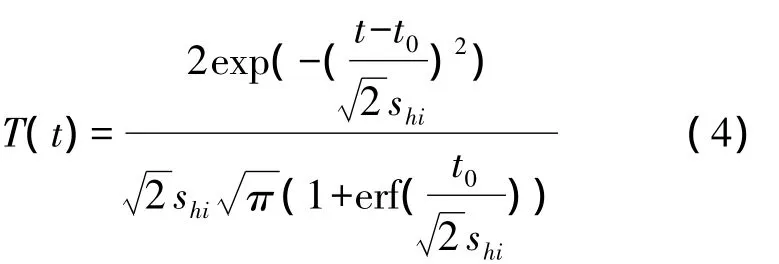

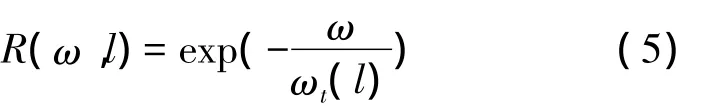

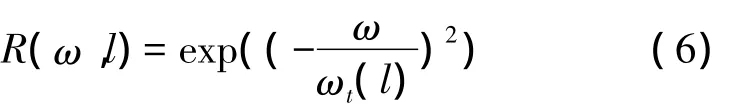

在Sentaurus Device中使用的Heavy Ion模型如图7所示,定义粒子在其轨迹附近的电子空穴对产生率为:

其中:l为粒子轨迹的长度,t为时间,ω为垂直粒子轨迹的方向距离,R(ω,l)和T(t)分别表示粒子电子空穴对产生率随空间和时间的变化,GLET(l)是线性能量传输产生率,单位为pair/cm3。该表达式中,T(t)定义为:

图7 重粒子入射模型

其中:t0为粒子射入时刻,shi为高斯特征值,产生率的空间分布R(ω,l)能够定义为指数函数的形式

或者高斯分布函数的形式[11]

其中,ω为沿着粒子轨迹径向的长度;ωt(t)为分布的特征长度,在Sentaurus Device中以ωt_hi表示。下文中计算电离产生的电子空穴对产生率所用的计算方法为高斯分布。

设定入射粒子从像素I感光二极管的中心位置(X=3.5 μm,Y=0 μm)入射到像素内部。为更好地测算感光二极管对辐射产生电荷的收集过程,本文模拟过程中没有对像素加入光照条件,因此,像素I+1和像素I+2在仿真过程中收集到的电荷均为辐射产生的扩散电荷。设定辐射的入射时间为700 ns,所使用的入射粒子的参数如表2所示。

表2中,LET为粒子的线性能量转移值(Linear Energy Transfer),表示入射粒子在单位长度内损失的能量值。在仿真中,LET的单位为pC/μm,常见单粒子入射单位为MeV·cm2/mg。硅材料中,本仿真过程采用的LET单位与常用单粒子入射单位的换算关系为 1pC/μm=97MeV·cm2/mg。

2 仿真结果

2.1 辐射前后像素区域电势变化

高能粒子进入像素内部后,与晶格原子碰撞,粒子能量值逐渐降低。粒子损失能量的一部分使晶格原子发生电离,沿着粒子运动轨迹产生电子空穴对。这些电子空穴对会对处于正常工作状态下的像素产生干扰。粒子射入像素的瞬间,在有限的空间范围内产生大量电子空穴对,这些电子空穴对发生漂移或者扩散,使像素的电势和载流子浓度分布发生剧烈变化。在像素空间电荷区内,以 LET=0.002 pC/μm,轨迹长度l=2μm和垂直入射的试验为例,高能粒子入射后,原PN结感光二极管的空间电荷区在受到粒子扰动后会向衬底中延伸数微米,呈现漏斗形状。漏斗效应表现为载流子收集的增强,使在PN结内建电场外部产生的电子空穴对,也能在延伸电场的最下方被收集。

图8是辐照后1 ps内器件沿着X轴方向上电势变化图,可以看到在像素I区域电势发生了明显的变化,这主要是因为辐照在此区域内生成了大量的电子空穴对,此后因辐射产生的电荷将会自由扩散至像素I+1和像素I+2区域并这些电荷作为噪声电子被相应的像素吸收,从而影响周边像素区域的成像效果。

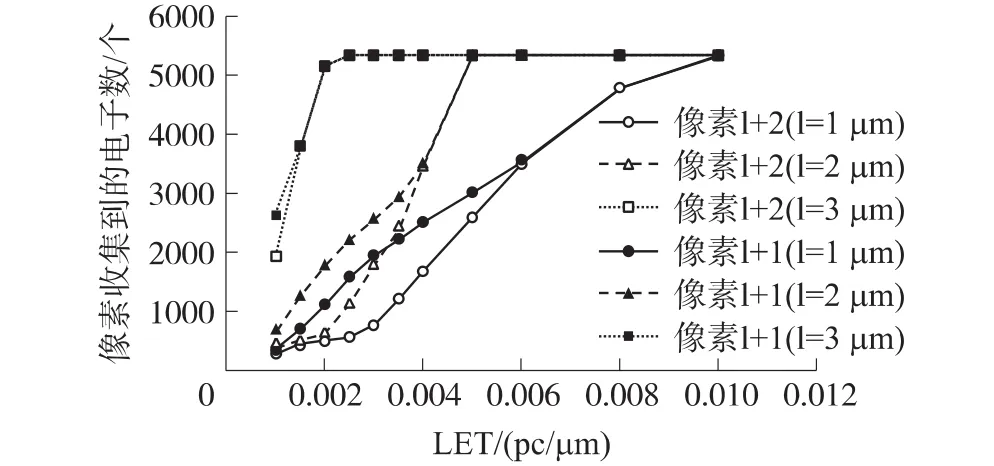

2.2 像素电荷分享效应

器件1在不同辐射条件下像素I+1和像素I+2收集到的电子数情况如图9所示。不同的辐射条件下像素I+1和像素I+2收集到的电子数具有一定差异性,当辐射剂量和单粒子入射深度超过一定范围后,像素I+1和像素I+2收集到的电子会达到饱和。在辐射剂量较小、入射深度较浅的条件下,像素I+2收集到的电子数相对于像素I+1要少,主要原因是像素I+1更加靠近辐射区域,而在电荷扩散过程中有一部分已被像素I+1吸收。

图9 器件1不同辐射条件下像素收集到的电子数

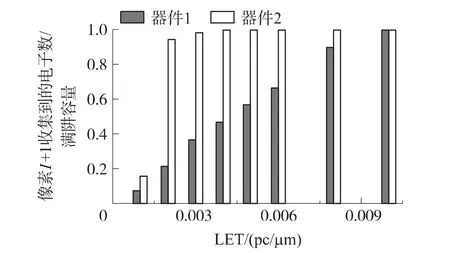

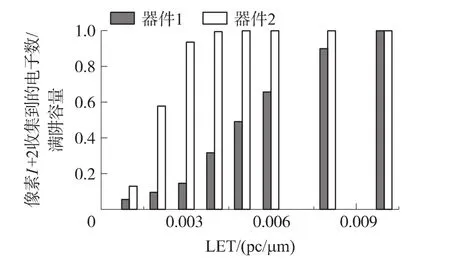

已有文献将像素区域收集到的电子数作为对比器件抗辐照的性能指标[12],但是在本文的仿真环境下,器件1在像素周围加入P+重掺杂保护区域之后,其耗尽区相比于器件2会发生变化,相对应的PN结结深、感光二极管阱容量、吸收扩散产生的电荷能力都会发生变化。因此,采用像素收集到的电子数与满阱容量的比值来对比器件1和器件2的抗辐照性能。

图10和图11分别为轨迹长度为1 μm时像素I+1和像素I+2在不同入射能量下收集到的电子的情况。在入射能量较低的条件下,P+重掺杂区域能够有效地抑制因辐射产生的电子空穴对扩散,由于势垒作用,一部分电子无法通过像素之间的势垒,像素间的电荷分享被抑制,像素I+1和像素I+2收集到的电子会减少。但随着辐射强度的增大,这种抑制作用会逐渐减小,这主要是由于随着辐射强度增大,受辐射区域的电子浓度增大,受辐射区域的电势随之发生变化,P+重掺杂区域形成的势垒对电荷扩散抑制作用已不明显。

图10 像素I+1收集电子情况

图11 像素I+2收集电子情况

3 结论

(1)入射单粒子所产生的电荷既能使入射点所在像素饱和,又能经扩散影响周边像素的正常工作。

(2)通过引入像素单元P+重掺杂保护层,在一定的单粒子辐射强度和辐射入射深度条件下,像素之间的电荷分享效应被有效抑制。

[1]Bigas M,Cabruj E,Forest J,et al.Review of CMOS Image Sensors[J].Microelectronics Journal,2006,37(3):433-451.

[2]范铁道,田雁,曹剑中,等.基于FPGA的CMOS图像感器IA_G3 驱动电路的研究[J].电子器件,2009,32(2):273-276.

[3]Hill T A,Gurrieri T M,Schwank J R,et al.An Embeddable SOI Radiation Sensor[J].Nuclear Science,2009,56(6):3372-3380.

[4]陈昕.SOI技术的发展思路[J].电子器件,2010,33(2):193-196.

[5]Arai Y,Miyoshi T,Unno Y,et al.Development of SOI Pixel Process Technology[J].Nuclear Instruments and Methods in Physics Research A,2011,636(6):31-33.

[6]周彦平,王晓明,常国龙,等.CMOS图像传感器的辐射实验[J].红外与激光工程,2011,40(7):1270-1273.

[7]倪景华,黄其煜.CMOS图像传感器及其发展趋势[J].光机电信息,2008,25(5):33-37.

[8]Morikawa K,kajita Y,Mitarashi M.Low-Power LSI Technology of 0.15 μm FD-SOI[J].OKI Technical Review,2003,196(4):60-63.

[9]Kucewicz W,Bulgheroni,CacciaA,etal.Fully Depleted Monolithic Active Pixel Sensor in SOI Technology[J].Nuclear Science Symposium Conference Record[C]//2004 IEEE:1227-1230.

[10]Syukyo Gando Ryu.First Performance Evaluation of an X-Ray SOI Pixel Sensor for Imaging Spectroscopy and Intra-Pixel Trigger[J].Nuclear Science,2011,58(5):2528-2536.

[11]Sentaurus D-2010.03,Sentaurus Workbench User Guide[S].Synopsys.Inc,USA,2010.

[12]姚素英,李渊清,徐超,等.四管有源像素单粒子效应及辐射加固器件模拟研究[DB/OL].http://www.paper.edu.cn.2012-11-6.