基于ANSYS的板级电路热分析及布局优化设计

马 静

(淮南联合大学机电系,安徽淮南232001)

由于电子器件朝着体积微小化、高互联密度方向发展,使得对实际的微电子器件进行热—机械性能测试变得越来越困难甚至不可能;传统的设计—实验—修改方案—再实验的方式生产周期长,过程反复多,已经远远不能适应电子器件更新换代速度,并且在相当程度上导致了产品制造成本的上升。因此,在设计阶段采用计算机技术模拟和分析制造后产品的实际性能,以发现其中的不足,并将之应用于设计的修改,已成为工程上主要的发展趋势[1-3]。

1 板级电路三维有限元模型

1.1 模型简化假设

实际的板级电路(SMA)是一个包括表面贴装元器件(SMC/SMD),印刷电路版(PCB)在内的板极电路。要对SMA进行正常工作情况下的热分析,必须先对实际的SMA进行合理的替代,使其成为计算机仿真模型。把具有特定物理、几何特征的SMA进行合理的简化是获得最终正确仿真结果的关键[4-5]。它包括两个部分的内容:(1)对SMC/SMD的合理简化;(2)对PCB的合理简化。先考虑对SMC/SMD的简化替代。对于小外形的片式电容器、电阻器,由于其体积小,热容量小,在再流焊过程中的吸热小,其温度变化大致与PCB一致且对整个SMA的温度分布影响不大,在进行计算时可将其作为质量点加入到PCB基板上。对于外形较大的器件,比如PLCC,BGA,SOP等,由于其封装结构和材料各异,必须对其进行简化。对于规则外形的器件,在计算时忽略其引脚而代之以规则的几何外形——长方体,圆柱体。由于器件与PCB基板之间以引脚相连,再流焊接过程中两者通过引脚进行热传导。必须估计器件和PCB之间的绝对热传导系数,用下式来表示热传导系数大小[6]:

式中,G为热传导率的数值大小;N为引脚数目;kp为引脚的热传导率;Ap为引脚的横截面积;lp为引脚的长度;ka为空气的热传导率;A为空气的器件下表面的面积;t为器件与PCB之间的空气间隙厚度。

对于PCB,主要考虑其层数以及PCB上金属布线对于PCB材料参数的影响。对于单一的PCB材料FR4或者FR2,其材料参数是各向同性的,但对于有金属布线以及多层PCB,其材料参数将呈现各向异性。对于各向异性材料的PCB,将采用平均材料参数的方法对其进行简化。

1.2 板级电路实体模型[7]

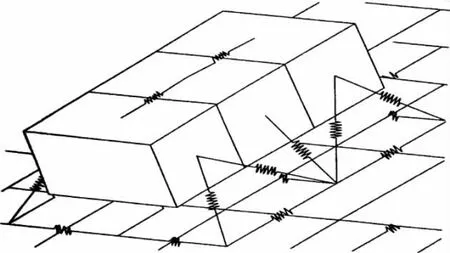

典型的板级电路由基板、大量的片式元件组成,基板包括单层、多层板等。以3D模型来表示一定厚度的PCB基板,对于基板上裸露的电路可以通过附加的辐射面来模拟。对于大量的片式电阻、电容以及小外型的晶体管可以用一维质量点单元来精确地表示,相对3D模型在不降低精确度的情况下可以节省大量的计算时间。对于更大更复杂的元件,不能用2D模型来简化,必须更详细地来讨论,一种有效的方法是用立方体模型图1来表示。

图1 元器件的立方体模型

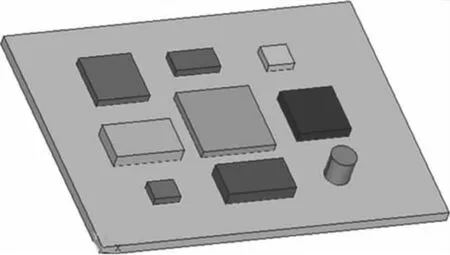

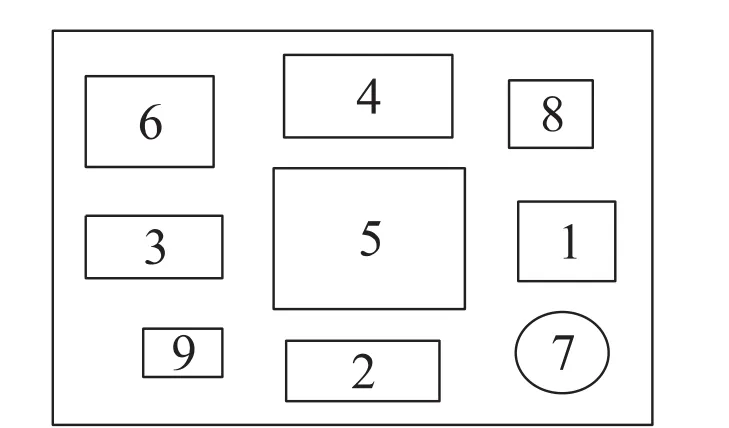

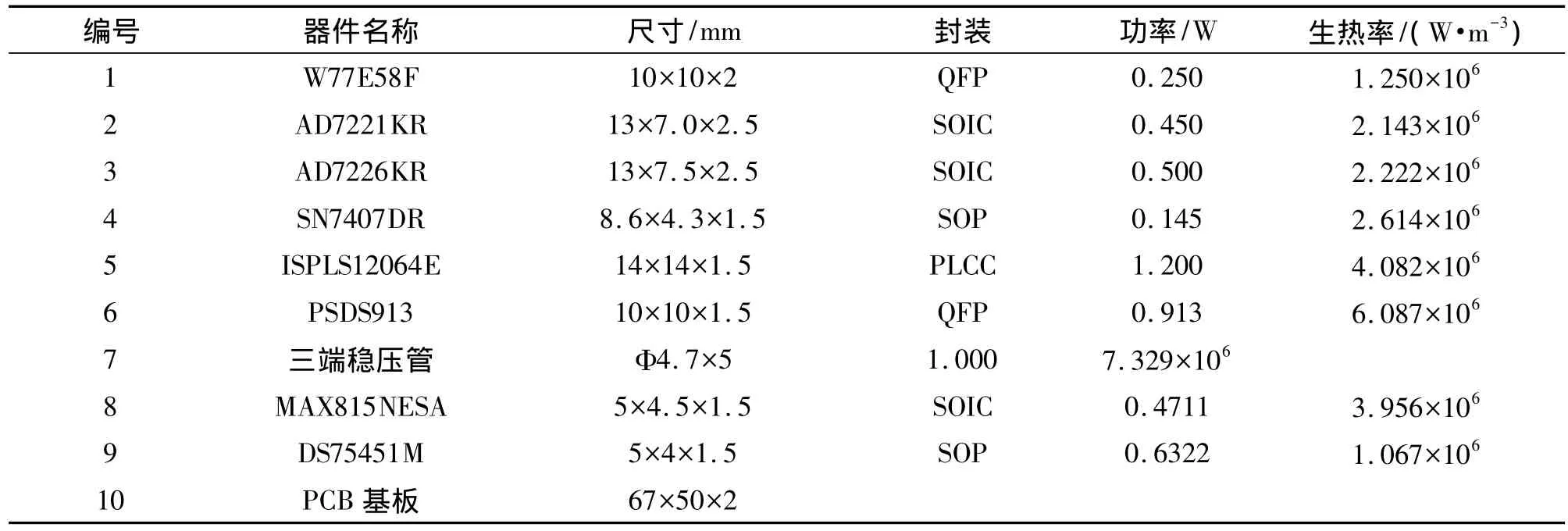

为了很好模拟实际的板级电路产品,设计如下的板级电路,包含基板、2个QFP,1个PLCC、2个SOP、3个SOIC元件,还有1个三端稳压管,基板以及各IC的材料参数各不相同,考虑用直接生成SMA有限元模型费时费力,采用实体造型的方法减轻这部分工作量。ANSYS程序允许通过汇集线、面、体等几何体素的方法构造模型,方便用户建立复杂的几何模型。利用ANSYS的实体建模功能建立如图2所示的简单的SMA实体模型,其器件编号及布置如图3所示。表1为该板级电路模型的各个组成部件名称、尺寸大小以及封装类型、功率以及生热率。

图2 基于ANSYS的板级电路实体模型

图3 板级电路器件编号及布置示意图

表1 板级电路各组成部件名称、尺寸、封装形式、功率及生热率

从图2中可以看出,把实际的SMA转换为ANSYS计算模型时,通过实体建模技术把原来复杂结构的SMA各组成部分都做了简化处理,这样的简化处理对于温度场分布计算是可以接受的。从直观上看,气流能够到达的部分是元件以及PCB基板的裸露部分,为了能够在元件以及PCB基板的裸露部分加对流载荷,而其他部分则没有,对所有体素进行一次交叠操作,以产生用于加载热对流载荷的几何多边形。为了方便求解过程可作如下假设:

(1)所有印制电路板和器件均视为与其实际几何形态相对应的理想几何体而不计二者间的几何误差,且忽略各几何体上小的倒角、圆角及孔洞等细微结构;

(2)仅考虑印制电路板和器件与周围空气环境的相互作用,暂时忽略电气互连线路等对热场造成的影响;

(3)假定板上所有器件各向同性均匀导热,且取相同的平均密度值。

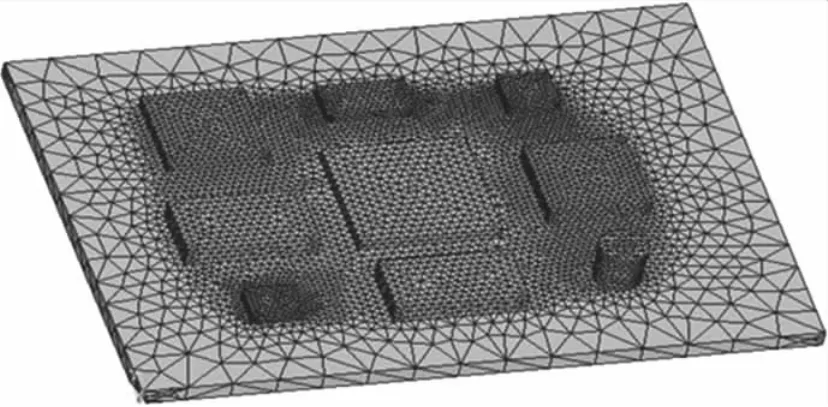

采用ANSYS软件对上述板级电路进行网格划分,结果如图4所示。

图4 板级电路网格划分

2 板级电路有限元热分析及元器件布局优化[8]

ANSYS热分析的边界条件或初始条件可分为7种:温度、热流率、对流、辐射、绝热、生热。在这里只考虑其中的对流、传导、和生热3种边界条件。

在对板极电路模块进行热分析时,假设三端稳压器的转换效率为95%,则其发热功耗为1 W。施加的环境温度为20℃。同时,仅考虑PCB基板上下底面与周围空气形成的对流。图5所示为分析以后的温度分布。

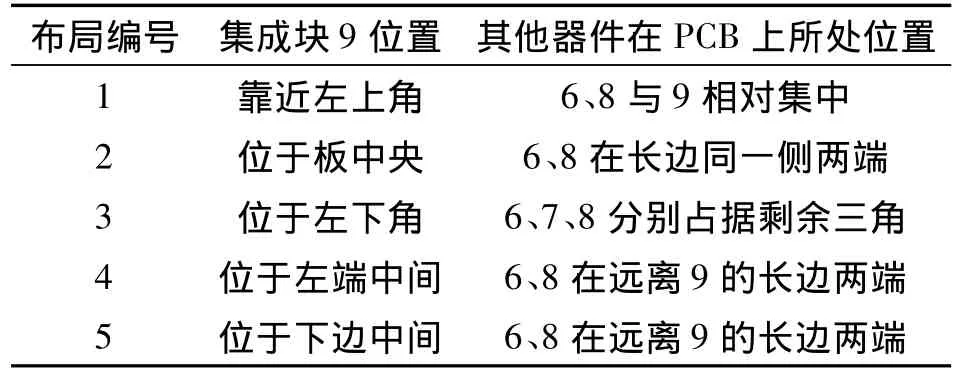

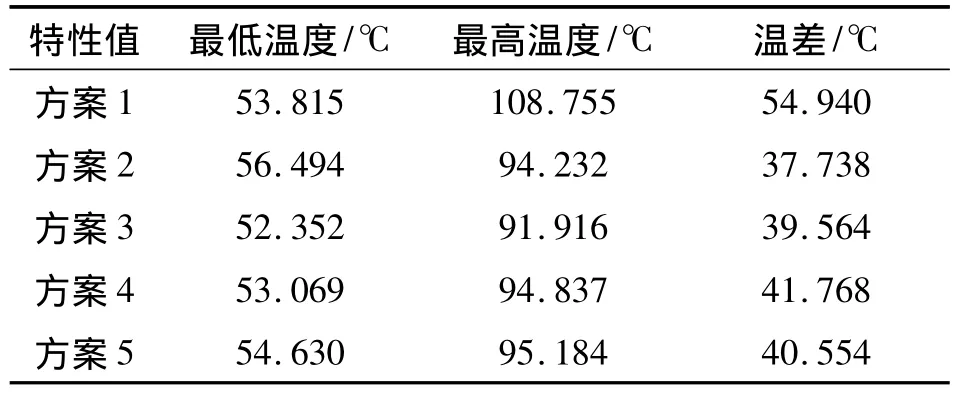

元器件的布局不仅要满足制造时的工艺要求,还应能尽可能地满足电、热性能等方面的要求。表2列出了图3所示板级电路的5种布局方案,分析在不同布局方案下板级电路的温度分布,以便得出较合理的板级电路集成块布局方案。

图5

表2 布局方案情况

图5为各种布局情况下有限元热分析的结果。各方案中最高温度始终出现在集成块9上随着集成块9在电路板上分布位置的不同,电路板的最高温度也不同,但在各种布局中温度最高处均位于集成块9上,其原因显然在于集成块9单位体积生热率最大。换言之,集成块9在板上的位置对该板极电路模块的热场形态及最高温度产生了决定性的影响。

表3为各种布局下集成块9的特性参量。

表3 各种布局情况下温度极值

结合图5所示的温度分布图可知:按照布局方案3对集成块进行布局可以使该板极电路温度较其他4种布局方案低,因此,在实际设计板极电路上的集成块布局时,可采用布局方案3。

3 考虑散热措施的板级电路热分析

在PCB上的集成块布局均采用较合理的方案(即布局方案3)的情况下,若同时考虑采取散热措施,可以较明显的降低模块的最高温度。图6为增大了与外界环境的热交换系数(强迫对流)后板极电路的温度分布图。从图6可见,在考虑了散热措施后,其最高温度由原来的91.916℃降低到31.913℃。

图6 强迫对流时方案3的温度分布图

4 分析总结

以上分析得出了生热率大的元器件在印制电路板上以各种典型方式排列时的温度分布形态。由此可知,从结构散热的角度考虑,当大小、功耗以及元器件数目都已确定时,应合理地布置元器件在印制板上的位置,建议在热设计时作如下安排:

(1)采用将高生热率器件在板面上呈四角型布放的方案。其中,三端稳压器和另外三个生热率较高的器件6、8、9分占PCB四角,其余器件则适当地穿插于它们之间。此时热场较均匀地分布于PCB上各处,且高低温差37.738℃为各种方案中最小。也就是说这样可以有效地减小各区域温度峰值之间的温度梯度,使温度分布趋于平缓,以降低热应力生成,从而提高组件和板子的热可靠性。一般而言,在同一块印制板上的电子元器件,可按其生热率大小分区放置,并尽量把生热率较大的器件放在靠近印制板的周边处,充分发挥对流效应,且最好把散热较差的一面放在气流的上游,而生热率小的器件可适当地放置在生热率大的器件之间或是气流的下游。

(2)器件6、8、9集中布置,使局部温度达到了108.755℃,为各方案中最高值,对器件的性能和使用寿命构成了严重的威胁。应避免生热率较大的元器件分布过于集中,这样可以避免因器件热生成局部集中导致温度向量的叠加从而使温度场中最高温度值上升造成的不良影响。

(3)生热率大的元器件位置也不可过于迫近PCB周边,以免此处产生应力集中。

[1]Swager A W.Thermal Images Provide Reliability Clues[M].END,1990:47-58.

[2]Vaccaro J M,Holzhauer D J,Yaworsky P S.Personal Computer Thermal Analyzer,1990.

[3]Godfrey W M,Tagavi K A,Cremers C J,et al.Interactive Thermal Modeling of Electronic Circuit Boards[J].IEEE Trans Components,Hybrids,and Manufact Technol,1993,16(8):978-985.

[4]李琴,朱敏波,刘海东,等.电子设备热分析技术及软件应用[J].计算机辅助工程,2005(2):50-52

[5]陈洁茹,朱敏波,齐颖.Icepak在电子设备热设计中的应用[J].电子机械工程,2005(1):14-16

[6]刘红,赵芹,蒋兰芳,等.集成式大功率LED路灯散热器的结构设计[J].电子器件,2010(8):481-484

[7]张栋,付桂翠.电子封装的简化热模型研究[J].电子器件,2006,29:672-679

[8]华庆,殷景华,焦国芹,等.基于ANSYS的功率VDMOS器件的热分析及优化设计[J].电子器件,2009,32(4):354-356