可变频三相交流波形发生器的研制*

罗洪平 ,程安宇,赵 双,徐 洋

(1.重庆邮电大学自动化学院,重庆400065;2.重庆高校汽车电子与嵌入式系统工程研究中心,重庆400065;3.重庆大学光电技术及系统教育部重点实验室,重庆400044)

在现代电子系统中,经常需要产生稳定的重复波形,例如正弦波或者方波。在许多场合,还要求产生波形的频率稳定,并且能够准确调节;甚至还要求能够产生相位保持确定关系的多路输出信号等。传统的LC、RC振荡电路已满足不了高性能信号源要求,通过使用频率合成器代替传统的调谐信号源中的LC、RC振荡电路,能够有效地解决上述问题,提高波形质量。

频率合成技术始于上世纪30年代,随着电子技术的飞速发展,频率合成技术也不断发展进步,其发展过程大致可分为直接模拟频率合成技术、锁相频率合成技术、直接数字频率合成技术三个阶段。直接数字频率合成DDS(Direct Digital Frequency Synthesis)是近年来新的频率合成技术,其具有超高速的频率转换时间,极高的频率分辨率和较低的相位噪声,在频率改变与调频时,DDS器件能够保持相位的连续等特点,因此很容易实现频率、相位和幅度调制,此外还具有可编程控制的突出优点。因此,当今电子系统及设备等频率源设备的设计中,直接数字频率合成器得到了越来越广泛的应用。

1 直接频率合成技术概述

DDS是美国学者Tierney.J、Rader.C和Gold.B等人于1971年在撰写的“A Digital Frequency Synthesizer”一文中首次提出的全数字技术[1],该技术是从相位的概念出发直接合成所需要波形,在频率合成法的原理上取得了突破,并导致了频率合成领域的第二次革命。

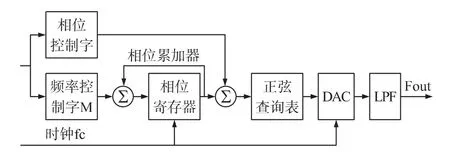

DDS由相位累加器、正弦查询表、数字模拟转换器(DAC)和低通滤波器(LPF)等组成[2-4],其基本工作原理如图1所示。

图1 DDS的原理图

该方法的基本原理就是将存于数表中的数字波形,经数模转换器D/A,形成模拟量波形,经过低通滤波处理后输出所需的波形。

DDS系统的核心是相位累加器,它由一个加法器和一个位相位寄存器组成,每来一个时钟,相位寄存器以步长增加,相位寄存器的输出与相位控制字相加,然后输入到正弦查询表地址上。正弦查询表包含一个周期正弦波的数字幅度信息,每个地址对应正弦波中0°~360°范围的一个相位点[5-6]。查询表把输入的地址相位信息映射成正弦波幅度的数字量信号,驱动DAC,输出模拟量。

相位寄存器每经过2N/M个fc时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS系统输出一个正弦波,从而得到输出正弦波频率为

2 三相交流波形发生器的设计

2.1 设计基本思路

根据DDS原理框图和正弦波频率公式fout=我们可以知道,两种方法可以改变输出信号的频率:(1)通过改变查表寻址的时钟频率fc来改变输出波形的频率。(2)通过改变寻址的步长M来改变输出信号的频率。

针对单片机控制系统的特点,DDS输出信号频率的改变主要就是通过改变寻址步长,即改变频率控制字的M大小来实现。步长即为对数字波形查表的相位增量,由相位累加器对相位增量进行定时累加,存于相位累加器的相位寄存器中,通过相位寄存器值的变化完成查表地址的选定,并将需要的波形数据输出转换即可。

目前,DDS的实现方式主要有两种方式:(1)采用专用集成芯片,如AD9858,通过增加外部辅助电路和控制功能电路即可完成波形输出[2]。(2)采用CPLD或FPGA等可编程逻辑器件相,通过软件编程完成波形输出与仿真[3-4]。但在实际的测控系统中,这两种方式构建系统都需要很多外接电路才能完成波形输出。与AD9858、CPLD或FPGA等芯片实现波形发生器比较而言,单片机能够根据片内ADC采集输入的模拟信号动态设定频率控制字M,正弦查询表可以直接以常量的形式存储在单片机内部程序存储器中,相位累加器则可以通过定时中断完成;同时单片机还可以通过通信等功能实现频率控制和相位控制的设定和检测,具有比较好的灵活性,对于频率比较低的交流信号,采用单片机完成DDS算法具有设计简单、成本低、人机接口友好等优点。

根据项目要求,本设计要求采用0~5 V模拟信号(如温度、压力、高度等)的变化来动态改变频率控制字M的大小,从而控制频率信号的输出,输出频率与输入模拟信号成正比关系,且输出的三相正弦波频率的范围为0~70 Hz。根据项目实际特点,无论在成本和实现方法上都适宜采用单片机完成信号采集和波形输出等一系列工作,PIC16F87X是微芯公司8 bit PIC系列单片机系列的中档产品,采用14 bit的RISC指令系统,在保持低价格的前提下增加了A/D转换器、内部E2PROM存储器、比较输出、捕捉输入、PWM输出、I2C总线和SPI总线接口电路、异步串行通信(SCI)接口电路、模拟电压比较器、LCD驱动、FLASH程序存储器等许多功能,可以方便地在线多次编程和调试[7]。本设计采用PIC16F870芯片作为模块的主控设备,不仅能很好地实现模块功能,而且为以后通信、显示等功能的扩展留下了较好的接口,便于系统升级。

2.2 硬件设计

根据项目设计要求,硬件设计主要包含模拟输入调理电路、三相模拟量输出电路、微控制器电路等几个部分。

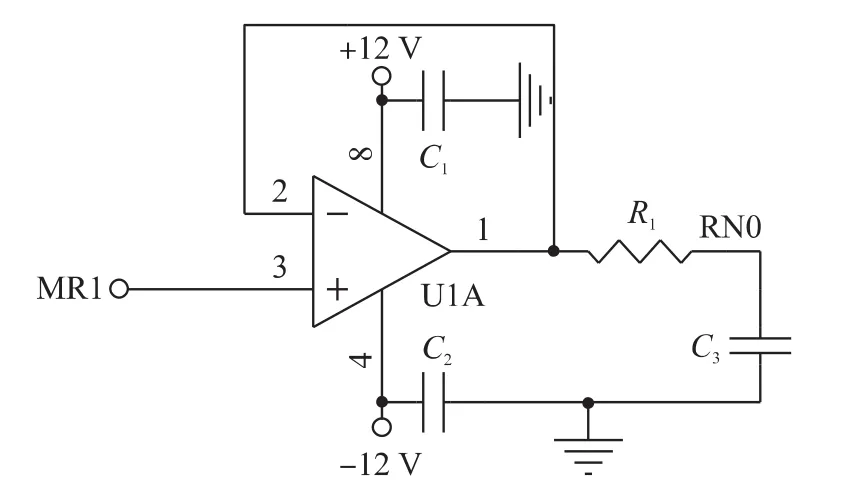

(1)模拟输入信号调理电路设计

根据设计要求,输入信号为0~5 V直流信号,跟单片机片内ADC的采样量程一致,故调理电路不需要作放大变换,这里采用电压跟随器实现,如图2所示,图中R1和C3组成RC滤波电路消除电压纹波。MR1为输入信号RN0直接送入单片机模拟输入采样引脚供单片机采样。

图2 信号调理电路图

AD7226与单片机的接口主要有、A0、A1 及8 bit数据接口。由单片机实现数据写入控制,A0、A1为地址选择线,通过A0、A1选择不同的D/A转换通道,AD7226在为低电平时将8 bit数据接口的数据读入A0、A1确定的输入到通道锁存器中,在上升沿将数据进行锁存,对应通道的输出缓冲器输出对应模拟量,即完成相应的 D/A转换,PIC16F870没有专用的地址总线和数据总线,只能采用通用IO口实现,本设计中采用该芯片的RC3、RC4、RC5 控制、A0、A1引脚实现相应的写入时序,数据线则通过芯片的 PORTB引脚(图中用RB0~RB7表示)完成。本设计中选择参考电压VREF为2.5V,故 SINA、SINB、SINC 输出信号的范围为0~2.5 V,具体接口如图3所示。

设计中包含三相交流信号输出,故DAC选用AD公司的AD7226芯片实现三路交流信号的数字模拟变换输出。AD7226是具有8位精度的四通道DAC,每个输入通道自带输入锁存器可以对输入的数字量进行锁存,输出端带有缓冲放大器,数字和逻辑接口电平与TTL/CMOS(5V)兼容,单片机可以直接与其接口[8]。

(2)DAC与单片机的接口电路设计

图3 DAC与单片机的接口电路图

(3)模拟输出电路设计

根据给定负载需求,本设计需要输出的最大电流为2 A,电压峰值为±10 V,用于转速表的驱动,由AD7226输出的三相交流电SINA、SINB、SINC(如图3)必须经过幅值和功率放大,由于本设计对电压的幅值大小精度要求不高,故幅值放大和滤波可以通过通用运放调理实现,功率放大则需要大电流运放实现,本设计采用Burr-Brown公司的OPA548运放,该运放能够输出3 A的持续电流、5 A的峰值电流,完全能够满足设计需求,具体电路设计入图4。

图4 模拟波形信号输出电路图

图4给出了A相交流信号的输出电路,本文如果没有特别说明都以A相为例,其余两相处理方法类似,图中运放U1B及外围电路实现信号的电平提升和信号放大,即将电压SINA的0~2.5 V电压变换为-2.5 V~2.5 V的电压信号VA,VA经过运放U1C完成滤波和电平放大,U2为采用OPA548大功率运算放大器形成的电压跟随器,实现大电流输出驱动信号VAout。

2.3 软件设计

根据DDS原理,软件设计主要完成模拟输入信号的采集、相位累加、正弦表的查询、三相正弦波模拟量输出控制等功能。具体设计内容如下:

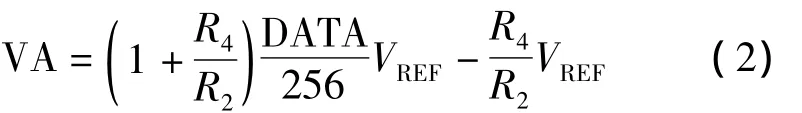

(1)正弦表的制定

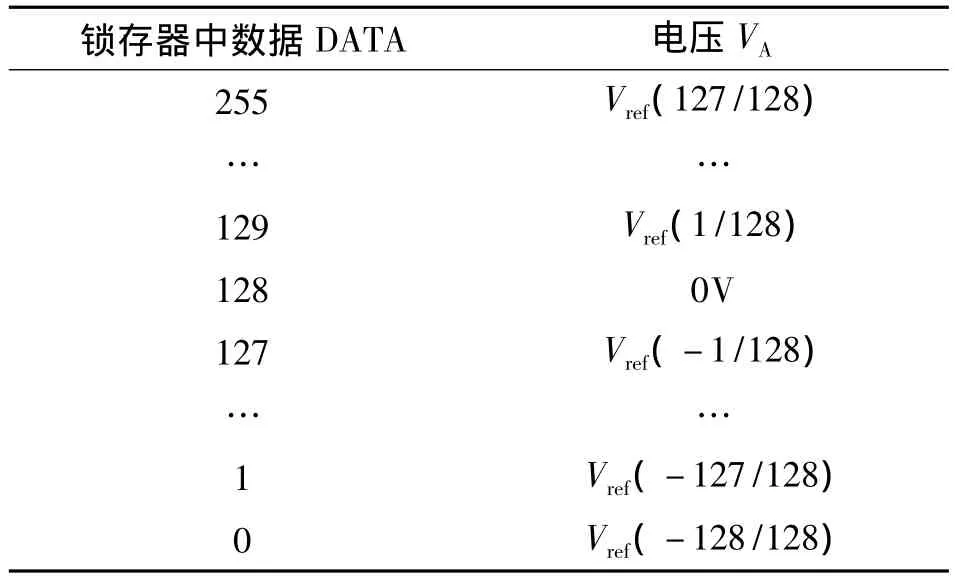

根据AD7226数据手册,我们知道AD7226具有单极性输出方式和双极性输出方式两种形式,分别对应与图4中的SINA和VA信号。即单极性信号为0~2.5 V电压,由图中的SINA给出,双极性信号为-2.5 V~2.5 V可通过图中的VA取得,设计者可以根据实际情况采取不同的设计方法。单极性输出方式对应输出信号SINA下,有:

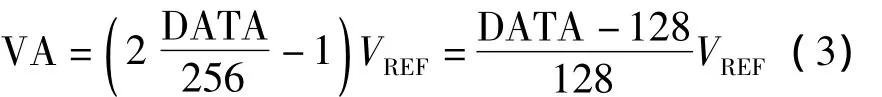

其中DATA为输入锁存器中存储的8位数字,范围为0~255。

本设计采用的是双极性输出方式,由图4得:

DATA的含义同上。取R2=R4即有:

根据式(3)我们可以得到输入锁存器中数据DATA与电压VA的关系如表1所示。

要想使VA输出信号为正弦波,必须由单片机根据DDS控制的方法将波形相位送入AD7226中对应通道的数据锁存器中,再通过AD7226实时根据数据锁存器中的数据输出模拟信号产生期望的波形信号,对于大量低成本的单片机而言,由于运算能力的限制,很难在短时间内通过公式计算正弦函数的值,一般只能通过查正弦表的办法直接从存储器中读取,因此需要计算正弦表。根据AD7226中锁存器中数据DATA与电压VA的关系表可确定正弦表的大小为256 byte,每个数据之间的夹角为360°/256,从而可以代入VA=VREFsin(2πft)中,即可求出正弦表中第i个数据为:

水面比降测量成果显示河道两侧水面线均呈直线且平行,同时还有原断面资料支撑。根据《水文测验实用手册》洪痕可靠度评定标准,确定洪痕及水面比降成果可靠。

通过式(4)即可将需要的正弦表计算出来,该正弦表以常量的形式存储到单片机片内存储器中以供波形输出时查询。

表1 锁存器中数据DATA与电压VA的关系表

(2)主程序设计

主程序主要完成看门狗计数器的清除和A/D采样。单片机片内自带多路A/D输入采集模块,本设计借助片内10 bit分辨率的ADC以定时器中断的方式完成输入信号采样,A/D采样在主程序中完成,以保证相位累加能够得到最新的采样值,提高设备的实时性,具体流程图如图5所示。

主程序在完成单片机初始化,中断和看门狗使能后进入循环函数,单片机自带看门狗,看门狗函数可以清除看门狗计数器,防止程序“跑飞”。A/D转换函数用于实现模拟信号的采集和转换,将输入电压信号转换为频率控制字的M,从而确定输出信号的频率;干扰滤除函数主要用来判断采集到的数据是干扰信号还是真正的输入信号,该函数将干扰信号丢去不用,从而提高系统抗干扰的能力[9]。

(3)中断程序设计

中断程序采用定时调用方式,由定时器中断产生,主要任务是完成相位累加、正弦表查询和输出控制等相关功能,具体流程图如图6所示。

图5 主程序流程图

图6 中断程序流程图

相位累加函数将采样到的输入值(也就是图1中的频率控制字M),与原来的累加结果相加得到新的累加结果,可以采用任意的存储器进行存储,取出该累加器中的相应8位作为正弦表数组的相应元素读取正弦表在该元数下的参量即为对应要输出的交流信号的DATA值,由于B相滞后A相120°,在正弦表中元数间的角差为360°/256,即有滞后120°相当于滞后256/3=85个元数,同样可得C相滞后A相170个元数,通过该值完成波形的相位偏移计算。在输出函数控制中只需分别读出A、B、C三相对应元数中的数据即可。

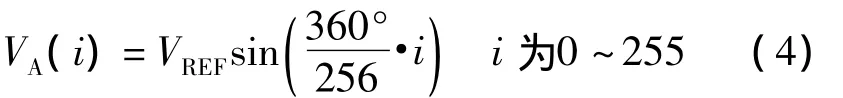

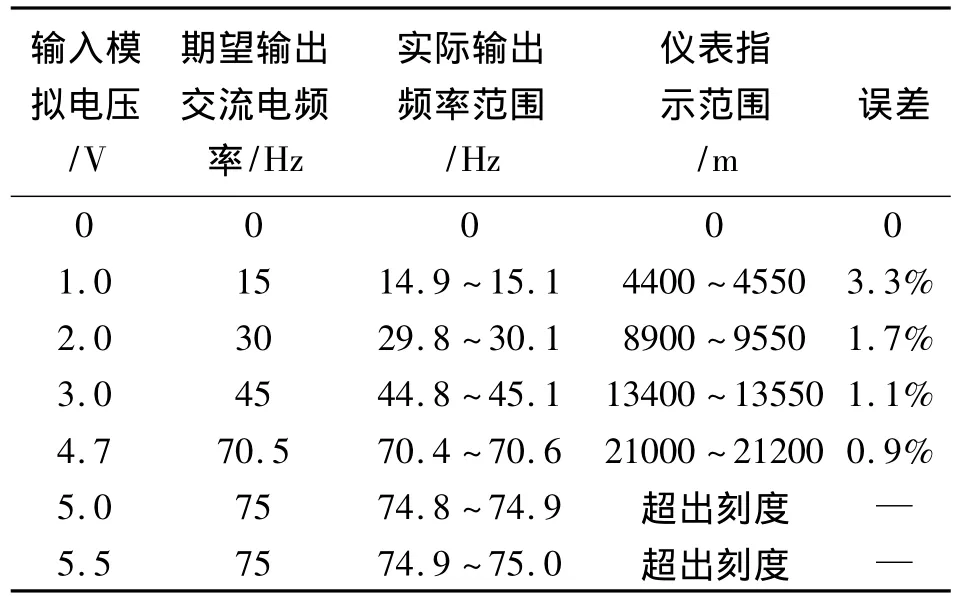

3 实际应用

本控制模块主要针对某研究所的专用测试装置研制,用于模拟飞行器的高度显示控制,其输入信号为模拟信号,代表飞行器的实际高度,输出信号用于驱动三相交流仪表电机指示飞行器高度,交流信号频率与仪表指示高度成正比,为300 m/Hz;为了防止电机转速过高损坏仪表,设定三相交流信号的上限输出频率为75 Hz,实验测得数据如表2所示。

表2 输入电压与输出转速表

实验中,因为MCU对直流信号的获取精度较高,采用了硬件滤波与软件误差纠错相结合的办法,再加上DDS算法的累加效应对单个采集点结果不敏感,故频率输出精度较高,仪表指针指示非常稳定;但由于仪表高度指示分辨率为100 m,数据读取不是很精确,误差的计算仅供参考。

试验表明,在实际驱动信号要求的范围(0~75 Hz)内,控制器通过单片机片内的10 bit A/D转换器,输出的三相交流信号在整个频率范围内的频率分辨率都达到了0.01 Hz以上,仪表指针指示非常稳定和精确。波形发生器从2007年开发完成到现在一直运行稳定,没有发生任何故障,并且具有很好的电磁兼容能力和环境适应能力,得到了该研究所相关技术人员的一致认可。

4 总结

利用单片机完成频率合成技术,其最关键就是要定时完成数据的累加,因此往往采用定时中断的方式实现,这样就能产生稳定的波形,该方法具有运算量较小、算法简单、波形分辨率高、运行可靠性高等特点。

本文通过DDS在单片机的成功应用,完成了三相变频正弦波形发生器的研制,使电路设计更为简化,成本低且可靠性高,为波形发生器的研制提供了一种新的低成本实用方案。同时,该方案不仅可以用来产生变频的正弦波形,亦可以用来产生梯形波等非标准波形,从而降低了波形发生器研制的难度。2010年,基于上述原理开发的可调斜率的梯形波波形发生器也得到了相关技术人员的认可和应用。

[1]Tierney J,Rader C,Gold B.A Digital Frequency Synthesizer[J].IEEE Transaction on Audio and Electroacoustics,1971,19(1):48-57.

[2]邓重一.基于DDS技术的频率合成源设计[J].仪表技术与传感器,2005(10):37-40.

[3]薛延侠,赫建国.CPLD实现DDS信号源的设计[J].现代电子技术,2005(19):73-76.

[4]郭军朝.直接数字频率合成研究及其FPGA实现[D].上海:上海交通大学,2002.

[5]Vankka J.Methods of Mapping from Phase to Sine Amplitude in Direct Digital Synthesis[C]//IEEE Proc 50th AFCS,1996:942-950.

[6]Saul P H,Taylor D G.A High Speed Direct Frequency Synthesizer[J].IEEE Journal of Solid-State Circuits,1990,25(1):215-219.

[7]刘和平.PIC16F87X单片机实用软件与接口技术——汇编语言及其应[M].北京航空航天大学出版社,2002.

[8]Analog Devices Inc.LC2MOS Quad 8-Bit D/A Converter AD7226[Z].2002.

[9]费业泰.误差理论与数据处理[M].6版.机械工业出版社,2010.