同步米里型序列检测电路的错误输出问题

王兆东,刘向军

(华北电力大学电气与电子工程学院,北京102206)

序列检测电路的设计是时序逻辑电路设计中的内容之一,它一直是学生学习数字电路中的难点。同步米里型序列检测电路设计是国内外许多教材文献中反复引用的一个例子[1-3],但本人在学习过程中发现该例题存在没有检测到序列时就输出了检测到信号的错误输出,系统工作出现不正常的问题。在文献[4]中,认为输出波形存在问题的原因是状态化简后的电路有可能不能正常工作了,这种说法有待商榷,因为,电路正常运行时,电路处于有效状态,一定能满足状态转换,与状态化简无关,而只有在无效状态下输入X时出现错误运行与化简有关系。在文献[5]中,为确保系统正常工作,在所设计电路的基础上,输出增加一个延迟环节,使电路等到输入改为下一位输入数据时才输出,是解决输出错误的方法之一,但是,这并没有找到问题的根源,因为问题发生在输入与时钟不同步,以及无效态的次态任意,常常会引起输出错误,并且调整过程缺乏规律,还需在输入解决根本问题。

本文分析了米里型序列检测电路存在的主要问题,给出了确保电路正常工作的有效方法。

1 同步米里型序列检测电路设计

同步米里型序列检测电路设计的一般步骤包括以下几部分[6]:首先根据设计要求,分析逻辑功能,获得原始状态转换图,进行状态化简,得出最简的状态转换图;为每个状态分配代码(状态编码),画出编码后的状态转换图;选定触发器的类型和个数,列写带有驱动端的状态转换表;利用卡诺图化简求出驱动方程和输出方程;检查能否自启动,不能自启动应修改设计,最后画出逻辑电路图。

设计一个时序逻辑电路目标是完成指定的逻辑功能,如果运行出现错误,那么设计不合理,需要对电路进行修正。

多年来国内外许多教材长期反复引用的一个例子是设计一个同步米里型时序逻辑电路实现串行数据检测,当连续输入3个或3个以上1时输出为1,否则输出为0。

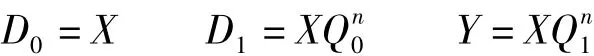

按照时序逻辑电路的设计方法,文献[1]中的例5 ~例9,取S0=00,S1=01,S2=11,选用上升沿触发D触发器实现,对触发器的每个驱动端和整个逻辑电路的输出进行卡诺图化简后,得到驱动方程和输出方程:

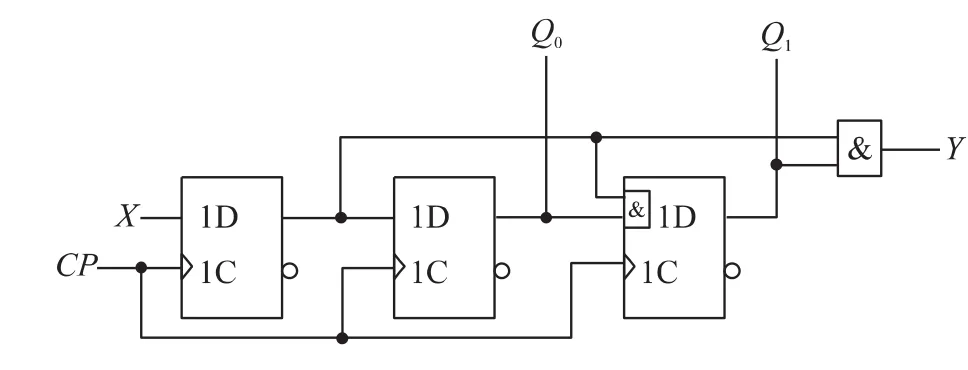

最后,根据驱动方程和输出方程,得到逻辑电路图如图1所示。

图1 111序列检测的逻辑电路图

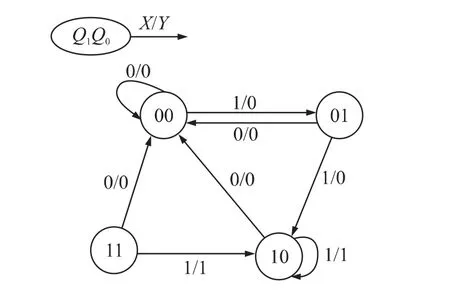

文献[1]中检查了电路能够自启动,其完整的状态图如图2所示。

图2 完整的状态转换图

2 同步米里型序列检测电路设计中存在的问题及解决方法

2.1 输出的设计方面

2.1.1 存在的问题

对于上述电路的输出进行分析,结果表明,当初状态是10,且X为1时,代入输出方程,输出为1。电路输出1表明接受到了3个和3个以上的1,显然,无效的状态为初状态,接收到一个1时就输出了1,不符合题意,它没有任何含义。

2.1.2 解决方法

在不应该输出1的时候输出了1,究其原因是状态转换表中将无效状态对应的输出设为了任意,这样的处理不符合题意,在卡诺图化简时利用了这个任意项,所以有了一个错误的输出,需要修正。

与其设计完再修正,不如在设计中,就应该按照题意设置,确定无效态对应的输出为0。修正方法是修改状态装换表,将现状态10对应的输出改为0。

此时,输出的表达式为:

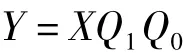

2.2 波形分析方面

输入的序列X一般有电平码和脉冲码两种形式,如果电平码与时钟同步,已知111序列检测中的输入波形对应的输出波形如图3所示,输出波形正常,符合题意。

图3 X输入为电平序列且与时钟同步时的波形分析

但是,在有些情况下是不能正常工作的,检测到两个1时就输出了1。

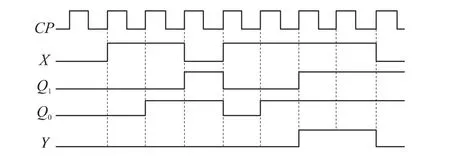

2.2.1 存在的问题

(1)X输入为电平码与时钟不同步

当X输入为电平码与时钟不同步时,其波形分析如图4所示,输出波形在连续输入两个1则错误地输出了1,与题意不符。

图4 X输入为电平序列且与时钟不同步时的波形分析

(2)X输入为脉冲码

当输入X为脉冲码时,分析其波形如图5所示。在连续输入两个1之后同样产生了错误的输出1,与题意不符。

图5 X输入为脉冲序列的波形分析

2.2.2 解决方法

米里型电路的输出不仅与状态有关,还与输入有关,输出不一定与时钟同步,但是随时会受到输入的影响。分析两种情况,原因是输入的X与时钟不同步,如果能把任意的输入都调整到与时钟同步,就可实现如图3的波形分析,输出就会符合题意要求。

为了使X与时钟同步,在X加入检测电路时先加一延迟环节,如D[7]触发器,从而保证输出的正确,改进后的电路如图6所示。

图6 改进电路

(1)X输入为电平码调整后与时钟同步

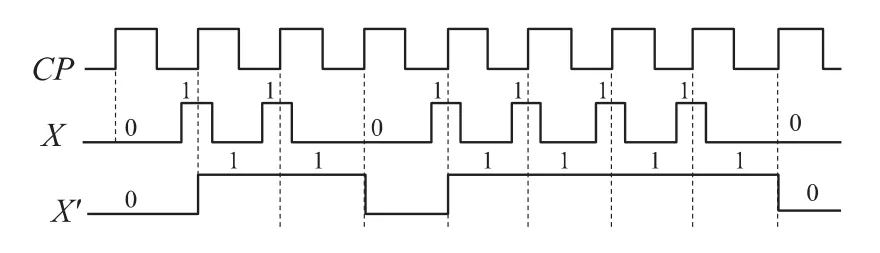

在图6所示的改进电路中,可将图4中的电平码X加延迟后调整为X',波形如图7所示。

图7 电平序列加延迟后的序列X'

(2)X输入为脉冲码调整后与时钟同步

在图6所示的改进电路中,可将图5中的脉冲码加延迟后调整为X',波形如图8所示。

图8 脉冲码经延迟后的序列X'

输入序列经整理后的为X',使序列与时钟达到同步,那么所设计的电路可实现如图3所示的波形分析,完成111序列检测,消除了不应该输出1却输出了1的现象。

2.3 自启动方面

对于含有无效状态的时序逻辑电路,假如电路由于某种原因进入无效状态,在有限个时钟脉冲作用下最终能到有效的循环状态中,则称该电路具有自启动能力[8]。

2.3.1 存在问题

由图2可知,设计的电路图能够自启动,在卡诺图化简时任意态的使用恰好使状态转换符合题意。但是,同样是111序列检测,设计方法相同,只是按照S0=00,S1=01,S2=10进行状态编码,那么对所设计的电路进行自启动检查,将得到如图9所示的状态转换图。由图9可知,虽然能够自启动,但是状态转换并不符合题意,不能描述原始状态表所描述的功能。比如,当输入序列11110110111序列时,输出应该为00110000001,如果从无效状态开始,则会输出11110000001,显然输出不符合要求,经历2个时钟后电路工作正常。文献[1]中101序列检测的设计结果,也存在这个问题,当输入序列10101011101时,输出应该为00100010001,但是如果从无效状态开始,则会输出10001000001,序列检测经历6个时钟后才能正常,没有规律可循。

图9 按S0=00,S1=01,S2=10编码所设计电路对应的状态转换图

2.3.2 解决方法

有此现象的原因,是无效状态的次态不合理,是状态转换表的无效状态对应任意次态引起的。所以,电路虽然能自启动,但是也应该修正其驱动方程。状态编码为S0=00,S1=01,S2=10的111序列检测电路的设计中,无效状态的次态不应该选择任意,当输入0时,次态应设为S0;当输入1时,次态应设为S1,修正其驱动方程,进而修正所设计的电路。还以输入11110110111序列为例,假设初态为无效态11,则能够输出00110000001,符合题意。

此例说明,时序逻辑电路的设计在状态转换表的分析中不能一律把无效状态的次态看成任意,在设计中应该根据题意确定次态,既能保证了电路能自启动,又能使状态转换不会出现错误。

3 结语

在米里型同步时序逻辑电路的设计中,电路的输出不应该有任意项,只有规定的序列下输出才为1,可直接获得输出的表达式,不需要卡诺图化简,也不需要修正;当输入与时钟不同步或脉冲序列时,在输入端加延迟环节,调整输入与时钟同步,保证了输出的正确;无效态的次态任意,常常会引起输出错误,并且调整过程缺乏规律,所以,本文建议其次态应该根据题意确定而不是任意态。此方法,在同步米里型时序逻辑电路的设计中有通用性。

[1]李月乔.数字电子技术基础[M].北京:中国电力出版社出版,2002:268-295

[2]阎石.数字电子技术基础[M].4版.北京:高等教育出版社,1997:286-290

[3]康华光.数字电子技术基础[M].4版.北京:高等教育出版社,1997:286-290

[4]龙胜春.米里电路设计的状态化简问题[J].电气电子教学学报,2002,24(4):52-53

[5]陈云洽.串行数据检测器的设计[J].电气电子教学学报,2006,28(2):110-113

[6]徐勇谦,万延.时序逻辑电路设计方法[J].科技创新导报,2008(10):61-62

[7]张富彬,HO Ching-yen,彭思龙.静态时序分析及其在IC设计中的应用[J].电子器件,2006,29(4):1330-1333

[8]任俊原.基于次卡诺图的JK激励函数最小化方法及时序逻辑电路自启动设计[J].浙江大学学报(理学版),2010,37(4):425-427