一种DDS任意波形发生器的ROM优化方法

李 超,谢雪松,张小玲

(北京工业大学 半导体可靠性研究室,北京 100124)

随着数字通信技术的发展,基于直接频率合成技术(DDS)的信号发生器,以其频率转换速度快、频率分辨率高、相位连续、波形稳定度高以及便于程控等诸多优势,得到了越来越广泛的应用[1]。与此同时,DDS技术的一个缺陷也逐渐显现出来,即要想获得高精度的波形,就要以占用大量的存储资源为代价[2]。对于常见的基于现场可编程门阵列(FPGA)的DDS信号发生器的设计方案,为了不影响系统的运行速度,波形数据一般都存放在FPGA的片上RAM资源中。而FPGA的片上RAM资源有限,且其存储空间的大小与FPGA芯片的价格成正比,这无形中增加了系统的开发成本。针对这一问题,本文提出一种改进的、基于FPGA的DDS任意波形发生器的设计方案。该方案在不改变波形精度的前提下,将波形数据量降低为传统设计方案的25%,并且能够输出正弦波、三角波、占空比可变的方波和升/降锯齿波5种波形。

1 DDS基本原理

DDS技术的核心是利用累加器将频率控制字、相位控制字和波形控制字转化成读取波形数据的地址值,再将读出的波形数据与幅度控制字相乘得到不同的波形,其结构框图如图1所示[3]。

输出波形的频率由频率控制字与输入时钟共同决定,其关系表示如下:

其中,fo为输出频率;K为频率控制字;N为一个正整数,其数值一般为频率控制字K的位宽;fc为输入时钟的频率。由累加器输出的结果与相位控制字相加,相当于将输出波形进行一次相移,从而确定波形的相位。因为DDS任意波形发生器能够产生多种类型的波形,所以需要将不同类型的波形数据分区块地写入波形存储器(ROM)中,将之前产生的地址值与波形控制字相加,即为用于将地址指向特定的波形类型的数据所在的区块。读出的离散波形数据经过D/A转换器就转换成了连续的模拟信号,再经过低通滤波器(LPF)就可以得到所需要的平滑波形输出。

2 DDS优化设计

2.1 整体设计方案

本设计的DDS任意波形发生器能够直接产生0~1 kHz的正弦波、三角波、升/降锯齿波和占空比可变的方波等5种波形,经过后接的功率放大电路其幅值可达65 V。系统采用型号为AD9746的高精度差分D/A转换芯片,其数据位宽为14 bit,这就意味着每个波形数据都为14 bit位宽,则对模拟信号采样生成波形数据时,就需要采集214个数据点。如果按照传统的DDS设计方案,所占用的片上RAM资源为:波形类型数×数据位宽×数据量=5×14×214=1 146 880 bit。 由此可以看出,资源的占用量已经远远超出了大多数常用FPGA芯片的片上资源总量。为了减小资源的占用,本设计首先对不同类型的波形数据的存储方式进行优化。

如图1所示,传统的DDS任意波形发生器是将所有类型的波形数据按区块存储在ROM中,按照需求读出某一区块的数据用于产生相应波形。这种设计方案的ROM利用率很低,以存储5种波形数据为例,在生成某种波形时,ROM空间的80%存储的都是无关数据。因此,为了节省空间,将不同类型的波形数据以数组的形式写在软件中,当需要产生某种波形时,通过波形控制字的控制,将指定的波形数据移入FPGA的片上存储器。由于软件运行的存储区域为片外的SDRAM,而SDRAM的存储空间较大,因此,用SDRAM的空间占用取代FPGA片上存储资源的占用可以在很大程度上降低成本。

另外,从式(1)中可以看出,当频率控制字 K取1时,可以得到系统的频率分辨率[4]:

由此可见,N的取值越大,输出频率的步长就越小,频率分辨率也就越高。本设计采用了32 bit字长的频率控制字,参考时钟为100 MHz,所以频率分辨率可达0.023 2 Hz。但是,累加器输出的结果将要作为对ROM寻址的地址,而ROM的寻址空间显然无法达到232bit。为了使地址值能够与ROM中的数据一一对应,又不影响频率分辨率,这里截取累加结果的高14位作为寻址的地址值,但并不表示ROM的寻址空间为 214bit,而是对不同的波形类型将对这14位的地址值做不同的处理,从而进一步对ROM进行优化。

2.2 正弦波、三角波的ROM优化设计

因为系统中采用的D/A的精度为14 bit,所以在对参考的模拟波形采样时,需要采集214个离散的数据点。但是不难发现,正弦波和三角波在4个象限的波形具有很好的对称性,因此,为了进一步对ROM进行优化,只存储波形在第一象限的数据点,利用基于VHDL硬件描述语言编写的硬件反相器对寻址地址值和波形数据进行处理,就可以在不改变数据精度的情况下得到完整的波形[5-6]。由于三角波和正弦波的原理完全相同,所以这里仅以正弦波的ROM优化设计为例进行说明,其硬件框图如图2所示。

从图2中可以看出,虽然累加器输出的结果为14 bit位宽,但是真正对ROM寻址的只有12 bit。实际上,只是累加器输出的最高2位用于对生成波形的4个象限进行选择,其对应关系如图3所示。

在正弦波的生成电路中,ROM只存储第一象限,即图3中是高2位为00时所对应的波形数据。由图3可分析得出,第二象限的波形数据相当于对第一象限数据进行反方向读取,即对地址值先取反再寻址;第三象限的波形数据为第一象限数据的相反数,即对波形数据先取反再读取;第四象限的波形数据为第三象限数据的反方向读取,即同时对地址值和波形数据取反再寻址读出数据。综上所述,反相器1在累加器输出结果的次高位为0时不采取任何操作,在次高位为1时将地址值取反;反相器2在最高位为0时不采取任何操作,在最高位为1时对ROM中的波形数据取反。这样利用2个反相器就可以仅存储212个数据点,还原出14 bit精度的完整正弦波形和三角波形。

2.3 升、降锯齿波ROM优化设计

与正弦波和三角波不同,升/降锯齿波为单调线性波形,所以在针对参考波形进行14 bit精度采样时,将生成的214个数据点每隔3个存储1个,把所存储的数据点个数减小到212个,这对于单调的线性波形几乎没有影响。因此,在寻址时只需要截取累加器输出的高12 bit作为地址值。另外,为了进一步简化设计,考虑到降锯齿波实际上是对升锯齿波的波形数据进行反向读取得到的,因此,可以仅存储升锯齿波的波形数据,利用波形控制字和反相器就可以得到降锯齿波形。其电路框图如图4所示。

2.4 方波生成电路设计

与之前介绍的所有波形的性质不同,方波只是高低电平之间的转换,转换的时间即为占空比。因此,在方波生成的电路中,只需把单一的高电平数据存入ROM中,利用定时器控制一个反相器,在特定时间将ROM中读出的数据取反,就可以生成占空比可变的方波。其电路框图如图5所示。

定时器中,以输入的占空比控制字为初值,每个时钟周期对频率控制字进行一次累加。当累加结果≤232-1时,控制位为0,反相器不工作,D/A直接收到 ROM中读出的数据,即输出方波高电平;当累加结果>232-1时,控制位置1,反相器将ROM中读出的波形数据取反,即输出方波的低电平。累加结果为33 bit位宽,当发生溢出时,自动回到初值状态,从占空比控制字开始继续对频率控制字进行累加。因此,通过输入不同的占空比控制字就可以得到占空比可变的方波。

3 测试结果

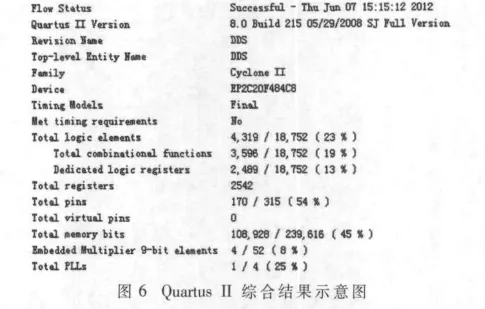

按照上述优化方法设计出基于DDS的任意波形发生器,FPGA的片上存储器仅需要存储4 096个14 bit位宽的波形数据,就能够实现可输出5种波形的任意波形发生器。在Quartus II 8.0软件中的综合结果如图6所示。

从图6中可以读出,片上存储资源的占用量仅为108 928 bit,这是因为中间过程中用到的寄存器和嵌入的NIOS II软核占用了一部分的存储空间。利用RIGOL公司生产的型号为DS1102CA的示波器可观察到最终的不同频率、不同幅值的输出波形,如图7~图12所示。

若按照传统的设计方案,5种波形、14 bit精度的DDS任意波形发生器将占用FPGA片上大于1 Mb的存储空间,而符合这个要求的FPGA芯片市场价格一般都接近千元。本系统采用Altera公司生产的Cyclone II系列的FPGA芯片EP2C20F484C8为核心处理器件,能够大大减小FPGA的片上资源占用,其市场价格仅为100元左右,很大程度上减小了成本。

[1]张严,洪远泉.基于FPGA的任意波形发生器设计与研究[J].现代电子技术,2011,34(10):157-159.

[2]杜伟韬,卢起斌,徐伟掌,等.面积优化的调相 DDS软核编译器设计与实现[J].微电子学,2008,38(3):381-384.

[3]江志浩,孙明珠,蔡德荣.高精度 DDS的 FPGA资源优化设计[J].微计算机信息,2009,25(1-2):191-193.

[4]傅沈文,曾广玺.基于DDS技术的高性能脉冲信号源设计[J].微计算机信息,2011,40(4):108-109.

[5]蓝天,张金林.直接数字频率合成器DDS的优化设计[J].电子技术应用,2007,33(5):42-44.

[6]李建磊,马震,庄波,等.直接数字频率合成器(DDS)精度提高方法研究[J].滨州学院学报,2006,22(3):43-46.