基于CY7C68013A的FPGA配置和通信接口设计

刘志华 ,郭付才 ,彭新伟 ,陈吉东

(1.解放军理工大学 气象海洋学院 探测与装备工程系,江苏 南京 211101;2.南京军区气象水文中心,江苏 南京 210016;3.南京杨辰科技有限公司,江苏 南京 210022)

通用串行总线(USB)因具有传输速度快、支持热插拔、易于扩展以及即插即用等优点,已经成为计算机与外部设备进行数据交换的常用接口。USB控制器是一种集成了USB总线协议的微控制器,利用USB控制器,用户可以在不深入了解USB协议的情况下设计完整的USB接口,这也促进了USB接口的广泛应用[1]。

目前,软件无线电技术越来越成熟,FPGA的应用也更加广泛。一块配备了USB接口的FPGA数据处理模块可以应用到各种高速数据采集、处理和传输场合。而在项目研发过程中,随时都需要对FPGA进行编程调试。基于此,本文研究和设计了一种可以同时实现对FPGA进行配置和数据通信的USB接口。

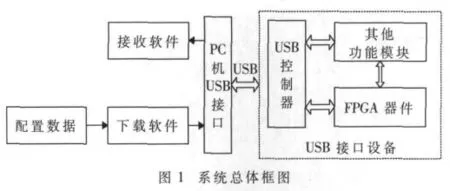

1 系统总体设计

系统总体框图如图1所示,系统主要包括以USB控制器为控制核心的USB接口设备、PC机上的应用软件和驱动程序以及相关的固件程序[2]。系统工作原理如下:ISE软件生成的FPGA配置文件由下载软件下载到USB接口设备中,由CY7C68013A控制器实现对FPGA芯片的被动配置;FPGA配置成功后由CY7C68013A芯片返回配置成功信息;计算机收到配置成功信息后就可以关闭下载软件、打开接收软件,正常接收FPGA向计算机发送的通信数据。

2 系统硬件设计

2.1 CY7C68013A器件

系统中的USB控制器选择CYPRESS公司EZ-USB FX2LP系列的CY7C68013A单片机,它主要包括USB2.0收发器、智能串行接口引擎(SIE)、增强型 8051微处理器、16 KB的RAM、4 KB的FIFO存储器、地址和数据总线、I/O口、I2C控制器和通用可编程接口(GPIF)。

CY7C68013A的串行接口引擎负责完成独立串行数据的编解码、差错控制、位填充等与USB协议有关的功能,简化了固件程序的开发;通用可编程接口支持所有通用的总线标准,可与外部ASIC、DSP等直接连接。CY7C68013A芯片内部包含3个固定的、64 B端点缓冲区,分别是 EP0、EP1IN和 EP1OUT。其中,EP0是默认的控制传输端点,EP1IN和EP1OUT支持快传输、中断传输和同步传输,它们只能由8051内核的固件访问;另外还有4 KB的可配置端点缓冲区,分别是 EP2、EP4、EP6和EP8,它们是大容量宽带的数据传输端点,无需8051固件干涉便可与外围电路完成高速数据传输。这4个端点具有非常灵活的配置方式,可以适应多种场合下的宽带要求。

2.2 硬件电路

系统硬件电路如图2所示。CY7C68013A控制器工作在从属FIFO模式,I2C总线上连接一片 EEPROM芯片(24LC64)。CY7C68013A的固件程序由EEPROM烧写器烧写到24LC64中,上电后自动加载到内部RAM中。FD是双向的数据传输总线。FLAGA、FLAFB、FLAGC是 FIFO标志管脚,指示FIFO的空满程度,保证数据的有效存取。FIFO_ADR[1:0]用于选择与FD连接的4个端点缓冲区。SLRD和SLWR分别作为FIFO的读写选通信号,SLOE用于使能数据总线FD的输出。PKTEND是CY7C68013A向PC发送数据的控制端。IFCLK是48 MHz的接口时钟,由芯片内部产生,控制FPGA配置数据的的读取。PE0与FPGA的PROG引脚相连,是FPGA初始化控制引脚;PE1与FPGA的RDWR引脚相连,是 FPGA配置数据的读写选择端;PE2与FPGA的DONE引脚相连,是FPGA配置成功指示信号。FPGA的配置模式管脚M[2:0]=011,将FPGA设置成从机串行模式[3-4]。

3 系统软件设计

3.1 CY7C68013A 固件程序设计

CY7C68013A的固件程序是指在芯片内部RAM运行的程序代码,它是USB接口设计的核心部分。CY7C68013A的固件程序有两种加载方式:一种是在线下载方式,这种方式是将固件存储在计算机中,在计算机上编写一个能自动下载以及设备从枚举功能的固件下载驱动程序,当CY7C68013A连接上计算机后由驱动程序下载固件;另一种方式是将固件程序存储到片外的EEPROM芯片中,上电后自动将固件加载到内部RAM中。由于第二种方式有扩展性好、操作简单等优点,本文采用的是第二种方式。为了简化固件编程,CYPRESS公司提供了固件编程框架,用户只需在此框架下添加USB描述表、收发数据的通信代码和相关的控制代码就可以完成固件编程[1,5]。 固件框架文件如表 1所示。

表1 固件框架文件

用户在编写固件程序时,只需对bulkllop.c和dscr.51两个文件根据具体设计需求修改相应的代码。固件框架内主要使用的函数如下:

TD_Init()函数:主要完成 CY7C68013A的初始化,它只会在USB启动后调用一次。函数里添加的初始化代码包括CPU时钟频率设定、USB工作模式选择、I/O口配置、端点选择及传输方向设置、FIFO的配置等。

TD_Poll()函数:是用户调度程序,在设备运行时被重复调用,编写需要反复执行的代码。其主要功能是对各个端点的状态进行查询,实现端点间数据的交互。

TD_suspend()函数:在设备进入挂起状态前调用,在其中加入适当的代码,配置设备的工作状态,可使设备处于低功耗状态并返回真值。改动TD_Suspend的程序代码,使其返回为假,可使CY7C68013A不进入挂起状态。

DR_VendorCmnd()函数:是自定义命令代码的书写处。fw.c固件会自动调用函数里的代码。

ISR_Ep0in()interrupt 0~ISR_Ep8inout()interrupt 0 函数:是当使用端点中断传输时的中断代码书写处。

CY7C68013A的固件编程框架流程如图3所示。

针对本文提出的采用CY7C68013A芯片设计USB接口,以实现对FPGA的配置和通信功能,其相关的设置如表2所示。

表2 CY7C68013A端点配置表

在TD_Init()中对端点的设置如下:

(1)EP2:用于传输FPGA的配置数据(XXX.bit文件)。一次传输数据的大小与CY7C68013A配置成USB1.1还是USB2.0有关。当配置成USB1.1时,必须保证一次只传送64 B,不能超过该值;当配置成 USB2.0时,一次最多可以传送512 B,也可以只传送64 B。在void ISR_Ep2inout(void)interrupt 0中,将得到的数据对FPGA进行配置。使用AUTO PTR可以节约时间,配置速率为6 Mb/s左右。

(2)EP4:用于传送控制参数,其设置方法与EP2相同。在void ISR_Ep4inout(void)interrupt 0中,将从应用软件传来的控制命令(包含对FPGA的配置命令)传给FPGA。

(3)EP6:用于采集数据。将其设置成SlaveFIFO模式,AUTOIN有效,IFCLK实现同步,16 bit数据宽度。在void ISR_Ep6inout(void)interrupt 0中,将FIFO中的数据发往USB。AUTOIN=1,在数据传输中,自动完成传输,不需要单片机的参与。

(4)EP8:用于传送状态数据。由于用了双缓冲,在得到状态数据时,要多读2次才能得到当前的状态信息。在void ISR_Ep8inout(void)interrupt 0中,将从FPGA得到的状态数据发往USB。

此外,在中断程序中,要添加中断标志清除的语句,但在EP6的中断中,由于设置了AUTOIN=1,则不需要。

3.2 设备驱动程序

设备驱动程序是用户访问设备的接口。EZ-USB开发系统提供了装载驱动程序开发模板,利用模板开发设备驱动比较简单。CYPRESS公司针对CY7C68013A提供了全新的驱动程序CYUSB.SYS。安装驱动之前,必须先根据VID/PID正确编辑CYUSB.INF文件,在文件中添加自己的PID/VID代码和设备描述;连接设备时,将根据硬件上的PID/VID查找INF文件中对应的驱动,如果找不到,则在设备管理器中将显示“68013 EEPROM MISSING”的字样。安装驱动时,找到修改好的CYUSB.INF文件,驱动即可被正确安装,此时设备可以正常使用了[6]。

3.3 主机应用程序

主机应用程序包括对FPGA配置程序用的下载软件和通信用的数据接收软件。下载软件用VC6.0进行开发,它将ISE软件开发的FPGA配置文件(.bit文件)通过CY7C68013A芯片下载到FPGA中实现对FPGA的配置,并返回配置状态信息[7]。下面是下载软件与CY7C68013A芯片的通信过程与格式:

(1)下载软件对CY7C68013A芯片控制的命令发往pipeNum=1,结构为:

数据接收软件可以根据实际需要进行编写,本设计采用通用的USB调试助手软件接收FPGA发送的二进制信息。

4 系统功能测试

主要测试系统实现对FPGA的配置和数据通信两方面的功能。通过下载软件的FPGA配置界面,将XC2VP4.bit配置文件下载到FPGA中。FPGA配置程序的主要功能除了完成相关的初始化配置之外,还向USB口交替发送 16 bit高电平“1”和低电平“0”。配置成功后会返回“FPGA配置成功”信息。此时关闭下载软件,打开USB数据接收软件,接收数据如图4所示,表明实验成功。

本文介绍了一种利用CYPRESS公司的USB控制器CY7C68013A芯片设计USB2.0接口的设计方案,并进行了实验验证。由于方案同时可对FPGA进行配置和数据通信,因此它可以为开发人员实时调试FPGA带来方便,同时也方便系统在后期的更新换代。

[1]钱峰.EZ-USB FX2单片机原理、编程及应用[M].北京:北京航空航天大学出版社,2006.

[2]王晓丽,龙兵,李力.基于 FPGA的 USB数字 I/O设备设计[J].电子测量技术,2011,34(10):57-59.

[3]刘森,赵明生.通过 USB接口实现 FPGA的 SelectMap配置[J].微计算机信息,2009,25(4-2):1-2,269.

[4]张俊涛,王豫莹.基于 FPGA和 USB2.0的高速数据采集系统[J].仪表技术与传感器,2011(10):46-48.

[5]马俊涛,李振宇.SlaveFIFO模式下CY7C68013和FPGA的数据通信[J].中国传媒大学学报(自然科学版),2009,16(2):38-44.

[6]Airhand.EZ-USB 68013A开发指南[EB/OL].[2009-03-13].http://forum.eepw.com.cn/thread/148408/1.

[7]葛亮.Visual C++从入门到实践[M].北京:清华大学出版社,2009.