基于FPGA的一体化实时图像采集系统设计

李 华,刘 萌

(商洛学院 物理与电子信息工程系,陕西商洛 726000)

自20世纪60年代问世以来,CMOS图像传感器因其体积小、功耗低、工作电压单一、抗辐照能力强等优点使其在成像领域得到了广泛的应用和发展[1-2],成为现代光电子学中最活跃、最具影响的应用器件之一。随着基于CMOS图像探测器的实际应用越来越广,对其像元输出信号进行快速采样、存储及图像数据处理就显得尤为必要。传统的使用单片机作为控制器对数据进行间断式采集与处理,处理速度较慢,实时效果不好[3];而通过DMA通道将数据传到上位机由PC机进行处理,占用资源又较大[4];也有用ARM或者FPGA来实现对数据的处理,虽然速度和集成度提高了,但是许多都是依靠示波器或数码管来实现测量结果的显示,功能单一,不利于信号通信的控制[5]。再加上不同厂家的图像探测器输出图像的格式又各不相同,传统方法往往是先按照探测器输出的格式采集图像,再根据实际需要进行数据重组,但是,这种方式得到的图像存在一定的滞后,在一些对实时性要求较高的场合是远远不能满足要求的。另一方面,相比CPU,FPGA集成了多个运算单元,功耗小、体积小、成本低,因此用FPGA硬件实现图像采集和处理,并行处理程度高,可实现图像的高速处理[6]。本文正是在这样的背景下,设计了一套以FPGA为核心控制单元,结合SDRAM存储器的一体化CMOS图像探测器实时图像采集系统,克服了以上不足,不仅取得了较好的效果,而且该设计还具有比较好的通用性。

1 系统方案设计

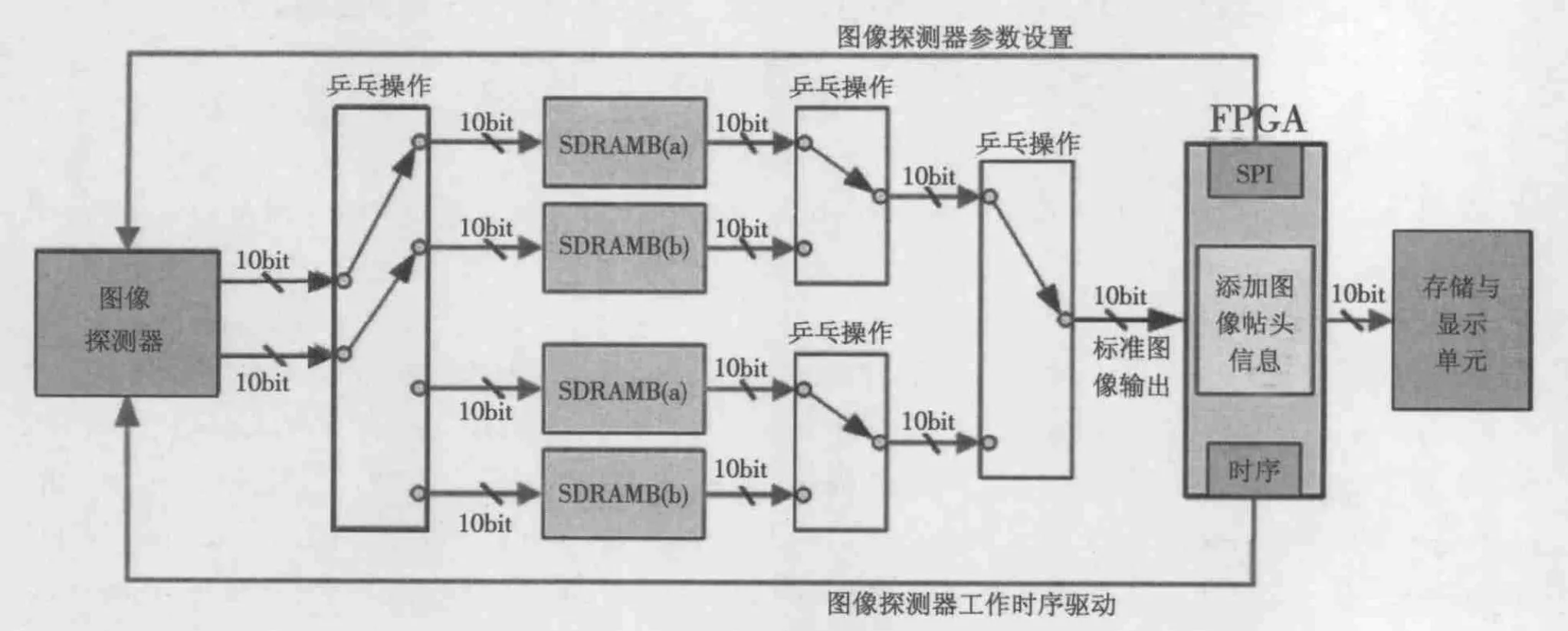

本系统的总体设计方案如图1所示,整个系统包括:CMOS图像探测器、存储单元、FPGA控制系统和存储显示单元等。其中,CMOS图像探测器选用的是DALSA公司的产品,FPGA应用Xilinx公司的XC2V3000,SDRAM则是尔必达公司的EDS5116ABTA-75,且由4片组成,用于完成图像数据的乒乓操作。系统的工作过程为:首先,FPGA上电稳定后根据外部指令给CMOS图像探测器发出工作状态配置参数,然后输出探测器正常工作所需的时序信号,这样,图像探测器就能以2路同时输出的形式输出图像了,但是这样的输出格式图像采集装置往往不能实时显示与存储,也给后续图像应用带来不便,为了达到图像实时、顺序输出的目的,系统将2路输出图像送给4片SDRAM进行整形,再送给FPGA用于图像帧头信息的添加,最后输出给存储与显示单元。在主时钟采用100 MHz的情况下,整个系统满足了以全帧、20 f·s-1工作模式下图像的准确实时输出。

图1 系统原理框图

2 关键技术设计

本系统设计重点体现在两方面,分别是基于Verilog-HDL硬件描述语言[7]的SDRAM及乒乓操作设计和图像帧头信息的添加设计。

2.1 图像探测器输出图像格式特点

不断的输出图像了,但是,由于本文图像探测器采用的是图像双路同时输出的模式,所以,一次输出的是奇偶两行数据,对于目前大部分图像采集卡,这种格式的图像是不易直接采集与应用的,因此要进行图像数据的整形操作。

与大多数CMOS图像探测器一样,本文探测器的工作过程分为两部分——工作参数的配置和数据的输出。由于探测器工作参数的配置设计比较简单,按照手册进行即可,因此,本文主要研究图像数据的处理。

按照手册为探测器提供时序,并以2352*1728大小循环工作,就可以让探测器连续

2.2 图像数据整形设计

2.2.1 SDRAM时序设计

SDRAM是一种应用广泛的存储器,具有容量大、数据读写速度快等优点,特别适合图像等需要海量存储的应用领域[8]。SDRAM内部存储单元由若干个相当于矩阵的bank组成。行地址就是矩阵的行元素,列地址相当于矩阵的列元素。因此给定的bank地址结合行地址和列地址就能唯一的指定一个存取单元。

SDRAM的工作过程与其它存储器件不同之处在于,系统刚上电初始化完成后,所有的行都处于非活动状态,不能进行相应的读写操作,这时就需要先激活相应的行,并经过从行地址选择到列地址选择的延迟之后,才可以根据read/write请求信号决定SDRAM将要进行数据读操作还是数据写操作。

本文SDRAM控制时序主要由三部分组成:状态控制模块、命令产生模块和图像数据存取模块。状态控制模块由初始状态机和工作状态控制状态机构成,它是SDRAM系统设计的核心,可以根据需要完成相应状态的切换;命令产生模块主要是根据SDRAM的工作状态产生SDRAM需要的命令信号;而图像数据存取模块主要是根据控制逻辑对探测器输出的图像数据进行SDRAM的写入或读出。

分析SDRAM的工作原理可知,它之所以不会发生数据丢失的情况是因为对存储体电容定时充电刷新的缘故,因此SDRAM工作时的刷新操作是至关重要的。SDRAM的刷新操作,本文在设计上分两种情况进行研究,对于没有图像时的刷新,采用每7.5 μs刷新一次的形式,这样,64 ms内刷新的次数为8533次,满足SDRAM不丢失数据8192次的最少刷新次数[9]。而对于正常工作时的刷新,则采用在图像帧逆程期间刷新的方式,本设计图像的帧逆程时间为25 ms左右,因此,帧逆程内每3 μs刷新1次,满足SDRAM最小刷新间隔67.5 ns的要求,这样,一帧图像帧逆程的刷新次数就是8333,满足64 ms刷新8192次的要求,同时满足20 f·s-1的输出需要。

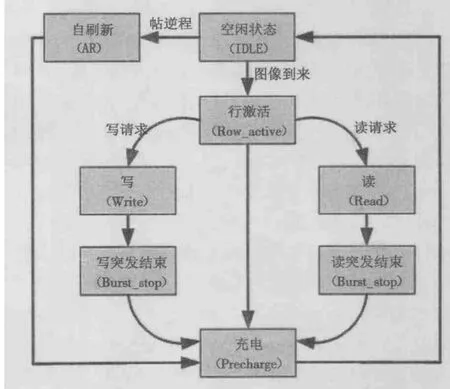

本文图像探测器在全帧模式时输出一行图像的长度是2352,而SDRAM一行的长度是1024,因此,一行图像的长度是SDRAM一行存储深度的2倍多,本文SDRAM采用了full page burst工作模式,即一次对SDRAM的一行进行读写操作,具体的工作状态与过程如图2所示。

图2 SDRAM的工作状态与过程

由图2可以看出,当SDRAM读写完一行1024×10 bits后,要进行 Burst Stop 操作,再对SDRAM进行刷新,然后读写下一行。由于探测器输出的一行图像2352个数据是连续的,而这些图像数据在SDRAM读写的过程中被分成两个1024长度的数据和一个304长度的数据,中间是Burst Stop等行间隔状态,所以,两者之间就存在了速度上的不匹配,这里就要用到FIFO,当然,FIFO的深度不需要很深,由于一次Burst Stop和刷新操作的时间约为15个时钟,所以,本文FIFO的深度设为20*3个时钟即可,如图3所示。具体设计上,以写数据为例,当工作状态是Burst Stop和刷新时,将FIFO读使能信号禁止,终止读操作,使图像数据在FIFO中缓存,当进入下一行写状态时再恢复读使能,而且在一行图像的逆程期间还要对FIFO进行复位,保证了数据的连续性与准确性。这样,探测器的数据就能完整无误的在SDRAM中写入与读出了。

图3 写一行1024个数据后进行Burst stop操作的仿真波形

2.2.2 基于SDRAM的乒乓操作

为了达到实时、顺序输出图像数据的目的,本文设计应用了4片SDRAM进行乒乓操作,如图1所示。具体的工作过程为:图像探测器在时序驱动下,奇、偶行图像数据从两个输出通道同时输出,首先将第1帧图像的奇数行图像存储在SDRAM A(a),将偶数行图像存储在SDRAM A(b),当存储完第1帧后,在图像帧逆程期间切换读写关系,将第2帧图像的奇数行数据存储在SDRAM B(a)中,同时将偶数行数据存储到SDRAM B(b)中,与此同时,对SDRAM A(a)和SDRAM A(b)进行乒乓读操作,即在奇数行时读SDRAM A(a)的图像数据,在偶数行时读SDRAM A(b)的图像数据,进行拼接,完成图像的顺序输出。当存储完第2帧图像后,再将第3帧图像存储在SDRAM A(a)和SDRAM A(b),同时乒乓读取SDRAM B(a)和SDRAM B(b)中的第2帧数据,顺序输出。如此反复就完成了图像数据的实时顺序输出,达到图像数据整形的目的。

2.3 图像帧头信息添加

经过数据整形后,图像已经能够实时的显示和存储了,但是,为了研究上的方便,通常还要将图像的一些拍摄条件信息,比如:拍摄时间、图像的曝光时间、增益、级数等附加在单帧图像里,本文是附加在每一帧图像的前两行,简称帧头。图像帧头信息添加功能本文设计中是在FPGA内完成的,具体设计过程是:当图像经过整形,顺序进入FPGA,由于本文图像探测器的前两行原始图像是无效数据,刚好可以用来填充信息,所以在FPGA内首先开辟一小块区域,本文是一个10*10 bits的FIFO,将图像进行缓存,当发现图像第一个行有效信号的上升沿到来时,将需要添加的帧头信息逐一开始加载,同时生成行有效信号,同样的方法添加第二行帧头信息,当两行的帧头数据加载完毕后,再将有效的图像数据按照图像探测器的输出格式紧跟在帧头信息的后面,从而完成帧头数据的添加。

3 成像试验

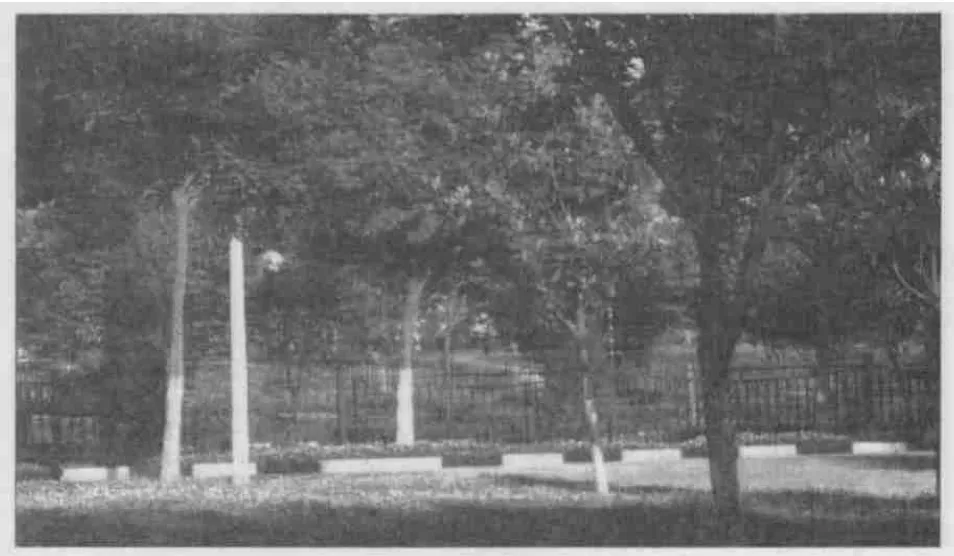

按照本文关键技术设计的思路对系统进行了详细设计,整个系统以一片FPGA为核心进行展开,采用Verilog HDL硬件描述语言以“自顶向下”的方式,并结合状态机、流水线等技术对系统功能进行了设计。实验表明,系统工作正常稳定,结合光机系统进行了实际成像试验,设置为全帧模式,在曝光时间为20 ms、帧频为20 f·s-1时拍摄得到的外景图像如图4所示。

从图4可以看出,得到的实时图像完整、清晰,充分证明了设计的可行性。由于添加了两行帧头信息,而它和整幅图像的数据没有联系,所以反映到图像里是最上面两行不规律变化的线。

图4 实际拍摄的外景图像

4 结束语

本文提出了一种以FPGA为核心器件的CMOS图像探测器一体化实时图像采集系统,该系统不仅能为探测器提供时序,而且增加了基于4片SDRAM的图像数据整形功能和图像帧头信息添加功能,满足了用户对图像准确性和实时性的要求,目前,该系统已经应用于工程,取得了不错的效果。值得注意的是,本文设计虽然是基于DALSA公司图像探测器开发的系统,但是分析不难发现,该设计只要根据实际应用稍加修改就能适应任何一款同时输出两路数据的CCD/CMOS图像探测器采集系统,具有良好的通用性。

[1]余辉龙.CMOS一体化相机关键技术研究[D].中国科学院长春光学精密机械与物理研究所,2010.

[2]林 凡,吴孙桃,郭东辉.CMOS图像传感器技术及其研究进展[J].半导体技术,2006,26(12):40-44.

[3]徐大成,翁桂荣.线阵CCD数据的高速采集系统[J].传感器技术,2002(9):25-28.

[4]刘 爽,赵凯生,龙再川,等.基于ARM和FPGA的嵌入式CCD采集系统[J].光电子·激光,2007,18(11):1296-1298.

[5]魏常伟,袁纵横,张文涛,等.基于FPGA的新型高速CCD图像数据采集系统[J].测控技术与仪器仪表,2010(4):77-80.

[6]杨健鸷,刘 霖.基于FPGA的面阵CCD图像采集系统[J].电子器件,2013,36(1):49-53.

[7]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003:87-176.

[8]李 华.基于SDRAM的Bayer格式图像插值算法硬件设计[J].电视技术,2013,37(5):49-51.

[9]EDS5116ABTA-75 Datasheet[R].Elpida Memory,Inc,2002.