基于NIOSⅡ便携式信号发生器设计

王学力,任全会

(郑州铁路职业技术学院电气工程系,郑州450052)

基于NIOSⅡ便携式信号发生器设计

王学力*,任全会

(郑州铁路职业技术学院电气工程系,郑州450052)

设计了一种基于SOPC技术便携式信号发生器。该系统利用DDS的理论,以NIOSⅡ嵌入式微处理器为核心的SOPC系统作为信号发生器的信号处理和控制的核心。测试结果表明此信号发生器能输出标准的正弦波、三角波、方波和锯齿波,不但波形的频率和幅度可调,而且根据实际需要可现场编程。此系统具有携带方便、输出频率稳定、波形标准、控制灵活和输出频率范围宽的优点。

SOPC;信号发生器;NIOSⅡ;DDS

信号发生器是电路测试和设备检测过程中不可缺少的电子仪器,在通信、测量、教学、科研等领域有着广泛的应用。传统的信号发生器大多都是台式机,而且大部分都是采用专用芯片或单片机作为控制核心,具有携带不方便、成本高、控制方式不灵活、不便于升级的缺点[1]。本系统采用DDS(直接数字频率合成)技术通过SOPC系统在一个FPGA芯片上实现了一种频率可调的信号发生器,能输出标准的正弦波、三角波、方波和锯齿波。具有携带方便、成本低、性能稳定、系统灵活、精度高、便于升级的优点。

1 DDS原理

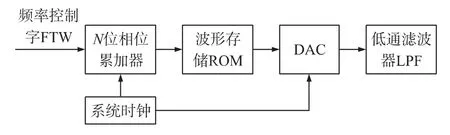

DDS(直接数字频率合成)技术就是利用累加器原理直接合成所需要的波形,DDS模型主要包括相位累加器、波形存储器、DAC和低通滤波器组成等4部分,DDS电路的数字部分主要由相位累加器,波形存储器ROM查表完成[2]。DDS的原理框图如图1所示。

图1 DDS原理框图

系统时钟是一个稳定的晶体振荡器,用它来同步合成器的各组成部分。相位累加器在每一个系统时钟输入的时候,相位增量就累加一次,相位增量由频率控制字(FTW)决定。如果计数大于N,就会自动溢出,此时把后面的N位数字保留在累加器中。相位累加器输出的相位值到正弦幅度值的转换由正弦查询表实现。正弦幅度值的数字量通过DAC转换为模拟量,最后滤波器进一步平滑近似正弦波的锯齿阶梯,从而得到一个很纯净的正弦波信号[3]。

输出波形的周期T0和频率f0分别为:

其中Ts是系统时钟周期,fs是系统时钟频率,Pftw是频率控制字的值[4]。

频率合成器的分辨率通常用频率增量表示,由式(2)可得到DDS的分辨率:

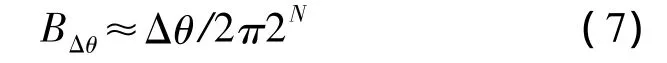

最低的合成频率就是这个增量,奈奎斯持抽样定理限制了最高的基波合成频率(至少每周抽样两次才能重构模型)所以有:

在实际的应用当中,最大的输出频率是系统时钟频率的40%。信号发生器采用DDS技术很容易实现[5]。

2 系统硬件设计

2.1 系统整体硬件设计

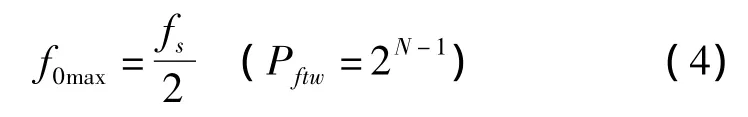

本设计是基于NIOSⅡ系统实现的。整体框图如图2所示,包括:时钟电路、AD电路、在FPGA上实现的NIOSⅡ系统、FLASH芯片、SDRAM芯片、EPCS16、键盘。FPGA选用Altera公司的cycloneⅣGX型FPGA。系统的控制和数据处理由NIOSⅡ系统完成,所得数据通过D/A转换和滤波送入示波器或者PC机进行显示。使用SOPC Builder开发平台完成NIOSⅡ系统的定制[6]。

图2 系统总体框图

2.2 DDS模块设计

DDS模块用软件实现,以正弦波为例,输出波形Sout为:

式(5)中时间t是连续的,用系统时钟对t进行抽样,设正弦波的相位θ=2πfoutt0,此时在一个时钟周期内θ的变化量是:

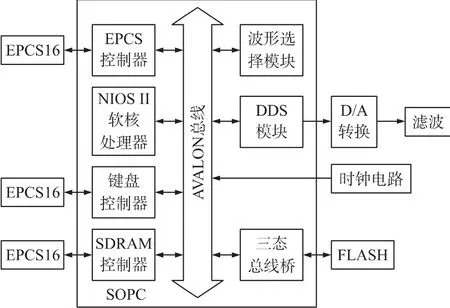

把一个周期切割成2N份,每个时钟周期相位增量的可用量化值BΔθ为:

正弦波的当前相位值可以通过相位的量化值进行累加运算得到。累加的相位增量量化值决定了信号的输出频率。

使用DDS实现三角波、方波和锯齿波就更容易了,只需改变相位增量的“0”,“1”值就能得到相应的方波、三角波和锯齿波[7]。

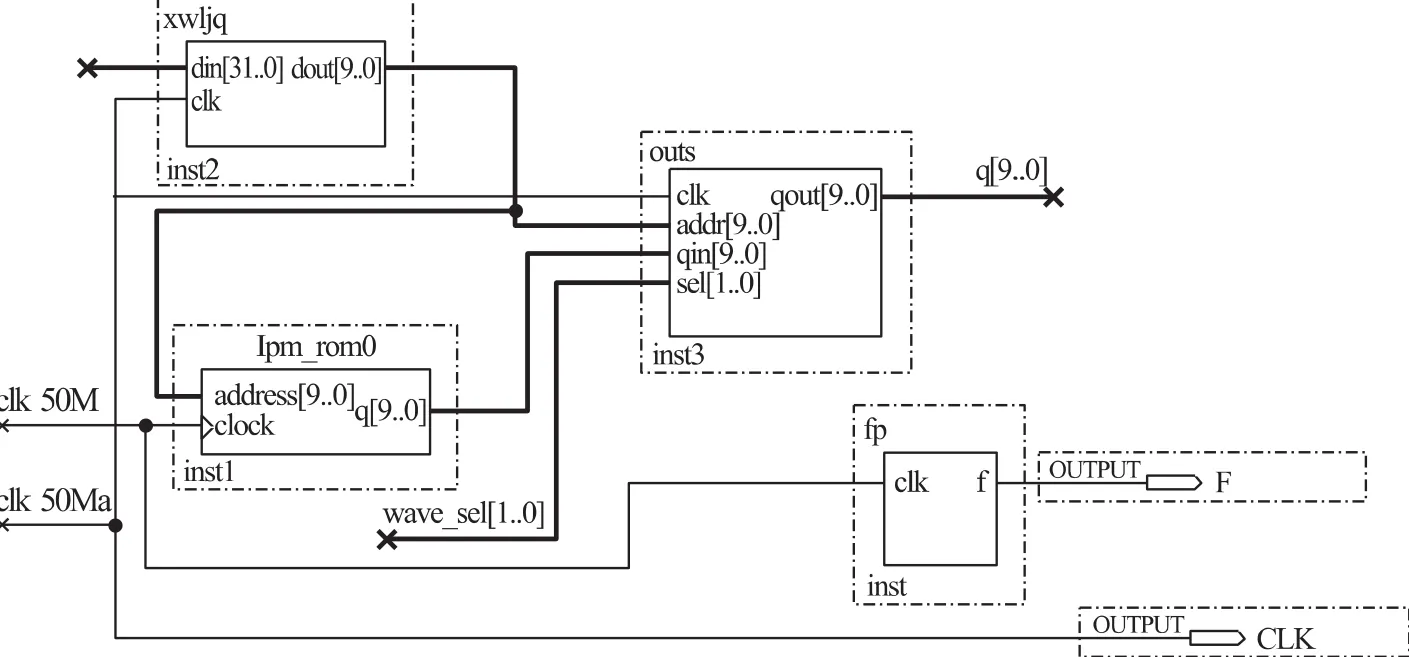

该模块使用Verilog HDL语言直接编程,能完成频率控制字的相位累加器和截断输出,这样就能实现波形数据的输出和频率调制,是系统的核心模块。其顶层设计图如图3所示。

图3 DDS模块顶层设计图

系统时钟取样的32 bit相位寄存器和32 bit二进制加法器组成了子模块“xwljq”是32 bit相位累加器。改变时钟脉冲可以改变频率控制字,也就是能输出频率。子模块“lom_room0”通过QuartusⅡ定制而成的正弦查询表,通过Matlab软件生成正弦数据,这些数据以mif的格式存储,并将这些数据加载到lom_room0模块中。输入为10 bit地址,通过系统时钟可以输出存储的正弦数据。“outs”子模块是波形输出模块,sel是波形选择端,选择端分别是0、1、2、3的时候,通过时钟就能分别输出正弦波、三角波、方波和锯齿波。本设计使用D/A转换是8 bit,输出端qout只需要接前8 bit即可。

2.3 滤波电路设计

本设计中最大频率为100 kHz,滤波器类型的选择由输出频率决定。图4(a)是低通滤波电路,FPGA通过控制继电器SW01来选择不同的截止频率。低通滤波电路在输出频率低于1 kHz时使用,假设C21=C22,可以得出C21=C22=1/(2πR22fs)≈0.048μF,取C21=C22标称值为0.047μF,可以计算出截止频率把低通滤波电路和高通滤波电路级联[8],选择电容为:C21=C22=470 pF,C23=C24=0.047μF。

图4 滤波电路

3 误差分析

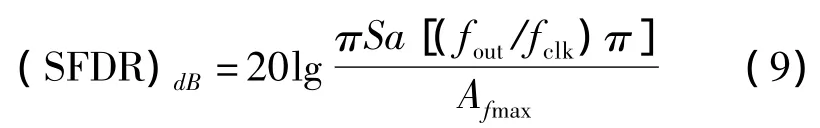

系统频率分辨率达到0.015 Hz,硬件设计采用了50 MHz晶振。为了得到较高的频率分辨率,在DDS设计中 N的取值需要比较大(本系系统取32)。只用高A位寻址能大大节省FPGA内部资,此时因为舍去低位B位就会产生相位截断误差。DDS的杂乱动态范围可以表示为:

其中

式(11)中Sa(x)表示为Sa(x)=sin(x)/x,变量x最接近x的取整运算用int(x)表示,变量x,y的最小值用min(x,y)表示。<x>y=x-int(x/y)×y,B=N-A。由式(9)可以算出(SFDR)dB≥6.02(N-B)。N和B分别取值为32和22,就能算出无杂乱动态范围大于60.2 dB。DAC908、OPA2300和OPA51技术指标的误差分别为0.05%、0.1%和0.1%,所以系统的最大幅度误差可以计算出来:(0.052+0.12+0.12)1/2=0.15(%)。D/A转换芯片和运放性能的好坏决定系统的误差的大小[9]。

4 测试结果和结论

4.1 测试结果

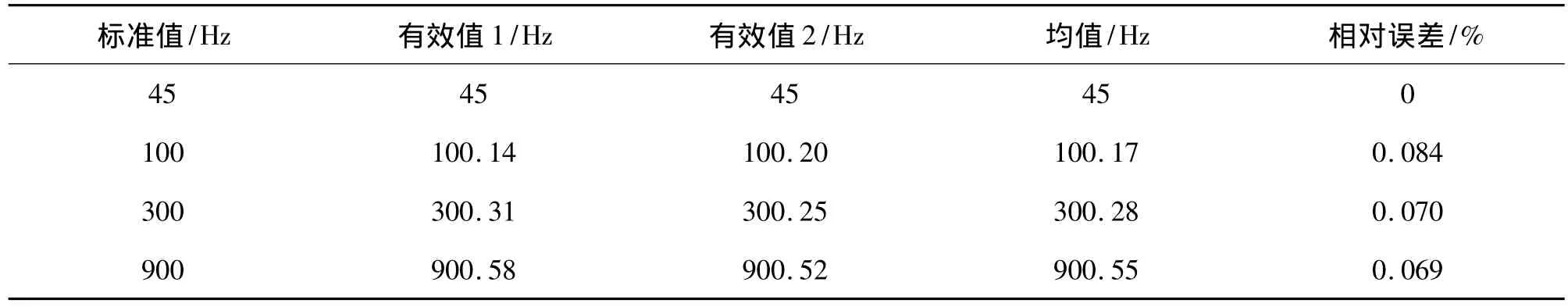

使用示波器测试结果如下图5所示。

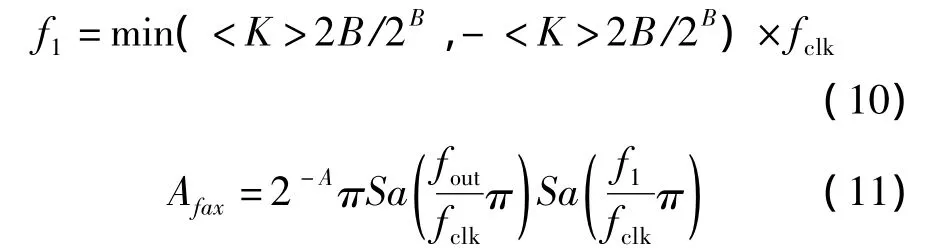

使用测量范围为0.1 Hz~100 MHz,分辨率为0.001 Hz高精度频率计对波形频率进行检测,以正弦波为例测量结果如表1所示。使用万能表来对其幅值进行性能测试,测试结果如表2所示。测试结果表明,信号发生器波形质量和幅值等各项指标都在理论误差范围之内。

图5 示波器测试结果

表1 频率性能测试

表2 幅值性能测试

4.2 结论

本系统通过使用基于NIOSⅡ的嵌入式处理SOPC技术不但减小了系统的PCB面积(降低系统的功耗,使系统体积大大减小,携带方便),外围硬件电路的复杂性也大大降低,这样电路结构更加简洁,而且系统波形显示清晰、工作稳定。该系统可由于FPGA具有可编程特性,改变控制方式或更换波形数据都非常方便,易于系统升级,有很高的性价比和市场应用空间。

[1]陈亚军,陈隆道.基于Verilog HDL的信号发生器的设计[J].电子器件,2011,34(5):525-528.

[2]邓腾,吴校生,周晓玲,等.基于DSP和DDS技术相位及频率严格可调的多路同步信号发生器[J].电子器件,2012,35(2): 163-167.

[3]常高嘉,冯全源.基于FPGA的高速数据采集系统的设计与实现[J].电子器件,2012.22(6):217-220.

[4]郭伟然,刘耀,汤勇明.基FPGA的频率特性测试仪的设计[J].南京:电子器件,2011,34(6):713-717.

[5]杨春玲,彭立章.基NIOS边界扫描测试平台的开发[J].电子器件,2007,30(6):2129-2132.

[6]冯伟昌,林玉池,何冬.基于FPGA的双通道实时图像处理系统[J].传感技术学报,2010,23(8):1118-1122.

[7]王丹,李平,文玉梅,等.采用DDS频率合成的虚拟信号发生器研究[J].传感技术学报,2007,20(3):586-591.

[8]杜斌峰,王智敏,孙跃.基于FPGA的数字混沌序列的实现及性能分析[J].电子器件,2011,34(4):477-485.

[9]王力,张雄.小波滤波与AR模型在脑电信号处理的应用[J].电子器件,2012,35(4):461-464.

Design of Portable Signal Generator Based on NIOSⅡ

WANG Xueli*,REN Quanhui

(Department of Electrical Engineering,Zhengzhou Railway Vocational and Technical College,Zhengzhou450052,China)

A portable signal generator is designed on the basis of SOPC technology.The system uses the theory of the DDS,taking the SOPC technology based on embedded processor of NIOSⅡas the core of signal generator for signal processing and control.The test results show that this signal generator can output sine waveforms,triangle waveforms,square waveforms and sawtooth waveforms.Itswave form frequency and amplitude are adjustable,and the system can be field programmable according to the actual needs.The system has advantages such as easy to carry,stable output frequency,standard waveforms,easy control and wide bandwidth.

SOPC;signal generator;NIOSⅡ;DDS

10.3969/j.issn.1005-9490.2013.04.011

TH741 文献标识码:A 文章编号:1005-9490(2013)04-0478-04

2012-12-25修改日期:2013-01-29

EEACC:1230

王学力(1963-),男,汉,河南信阳人,郑州铁路职业技术学院,讲师,硕士,研究方向为ARM、通信技术及电子技术研究,wangxueli1963@163.com。