一种无片外电容LDO的瞬态增强电路设计

王 常,吴 震,邓朝勇

(贵州大学 理学院 贵州省微纳电子与软件技术重点实验室,贵州 贵阳 550025)

近年来,随着信息产业的巨大发展,人们对便携式电子产品需求量日益增加。而低压差稳压器(Low-Dropout Regulator,LDO)以其低噪声、低纹波、体积小、应用简单等优点被广泛应用于电池供电系统的便携式电子设备上。随着SoC(片上系统)的发展,要求尽可能地减少外围电路,越来越多的模块被纳入芯片内部。因而对LDO而言,无片1外电容LDO就成为LDO发展的新趋势。

介于无片外LDO缺少输出大电容,使得负载的阶跃变化需要靠调整管来快速响应。但调整管的栅电容通常很大,这会导致环路的压摆率(slew rate,SR)不够,因此无片外电容LDO的瞬态特性比较差。

针对无片外电容LDO的瞬态特性,常用的解决办法是缩短调整管栅电容的充放电时间。由于调整管栅电容的充放电时间与电流成反比,与其电容成正比。因此减小栅电容的充放电时间的途径有:增大调整管栅极的驱动电流,或者减小调整管栅极的等效阻抗或等效电容。本文采用的是增加调整管栅电容的充放电流,来增强瞬态响应。

近些年,为了提高LDO瞬态响应特性,众多设计者采用增加调整管栅极驱动电流的方法[1-4]。在保证系统其它性能不受影响的前提下,为了得到快速响应,本文基于Lee提出的摆率增强电路(SRE)思想[5],结合RC电路的瞬态特性,提出了一种无片外电容LDO的瞬态增强电路。

1 使用摆率增强(SRE)技术的瞬态增强电路设计

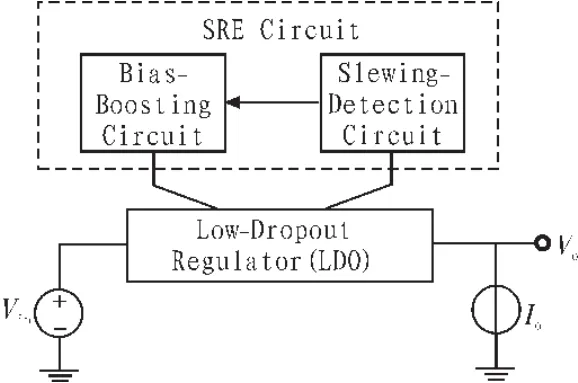

摆率增强技术是目前提高无片外电容LDO瞬态性能的重要技术。图1为SRE技术的系统模型[6-7]。该电路主要有两个部分组成:LDO主干电路和SRE电路。首先在LDO中找到一个能快速响应负载电流和输入电压变化的节点,将该变化信号传递给SRE电路,然后SRE电路在LDO调整管的栅极产生一个额外的充放电流,从而使栅极电位快速变化,达到输出端快速稳压的目的。

图1 采用偏置电流增强技术的LDO框图Fig.1 Diagram of LDO with the proposed dynamic bias-current boosting technique

1.1 LDO的瞬态检测电路

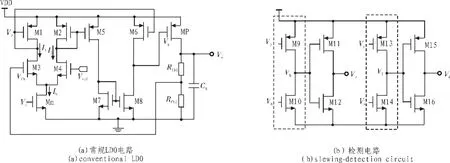

本设计为了降低功耗,采用工作在亚阈值区的跨导放大器作为LDO的误差放大器。图2(a)为一个简单的LDO电路图。

图 2(b)为 LDO的瞬态检测电路[8],图中 Vp和 Vn与图 2(a)相对应,为检测节点的电压,其中虚线部分为信号检测电路,另外两条支路分别为一级放大器。

在检测电路中,我们通过调节PMOS和NMOS晶体管的宽长比,来使得和在稳定状态下,通常分别被偏置在接近电源电压和接地电压。Vu和Vd为检测电路的输出端,同时也是偏置电路的输入端口。

为了给偏置增强电路提供快速和摆幅较大的触发信号。在检测电路的输出端加入了一个轨到轨的放大器,在这里采用反相器来实现,如图2(b)所示。它可以有效地将缓慢变化的检测信号转化为快速的轨到轨信号。当Vfb正向突变时,Vg增加,同时Vn增加,而在Mn上形成一个较大的栅源电压Vgs,从而为PMOS调整管提高一个大的充电电流。而且Vh和Vl均增加。Vh更加靠近电源电压,而Vl开始从一个小电压开始增加,使其达到了反相器CMOS的阈值电压,因而在Vd产生了从电源电压到地电压的摆幅范围。同样,当Vfb负相变化时,会使Vp增加,从而导致Vh和Vl均下降,而且反相器会使Vh变化范围转化为从电源电压到地电压的变化范围,实现轨到轨的目的。仿真结果如图3所示。

图2 带瞬态检测电路的LDO Fig.2 Diagram of LDO with the transient slewing-detection circuit

图3 电路内部信号随Vfb变化曲线Fig.3 Internal signals of the cricuit during the slewing of Vfb

1.2 偏置电流增强电路

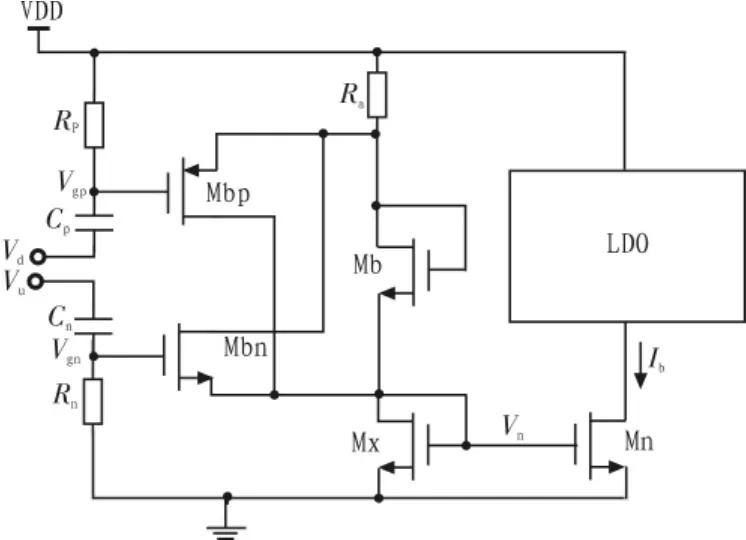

检测电路将检测信号传递给偏置电路,偏置电流增强电路产生一个瞬间的大偏置电流,进而给调整管的栅电容充电。

本电路主要是利用RC电路在输入电压发生变化时,电容不能瞬间突变的原理,为输出端提供一个瞬时尖峰脉冲。

利用RC电路产生的脉冲使MOS管导通,电路图如图4所示。在信号发生突变时,为了使偏置电流Ib能随之变化,本电路采用了上一节的轨到轨的思想,使得Vgn和Vgp是在VDD到地之间的满摆幅。为了避免MOS进入截止区,本设计采用Mbn和Mbp2个MOS管并联,如下图所示,保证了信号的变化过程中,至少有一个的MOS管导通。从而使得Mx的漏源电流瞬间增大,Vn增加,进而Ib随之增大。

图4 偏置电流增强电路Fig.4 Bias-current boosting circuit

上图中,Vu和Vd作为偏置电路的输入端口,且是检测电路的2个输出端。Mb是以二极管形式连接的MOS管,在这里起提供一个大电阻Rb的作用,Mbn和Mbp与Mb并联,Mx和Mn为一个电流镜。

稳态下,Vu和Vd均保持不变,此时电容并不导通,所以Vgn和Vgp分别置地和电源电压。2个MOS管均截止,偏置电路由于Mb产生的大电阻Rb,使得偏置电流保持很小,Ib约为40 nA。当脉冲出现后,会在Vgn和Vgp处产生一个瞬时尖峰电压,达到MOS管的阈值电压,使其导通,而导通的Mbn和Mbp的电阻比并联的Mb的电阻小得多,此时偏置电路的电阻急剧减小,因而在Mx处产生一个瞬时大漏电流,从而在Mn处镜像出一个大的瞬时偏置电流Ib。

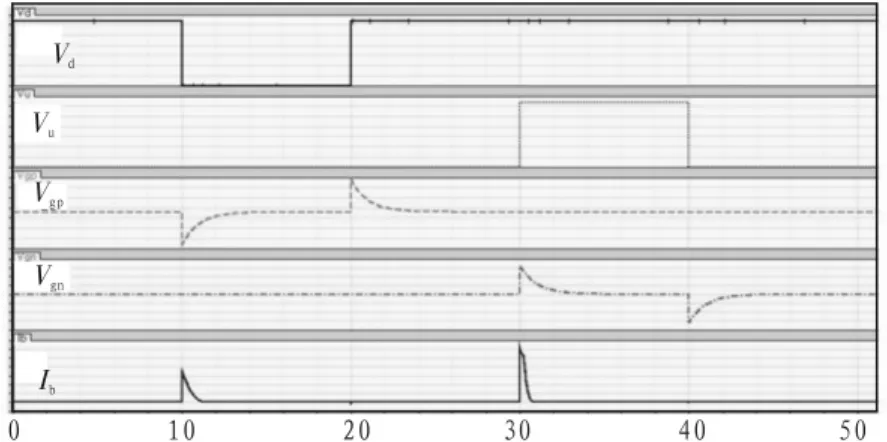

由于RC电路瞬态特性,Vgn和Vgp是以正负脉冲的形式传递过来的,所以偏置电路只是产生一个瞬时的大电流Ib,然后镜像给LDO,给调整管的栅电容进行充放电,使得栅电压快速响应。当栅电容充放电完成后,Vgn和Vgp又迅速恢复到原来的稳态,分别偏置到接地电压和VDD,2个MOS管又重新截止,偏置电流又恢复到原来的低电流状态[9]。如图5所示。

该电路设计在稳定的状态下,静态电流保持在较低的水平;突变状态下,在提高了系统响应速度的同时,静态电流只是瞬间增大,随后立即减小为初始值,因而对系统的功耗并没有产生很大影响。

图5 偏置电路内部信号随 Vu和Vd变化曲线Fig.5 Internal signals of the cricuit during the slewing of Vuand Vd

2 采用瞬态增强电路的无片外电容LDO的电路实现

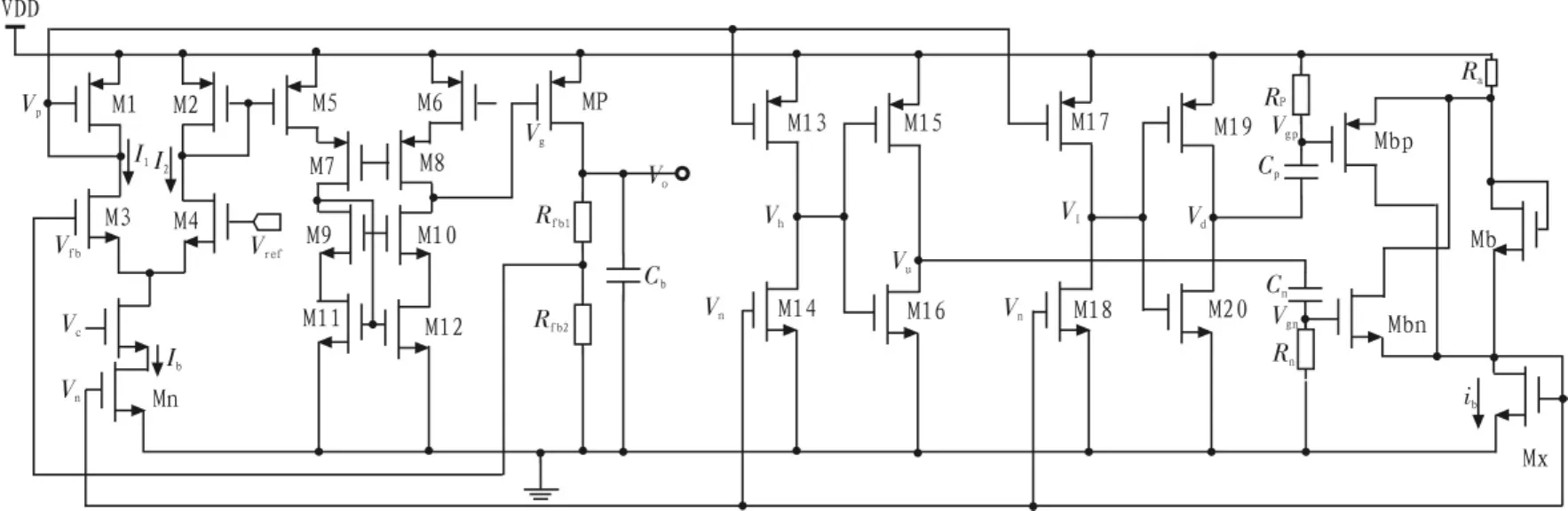

本电路设计主要包括检测电路、偏置电流增强电路、以及LDO主电路。其电路图如图6所示。

图6 带有检测电路和偏置增强电路的LDO的实现电路Fig.6 Circuit implementation of the LDO with the slewing-detection circuit and the dynamic bias-current boosting circuit

当负载电流正向变化时,Vfb减小,在上面的电路图中体现为Vp增大,由于电流镜作用,使得本身为低电位Vl的继续降低,通过反相器后,Vd保持为高电位不变;而Vh由高电位开始减小,在反相器的作用下,Vu由低电位开始增加。因而Vgn产生了一个瞬间的正向电压脉冲,使得Mbn瞬间导通,从而偏置电流极大增加。使得流过Mx的漏电流增大,Mx的栅电压增大,则Vn增大,同时流过Mn的漏电流Ib增大。当负载电流负向变化时,同理使得Mbp导通,为LDO电路提供瞬间大电流。本设计的偏置电流在激励信号的作用下为17.5 μA,在稳态时为40 nA。

3 电路的仿真结果

电路基于SMIC的0.18 μm工艺进行仿真。由于稳态下偏置电流设计的比较低,Ib=40 nA,所以整个系统的静态电流只有 3.2 μA。

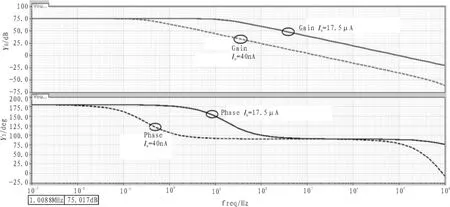

如图7所示,图中虚线表示的偏置电流为40 nA的频率响应,实线为偏置电流为17.5 μA的频率响应。当系统处在稳定状态时,偏置电流为40 nA,其相位裕度为90.19°。当遇到激励信号时,瞬时偏置电流为17.5 μA,其相位裕度为91.35°。所以系统在瞬态响应时,没有降低系统的稳定性。

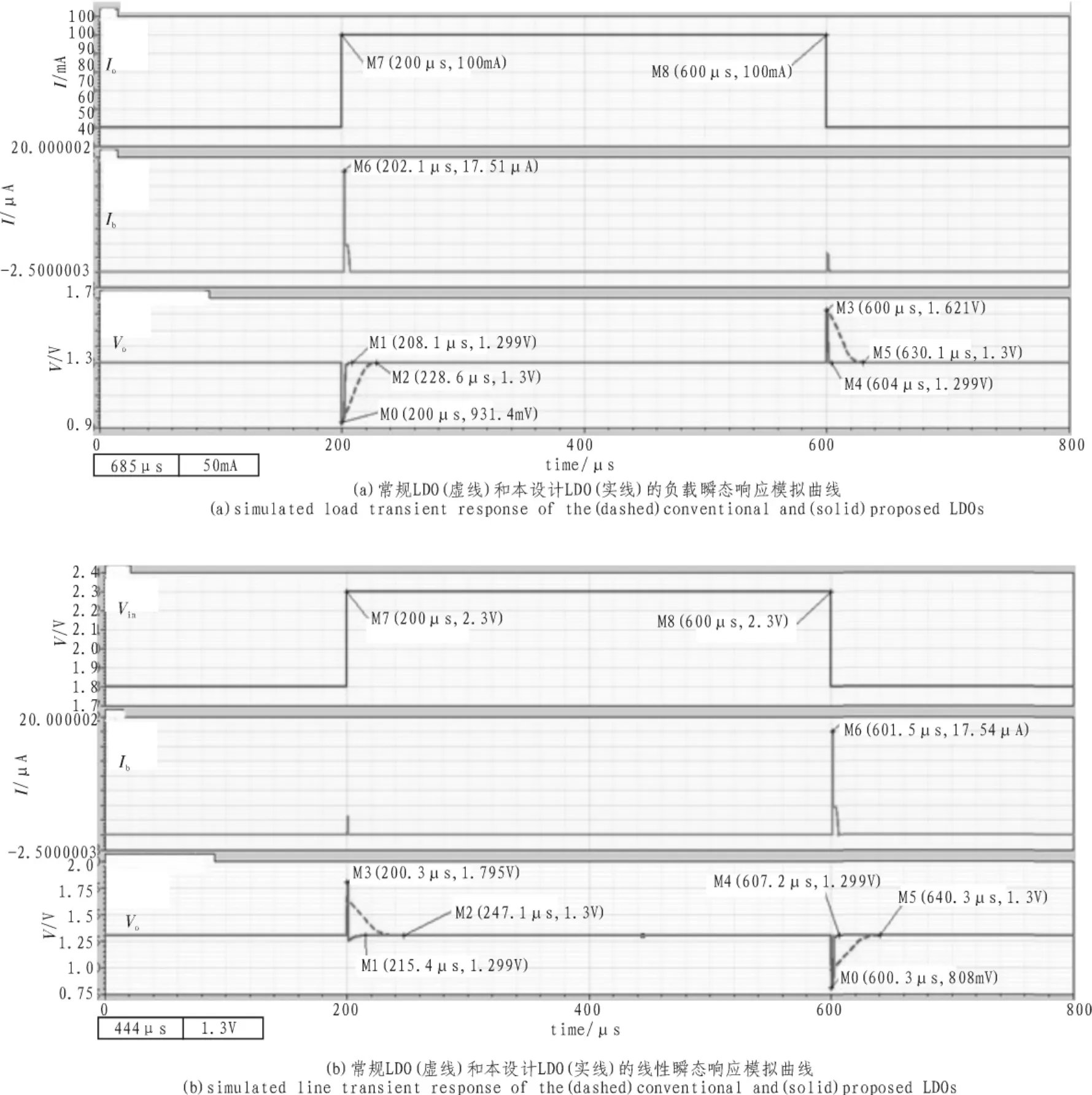

为了得到瞬态响应的结果,我们通过对本设计电路与没有采用偏置增强电路的LDO进行负载瞬态响应与线性瞬态响应的仿真。两组LDO的仿真条件一样。

对负载响应进行仿真时,电源电压为1.8 V,输出电压为1.3 V。负载电流在10 ns内从50 mA增加到100 mA,经过400 μs后,又变回到 50 mA,如图 8(a)所示。可以看出在负载电流发生跳变的两个时刻,偏置电流Ib都发生了明显的瞬时增大。响应时间分别为8 μs和4 μs远小于传统没加偏置增强电路的LDO的响应时间28 μs和30 μs,很大程度上提高了系统的负载响应性能。对线性响应进行仿真,在保证输出电压为1.3 V,负载电流为100 mA的前提下,电源电压在10 ns的时间内从1.8 V增加到2.3 V,经过400 μs后,又变回到1.8 V,如图8(b)所示。同样可以看到在电源电压发生跳变的过程中,偏置电流出现了瞬间增大。结果显示本设计的线性响应时间分别从 47 μs和 40 μs提高到 15 μs和 7 μs, 比传统LDO瞬态响应性能提高了很多。

图7 LDO环路增益的幅频和相频曲线(Ib=40 nA,Ib=17.5 μA)Fig.7 Magnitude and phase response of LDO loop gain (Ib=40 nA, Ib=17.5 μA)

图8 常规LDO和本设计LDO瞬态响应特性模拟曲线Fig.8 Simulated transient response of the conventional and proposed LDOs

4 结 论

文中针对一款低功耗的无片外电容的LDO,利用偏置电流增强技术,设计出了一个瞬态响应增强电路。基于SMIC的0.18 μm CMOS工艺,使用Spectre仿真工具,对电路仿真验证表明,负载瞬态响应时间由原来的28 μs提高到8 μs,线性瞬态响应时间从47 μs减小到15 μs。在不影响整个系统功耗的前提下,有效地提高了LDO的瞬态响应性能。而且整个电路的相位裕度保持在90.19°以上,保证了电路响应过程中系统的稳定性。

[1]Jaime R A.A novel slew-rate enhancement technique for one stage operational amplifers[C]//Midwest Symposium.Circuits and Systems,Ames,IA,1996:11-13.

[2]Yoon K S.A CMOS digitally programmable slew-rate operational amplifer[J].IEEE Transactions on Circuits Systems II,Analog and Digital Signal Processing,1995,42(11):738-741.

[3]Klinke R,Hosticka B J,Pfleiderer H J.A very-high-slew-rate CMOS operational amplifer[J].IEEE Journal of Solid-State Circuits,1989,24(6):744-746.

[4]Nagaraj K.CMOS amplifers incorporating a novel slew rate enhancement circuit[C]//Custom Integrated Circuits Conference,1990:1161-1165.

[5]Hoi Lee,P K T,Leung K N.Design of low-power analog drivers based on slew-rate enhancement circuits for CMOS low-dropout regulators[J].IEEE Transactions on Circuits and Systems II, Express Briefs, 2005, 52(9):755-759.

[6]G A, Rincón-Mora.Current-effcient low-voltage low dropout regulators[D].Atlanta:Georgia Institute of Technology,1996.

[7]Hoi Lee,Mok P K T.A CMOS current-mirror amplifer with compact slew rate enhancement circuit for large capacitive load applications[C]//International Symposium.Circuits and Systems,2001:220-223.

[8]崔岩.采用T型电路参数法对现场电流互感器测量的研究[J].陕西电力,2011(9):63-66.CUI Yan.Probe into the T-circuit parameter method for field CTs measurement[J].Shaanxi Electric Power,2011(9):63-66.

[9]李军浩,胡泉伟,吴磊,等.极化/去极化电流测试技术的仿真研究[J].陕西电力,2011(4):1-5.

LI Jun-hao,HU Quan-wei,WU Lei,et al.Simulation study of polarization and depolarization current measurements technology[J].Shaanxi Electric Power,2011(4):1-5.