基于PLL的频率合成器的设计

刘 倩

(滁州职业技术学院,安徽 滁州 239000)

一、引言

频率合成器是将一个高准确度和高稳定的标准参考频率源[1],经过混频、倍频和分频等对它进行加、减、乘、除四则运算来最终产生大量的具有同样精确度和稳定度的频率源,频率合成器已经在电子等多领域得到广泛的使用,尤其在雷达、电子对抗、通信、测量、仪器仪表等领域的应用非常广泛。由于我国通信业快速发展,移动通信IC芯片需求发展很快。国内市场对频率合成器的需求很大,开发锁相式频率合成器具有积极的意义。

二、频率合成器技术与锁相环原理

(一)频率合成的基本方法

频率合成的基本方法有以下三种[9]:

1、直接频率合成(DS):直接频率合成是最早的频率合成方法。将滤波器调谐到所需输出的频率上就可以得到需要的频率。这种方法要求选择性很高的滤波器。

2、锁相频率合成(IS):直接频率合成所固有的缺点,在应用锁相环路(PLL)的频率合成(常称为间接合成)中就大大减少了。

3、直接数字频率合成(DDS):直接数字频率合成器的体积小、功率低,并且能以实际上是即时的、相位连续的频率变换,给出非常高的频率分辨力。

(二)频率合成的主要性能指标[10]

频率合成器的性能需一系列指标来表征。但不同用途的合成器,其性能差异很大,这里仅介绍一些必可少的基本指标:频率范围、频率分辨力、频率转换时间、频率准确度、稳定度、频谱纯度。

(三)锁相环基本原理

锁相环(PLL)是一个相位跟踪系统。它包括三个基本部件:鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)。在锁相环的反馈支路中,插入一个分频器就可构成一个最基本的单环锁相频率合成器。基本的锁相环由下列各部分组成:

1、鉴相器

鉴相器(PD)又称相位比较器,它是用来比较两个输入信号之间的相位差θe(t)。鉴相器输出的误差信号P/(P+1)是相差θe(t)的函数,即

2、环路滤波器ud(t)

在锁相环路中,环路滤波器起着至关重要的作用,它可以滤除误差电压或电流中的高频分量和噪声,将误差电流分量转化为误差电压分量,以保证环路所需要的性能,增加环路稳定性。

3、压控振荡器

压控振荡器就是震荡电路中采用压控元件作为频率控制器件,是一种电压一频率转换器。压控振荡器的技术指标:中心频率、频偏范围、压控线性度、频率稳定度及相位噪声。

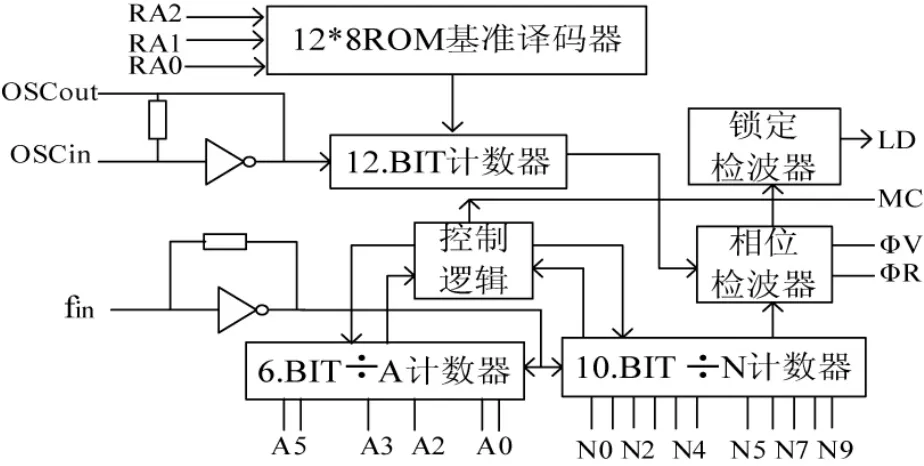

(三)MC145152-2 芯片的简介

MC145152-2的工作原理:参考振荡器信号经R分频器分频后形成fR信号。压控振荡器信号经双模(P/(P+1))分频器分频,再经A、N计数器分频器后形成fV信号,fV=fVCO/(NP+A)。fR信号和fV信号在鉴相器中鉴相,输出的误差信号(ΦR、ΦV)经低通滤波器形成直流信号,直流信号再去控制压控振荡器的频率。

图1 MC145152-2的原理框图

当整个环路锁定后,fV=fR且同相,fV=fVCO/(NP+A),fV=(NP+A)fR,便可产生和基准频率同样稳定度和准确度的任意频率。

三、振荡器实现

VCO电路图如下所示,在电路图中加入电容Cd,避免了电感对变容二极管的直流短路作用:

图2 压控振荡器

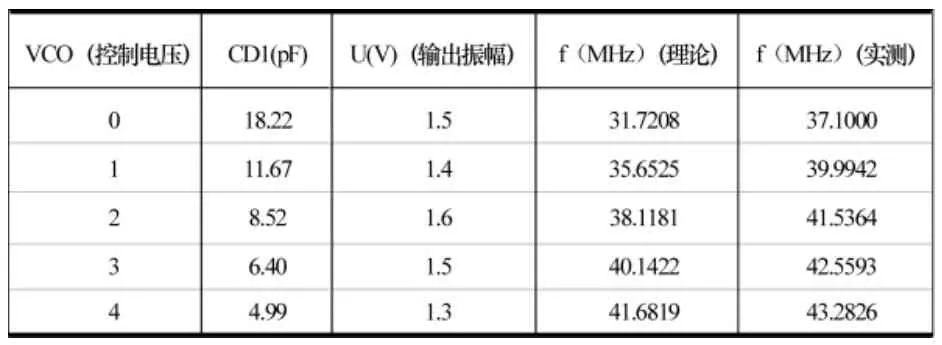

理论上计算出的VCO振荡频率值与实测值对比如下表1所示:

表1 震荡频率值

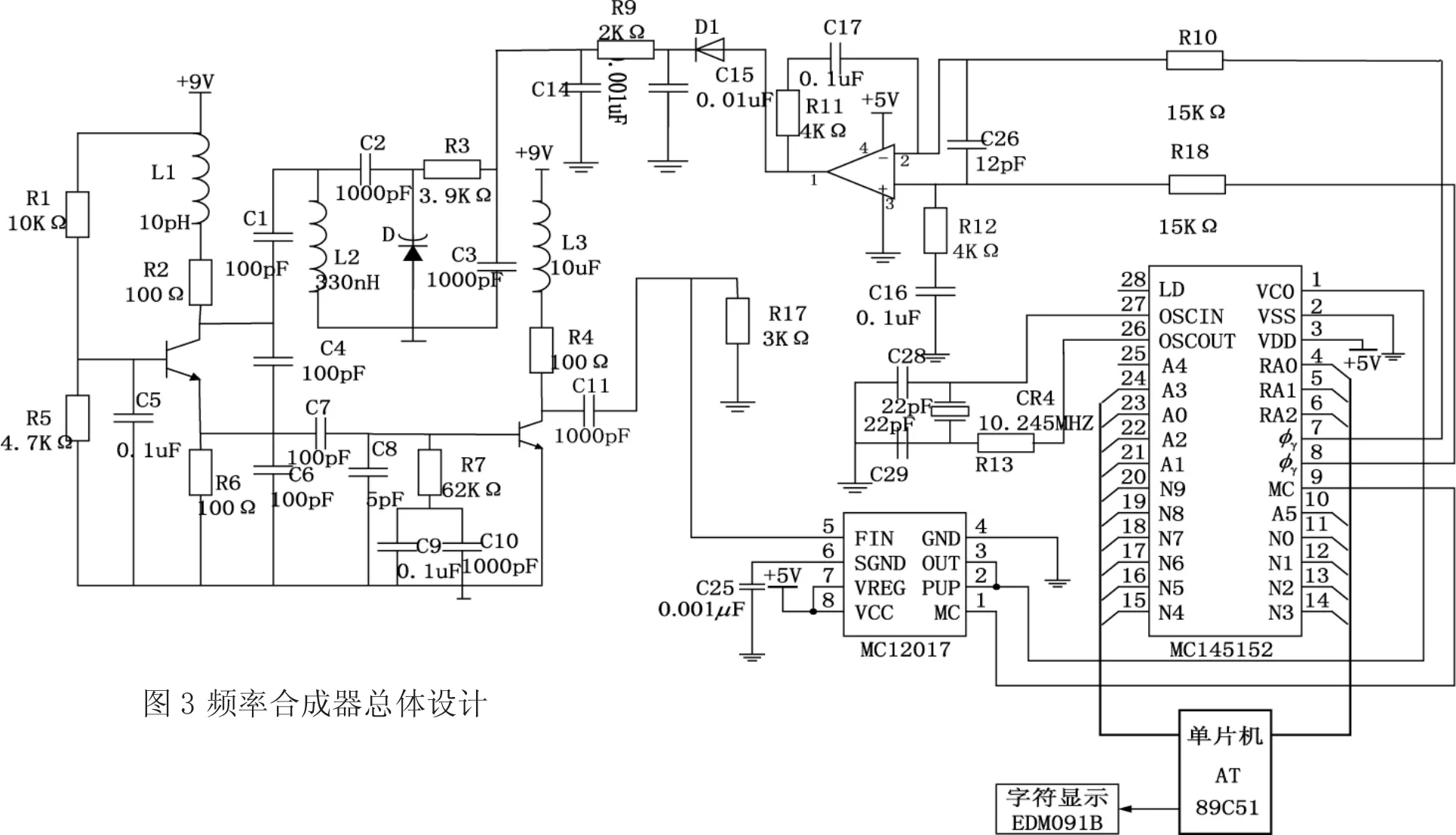

图3为一频率合成其中压控振荡器输出的频率通过双模预分频器MC12017预分频,输出到可编程行输入锁相环MC145152中单片机通过I/O口对MC145152进行编程以改变其计数器的计数初值,从而改变分频比,鉴相器双输出端输出的误差信号和输入到由LM358双端输入的有源低通滤波器,其中R10、R18、R12、C16等构成有源滤波器输入电路的RC低通环节,而R11、C17构成有源滤波器的高反馈环节。由D1和C14、R9、C15网络组成的峰值检波器将有源滤波器输出的误差电压进一步平滑后,直接对MC3363中的压控振荡器进行控制,构成了一个完整的数控锁相环。单片机接收人工调整、设置的数值,并对MC145152的计数器计数初值进行不同的预置,以锁定不同的频率,达到改变不同频点信号的目的。对应频点的信号经A/D到单片机后,再输入到字符显示器中显示信号场强。

四、结束语

图3 频率合成器总体设计

本设计主要实现了压控振荡器VCO设计了其工作电路,具有频率范围广、可程控性强、步进率小、结构简单、使用灵活方便、成本低等优点。有很强的实用性和经济性,便于集成推广;使用锁相环频率合成器专用芯片MC145152-2连接相应的前置分频,环路滤波和压控振荡电路构成一个频率合成器,使该频率合成器具有较低的相位噪声、很高的频率稳定度。

[1]王晓音,聂裕平,庞伟.正.输出频谱杂散的抑制[J].电子对抗技术,2008,(11):25-28.

[2]韩杰峰.超短波高速跳频频率合成器的设计.[D].哈尔滨:哈尔滨工程大学,2008.

[3]赵丽妍..超宽带YIG频率合成技术的研究.[D].南京:南京理工大学,2010.

[4]杨臆.现代频率合成技术的研究进展.成都:电讯技术,2007.5.

[5]杜昌源,王晓初,李克天等.面向金丝球焊线机的功率超声电源的设计[J].微计算机信息,2010,(2):157-158.

[6]王飞,马胜前.S波段锁相频率合成器的设计[J].安徽职业技术学院学报,2009,(4):16-19.

[7]罗杰汉,程光伟.基于FPGA的DDS设计[J].电子设计工程,2010,(1):66-67.

[8]万心平,张厥盛,郑继禹.锁相技术[M].西安:西安电子科技大学出版社,1993.:1-51.

[9]曾素琼.基于NE564D锁相环频率合成器的设计[J].电子质量,2010,(1):16-18.