一种基于SiP技术的加速度计有源磁悬浮控制电路

张志阳,毛寒松

(中国电子科技集团公司第43研究所,合肥 230088)

1 引言

加速度计是以加速度的观点来测量物体运动的传感器,它通过检测质量块的惯性力来测量载体的线加速度或角加速度。加速度计被广泛应用于惯性测量与惯性导航系统。其种类繁多,基本类型有闭环液浮摆式加速度计、挠性摆式加速度计、振弦式加速度计和摆式积分陀螺加速度计等。

本文介绍的有源磁悬浮控制电路应用于闭环磁悬浮摆式积分陀螺加速度计中,该加速度计是利用自转轴上具有一定摆性的双自由度陀螺仪来测量加速度的一种高精度加速度计,而且在很大的量程内能够保持较高的测量精度。

2 有源磁悬浮控制电路的工作原理

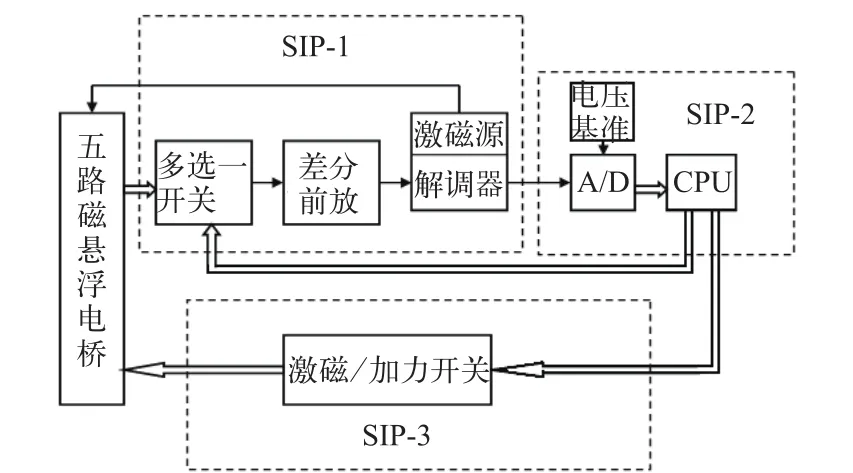

有源磁悬浮控制电路与加速度计磁悬浮元件构成闭环系统,实现磁悬浮元件的位置信号检测与加力信号控制的功能。图1是有源磁悬浮控制电路的原理示意图。有源磁悬浮控制电路主要包括4部分:浮子位置信号检测电路、时序控制开关、控制器、激磁/加力信号开关功率放大器。浮子位置信号检测电路由多选一开关、前置差分放大器及相敏解调器构成。用来测量因浮子位置变化引起磁悬浮相对磁极电感的差动电压信号变化量。微处理器实现磁悬浮元件的分时两用(即位置传感器作用和控制施力器作用),在微处理器的分时控制下,可将同一级磁悬浮线圈交替作为位置传感器和加力发生器,改变磁悬浮线圈中直流加力电流的大小,以适当的径向或轴向力,使浮子组件保持在中心位置。激磁/加力信号开关功率放大器在微处理器的分时控制下,将同一磁悬浮线圈交替作为位置传感器和加力发生器。当线圈作为位置信号传感器时,微处理器使能时序开关的激磁端,激磁电流流过惠斯通电桥,通过对电桥差动电压的采集完成对浮子位置的测量;当线圈作为加力发生器时,微处理器使能时序开关的加力端,根据控制算法来控制时序开关的开、合及持续时间,从而控制对磁悬浮元件的磁拉力,完成对浮子的定中控制。

图1 有源磁悬浮电路原理示意图

3 基于SiP技术的电路设计

3.1 SiP技术概述

随着电子技术的发展,模块化集成技术已日益成熟,作为设计过程中的系统集成技术SoC(System on Chip)和作为封装过程中的系统集成技术SiP(System in Package)已成为模块化集成的两大主流技术。SoC的设计思想是在单个芯片上实现数字电路、模拟电路、RF电路、存储器的集成;SiP的设计思想则是采用混合集成技术,将多种类型的元器件组合成一个紧凑的具有独立功能的模块。

SiP技术主要包括以下4个方面的内容:(1)系统功能模块的划分和设计;(2)实现系统集成的载体(高性能多层基板)的设计与制备;(3)组装技术;(4)封装技术。

3.2 电路的功能划分与设计

3.2.1 电路功能的划分

有源磁悬浮控制电路与加速度计磁悬浮元件构成闭环系统,应用于某整机系统中。由于整机系统能提供本电路的装配空间有限,对电路产品的体积提出了具体的要求。为了减小产品的体积,特别是减小产品的高度,以适应整机系统对产品的装配和使用要求,以及便于集成化,我们将有源磁悬浮控制电路划分成3个模块,如图1所示:(1)SiP-1电路:包括多选一开关、前置差分放大器、位置信号的相敏解调以及磁悬浮信号的激磁电源等功能电路;(2)SiP-2电路:集成了电路的微处理器芯片,以及磁悬浮信号的锁存和激磁使能信号的锁存等功能电路;(3)SiP-3电路:将系统的20路激磁/加力功率开关集成于该模块中。

3.2.2 SiP-1电路的设计

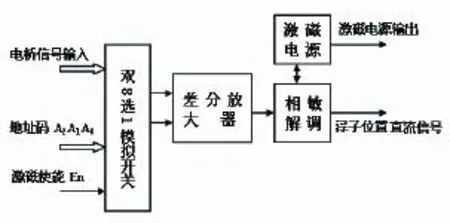

SiP-1的设计原理图如图2所示。为了提高测量精度,加速度计系统采用了5路磁悬浮惠斯通电桥的电路结构作为位置传感器和加力发生器,每路电桥输出一组电桥差动电压信号。位置信号切换开关用于对5路磁悬浮惠斯通电桥电压进行切换。5路位置信号共用一套模拟信号预处理电路,可以大大减少元器件的个数,减小SiP-1的体积。

图中的位置信号切换开关选用双8选1模拟开关ADG507,它由A、B两组8选1开关组成。本电路只使用了双8选1模拟开关的前5路,将它作为双5选1开关。每组电桥的差动输出端分别输入到双5选1开关的A通道和相应的B通道,在地址码A2A1A0的控制下,选通双5选1开关的某一组A、B通道,如A2A1A0=001时,模拟开关的A2与B2通道被选通,此时第2路电桥的2组电压信号被送入差分放大器中。差分放大器选用高精度的仪表放大器AD620,它具有电压增益可调功能。相敏解调器将差分放大器的输出信号进行解调,输出浮子位置的直流信号。

图2 SiP-1的原理框图

为了提高SiP-1电路对磁悬浮输入信号的敏感性,电路的电压增益设计在36倍以上。电路中的激磁电源是通过基准电压源实现的,以提高激磁电源的精度和稳定性,特别是温度稳定性,其输出电压的温度系数仅为±10×10-6/℃以内。

3.2.3 SiP-2电路的设计

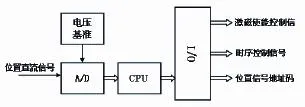

图3是SiP-2的设计原理框图。SiP-1输出的浮子位置直流信号输入到SiP-2电路中,经A/D转换器转换成数字信号。通过微处理器内算法参数的设置,SiP-2电路输出符合系统控制要求的激磁使能信号、磁悬浮位置信号地址码以及时序控制信号等。为了提高系统的控制精度,电路中采用了20位微处理器。

图3 SiP-2的原理框图

3.2.4 SiP-3电路的设计

SiP-3电路是一种多开关组件,其中含有20路电子开关。为了保证开关的电流驱动能力,20路电子开关均采用开关三极管芯片构成,每路开关的最大驱动电流可达300 mA。SiP-3中的20路电子开关在SiP-2的时序控制信号作用下,实现磁悬浮元件的分时复用,也就是将同一磁悬浮线圈交替作为位置传感器和加力发生器。

3.3 采用SiP技术的集成化设计

3.3.1 SiP的结构设计

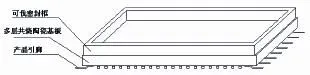

采用SiP技术实现电路的集成化。具体方式为采用多层共烧陶瓷基板实现多层布线的制作与互连,然后在多层基板的正面焊接一个密封框,在多层基板的背面焊接引线,从而形成一个SiP结构的陶瓷外壳,如图4。外贴元器件组装到一体化陶瓷外壳中,再采用平行缝焊技术实现密封。这种SiP结构不但可实现产品高度的最小化,而且可有效减小产品的底面积。

图4 电路的SiP结构

3.3.2 多层共烧基板工艺的选择

在目前市场化的SiP产品中,其高性能多层基板大部分采用LTCC(Low Temperature Co-fire Ceramic)工艺制作,因为它具有烧结温度低、介电常数小、高频损耗小、可埋置无源元件等优点。但是LTCC基板由于玻璃相含量较大(有时超过50%),其机械强度远不如HTCC基板。另外,LTCC基板的热导率仅为HTCC(High Temperature Co-fire Ceramic)的20%~25%,虽然通过设置金属散热通孔能适当提高LTCC基板的散热能力,但是金属散热通孔的数量增多,将会更加减弱其机械强度。同时,LTCC的焊接区一般采用PaAg浆料烧结而成,其耐焊性与附着力受到限制。因此,本电路采用Al2O3含量为92%~93%的黑色HTCC多层共烧基板作为SiP结构的载体。

3.3.3 HTCC多层基板的设计

(1)设计原则

HTCC的设计原则:避免直通孔,顶层过孔离密封框内侧边缘的距离不小于0.5 mm,内层的布线区及网格地层离HTCC陶瓷板边缘的距离不小于0.7 mm。最小线条宽度为0.15 mm,最小线条边缘间距为0.2 mm,线条边缘与过孔边缘的最小间距为0.2 mm,密封框的壁厚为0.6 mm,密封框焊接区的宽度为0.8 mm~1.0 mm。

(2)分层版图

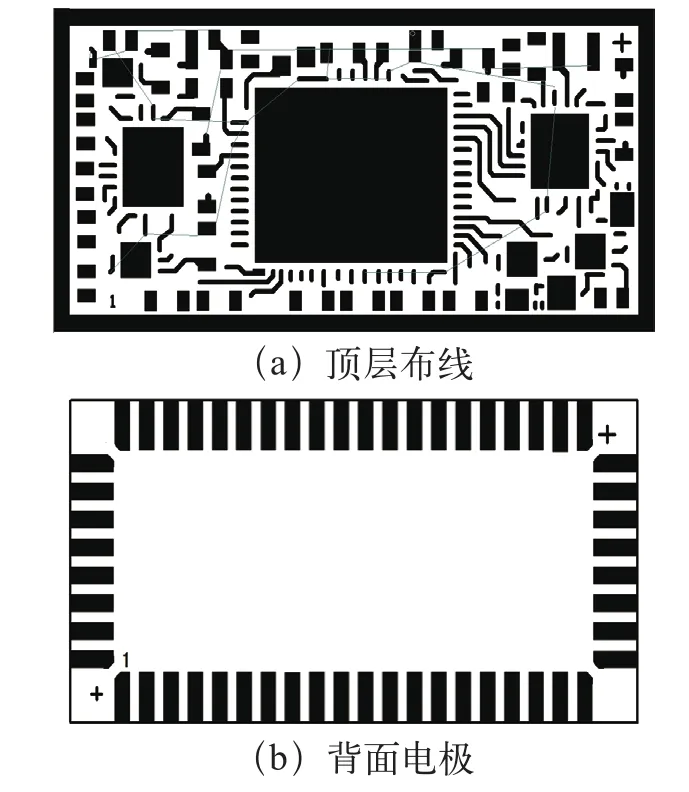

根据上述设计原则,我们对SiP-1、SiP-2、SiP-3三种电路的版图进行了设计,SiP-1、SiP-2、SiP-3都采用了8层基板结构,图5示意的是SiP-2电路的顶层和背面电极层的布线图。

3.3.4 SiP结构设计中的关键技术

(1)热匹配性设计

为了保证外引脚、密封框及多层陶瓷基板三者的热匹配性,外引脚和密封框的材料选用热膨胀系数与陶瓷基板相近的4J42型柯伐材料。

(2)密封框设计的热应力考虑

在密封框设计中,对密封框的4个拐角(内、外侧)进行了R1.0的倒角处理,以减小平行缝焊时密封框4个拐角处的热应力,提高封口质量。

(3)对外应力适应性的设计考虑

产品在系统中使用时,被焊接到系统的PCB板上。当某种外力使系统的PCB板弯曲时,产品的引脚势必受到外应力的作用。这种应力会导致产品的引脚脱落,甚至导致产品的壳体拉裂。采用图4所示的“Z”字结构引脚,将会吸收或缓冲因PCB板弯曲对产品产生的应力作用,提高产品的使用可靠性。

图5 SiP-2的顶层与背面层布线图

3.3.5 SiP结构的工艺设计

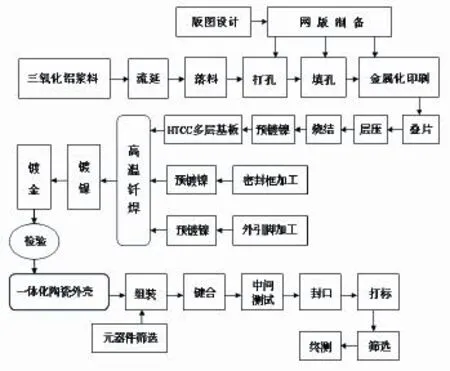

SiP结构的工艺流程如图6所示。

图6 SiP结构的工艺流程框图

4 集成化产品的技术性能

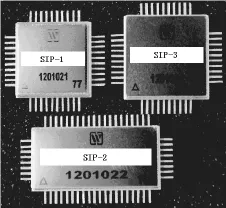

4.1 产品照片

SiP-1、SiP-2、SiP-3产品的照片如图7。

4.2 产品性能参数

采用HTCC工艺的SiP技术,通过合理的电路设计,使SiP-1、SiP-2、SiP-3产品达到如下技术指标。

图7 产品照片

(1)SiP-1的技术参数

供电电压:VDD=15 V±0.3 V,VSS=-15 V±0.3 V;

工作温范围:-55~125 ℃;

体积:≤17.6 mm×17.6 mm×3.8 mm;

重量:3.4 g;

激磁电源输出:5 V±0.01 V;

电压增益:36~44倍;

1通道输出(En=1,A2A1A0=000):2.4~2.6 V;

2通道输出(En=1,A2A1A0=001):4.3~4.8 V;

3通道输出(En=1,A2A1A0=010):-1.1~-1.9V;

4通道输出(En=1,A2A1A0=011):6.2~6.9 V;

5通道输出(En=1,A2A1A0=100):-3.0~-4.0V;

动态功耗:≤800 mW;

解调器振荡频率:18.5~20.0 kHz。

(2)SiP-2的主要技术参数

供电电压:VDD1=15 V±0.3 V,VDD2=5 V±0.3 V;

工作温范围:-55~125 ℃;

体积:≤29.6 mm×14.6 mm×3.8 mm;

重量:4.8 g;

单片机的时钟频率:20 MHz;

加力时序脉冲:高电平≥VDD2-1.0 V,低电平≤1.0 V,周期:5~30 ms;

动态功耗:≤840 mW。

(3)SiP-3的主要技术参数

供电电压:VDD=15 V±0.3 V,VSS=-15 V±0.3 V;

工作温范围:-55~125℃;

体积:≤19.6 mm×19.6 mm×3.8 mm;

重量:3.7 g;

每路开关输出电流:≥300 mA;

每个开关三极管的饱和导通电压(IC=100 mA时):Vces≤0.28 V;

每个开关三极管的漏电流:Iceo≤0.8 μA;

动态功耗:≤500 mW。

5 结束语

采用HTCC工艺的SiP技术制作的加速度计磁悬浮控制电路产品,具有体积小、高度低的特点,满足了整机系统对产品体积和高度的装配要求。同时,产品具有工作温度范围宽、参数稳定且一致性好、重量轻、可靠性高等优点,达到了整机系统对产品的设计要求,已被整机系统批量使用。本文介绍的基于SiP技术的电路设计方法、HTCC工艺SiP结构的设计思想,具有一定的工程指导价值。

[1]王壬林.加速度计[M]. 北京:国防工业出版社,1982.

[2]窦新玉. 系统集成封装技术[J]. 电子工业专用设备,2005,5.

[3]窦新玉.SIP:面向系统集成封装技术[N].中国电子报,2006,6,20(第C07版).

[4]王阿明,王峰. SIP封装工艺[J]. 电子与封装,2009,9(2).

[5]石磊. 系统集成封装技术是主流方向[N]. 中国电子报,2010,10,19(第009版).

[6]杨邦朝,顾勇,马嵩,胡永达. 系统级封装(SIP)的优势以及在射频领域的应用[J].混合微电子技术,2010,21(1).