高增益低功耗恒跨导轨到轨CMOS运放设计

赵毅,梁蓓

(贵州大学 理学院,贵州 贵阳 550025)

随着人们对电子产品低功耗设计的提出,模拟电路、数模混合电路的工作电压在逐渐降低。然而低电压导致了电路输入共模范围的变小,传统的PMOS或NMOS差分对已不能满足大的输入共模范围的要求[1]。同时,电压降低,噪声的影响就越来越显著,为了得到高的信噪比,我们必须尽可能扩展输入电压的动态范围,这样,轨到轨运放就应运而生。

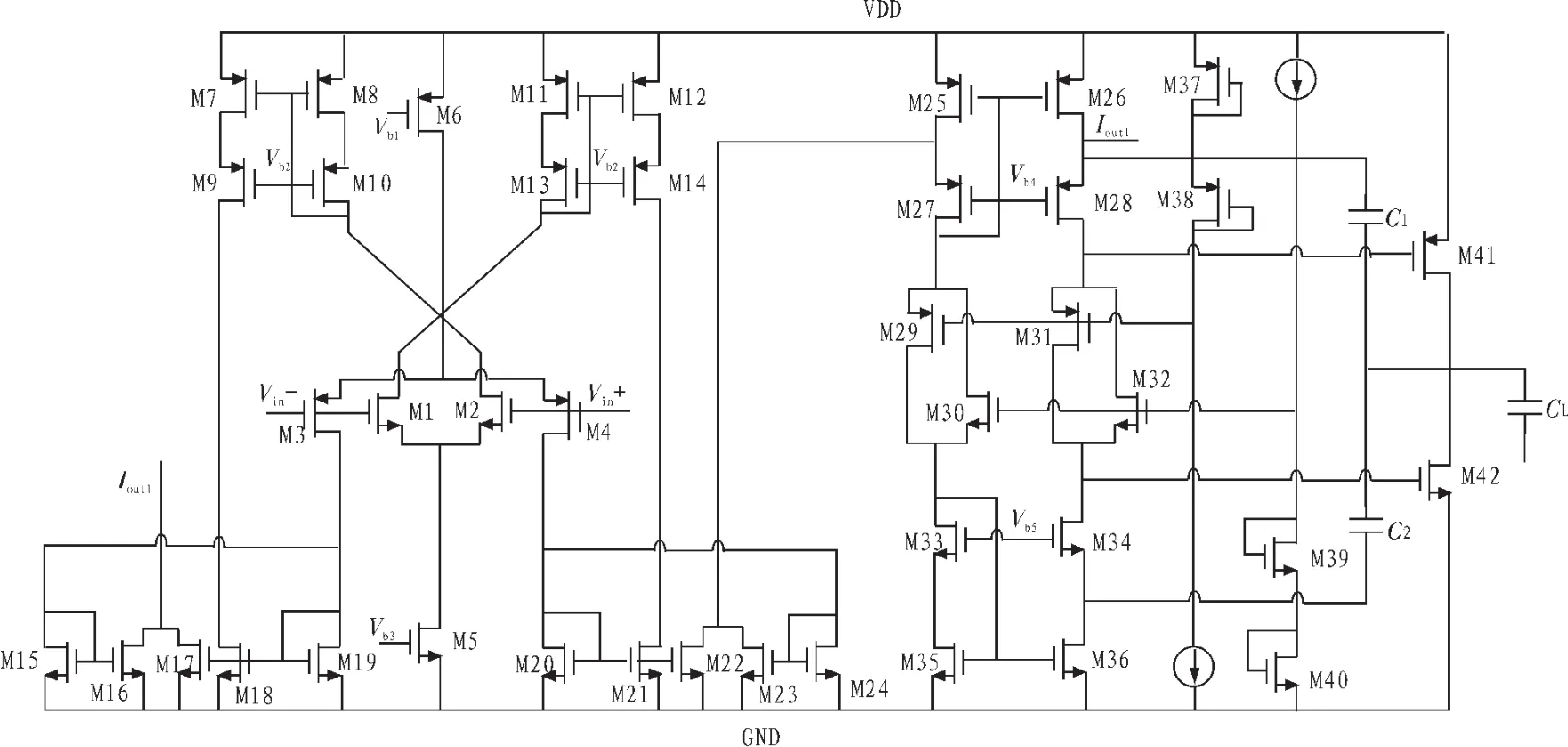

文中设计了一个3 V rail-to-rail运算放大器,采用最大电流选择电路实现输入级跨导恒定,推挽结构实现轨到轨输出。

1 输入级电路分析

由于NMOS、PMOS差分对的直流工作特性不同,使用互补差分输入对会导致一些问题而限制电路的整体性能。当共模电平仅使一对输入管导通时,共模抑制比会下降,还会引起输入级跨导的变化,且双输入对工作时的跨导是单输入对工作时跨导的两倍,这会影响电路的环路增益和频率补偿[2]。在很多文献中都有阐述如何实现输入级跨导的恒定,归纳起来比较常用的有3种方法:1)三倍电流镜技术。其缺点在于过于依赖电流的平方律模型,MOS管在强反型和弱反型时不能通用;2)使Vsgp+Vgsn保持不变以达到稳定输入跨导的目的。它的不足在于二极管连接形式的MOS管性能是其端电压的函数,这样跨导在输入共模变化的范围内不恒定;3)最大电流选择电路,这种方法的原理是在共模电压中间只允许一个差分对工作,其不足在于电路结构比较复杂。文中采用第3种方法来实现输入级跨导的恒定。

2 最大电流选择电路输入级

轨到轨输入的基本结构如图1所示,当只有NMOS对工作时,输入级跨导为 gmn=[2μncox(W/L)Iref]1/2;当只有 PMOS 对工作时,输入级跨导为 gmp=[2μpcox(W/L)Iref]1/2,我们可以调整输入级中N管和P管的宽长比使gmn=gmp。

图1 轨到轨输入级的基本结构Fig.1 Structure of rail-to-rail input stage

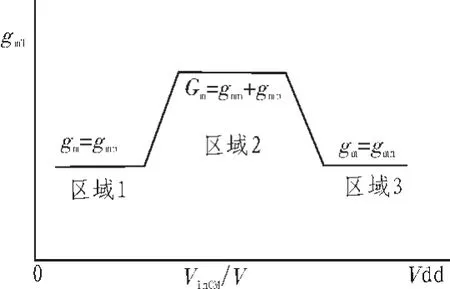

图2给出了共模电压在0~VDD之间变化时,输入级总跨导(gmT)的变化情况:我们可以看出,当 VinCM→0时,只有 P管工作,gmn=gmp;当 VinCM→VDD 时,只有 N 管工作,gmT=gmn;当VinCM趋于中间电平时,N管、P管都工作,此时gmT=gmn+gmp=2gmn=2gmp,输入级总跨导发生了两倍的变化[6],这会影响电路的增益和频率补偿。最大电流选择电路[1-2](如图3所示)可以实现输入级跨导的恒定,其工作原理如下:

图2 输入级跨导随共模电压的变化Fig.2 GmT versus the common-mode input voltage

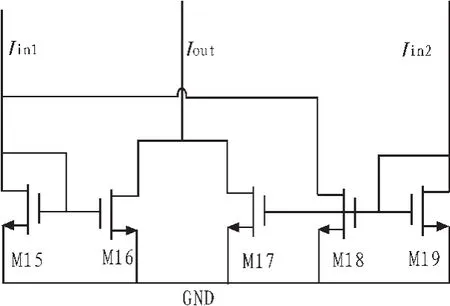

当 Iin1>Iin2时,由于电流镜的作用,ID15=ID16=Iin1-Iin2,ID17=ID18=ID19=Iin2,则 Iout=ID15+ID17=(Iin1-Iin2)+Iin2=Iin1=Max(Iin1,Iin2);

当 Iin1>Iin2时,M15、M16 截止,ID17=ID18=Iin2, 则 Iout=ID16+ID17=Iin2=Max(Iin1,Iin2);

当 Iin1=Iin2时,Iout=Iin1=Iin2=Max(Iin1,Iin2);

由此可得,在共模电压变化的过程中,最大电流选择电路 始 终 选 择 Iin1、Iin2中 的 较 大 值 输 出 ,即 取 出 gmn(max)和 gmp(max),这样就可以使输入级总跨导达到一个恒定值。

图3 最大电流选择电路Fig.3 Max current selecting circuit

图4 电流求和电路Fig.4 Summing circuit

3 电流求和电路

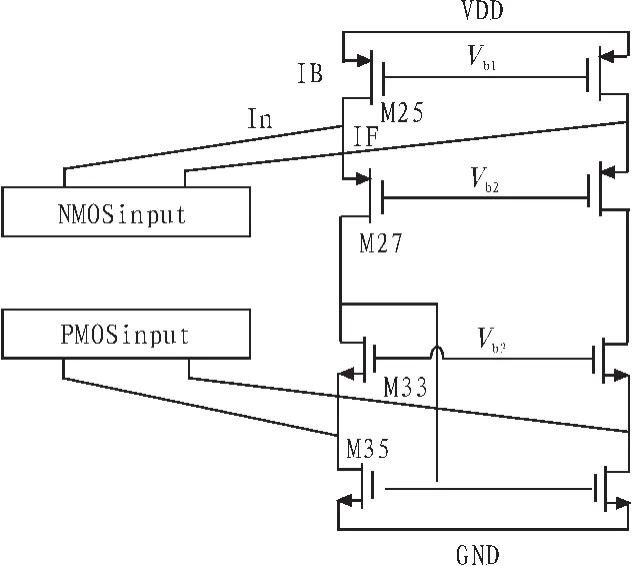

为了使反相的差分输入电流能够同相的驱动轨到轨输出级,就要用到电流求和电路,但这会在频率补偿时带来一些问题。如图4所示,M25、M26为求和电路提供偏置电流IB,它包括输入级电流 In和 M27、M28、M33、M34的偏置电流 IF。 由于NMOS差分对的电流随共模电压的变化而变化,其值可以从0变化到2In以上,其中In为NMOS差分对在共模电压VinCM为中间时的值。所以M25、M26要能为NMOS差分对提供这样的电流增量,还要能为电流求和电路提供最小静态电流。

另一方面,当VinCM处于共模电压中间值或VDD时,M25、M26中额外的偏置电流将流过M27~M34,这会改变这些管子中的静态电流,进而改变它们的跨导和输出电阻,从而引起运放零极点位置和低频增益的变化[3]。

文中采用浮置电流源[4-5]来稳定求和电路中的静态电流,即把浮置电流源嵌入求和电路中,具体实现方式在运放的整体电路(如图5所示)中给出。

图5 运放的整体电路图Fig.5 Circuit of the rail-to-rail operational amplifier

4 Class-AB输出级

为使电源的利用效率达到最大,要求输出级有尽可能大的摆幅和很小的静态电流。B类输出级可以满足上述条件,但它存在严重的交越失真;A类输出级不存在交越失真,但它的输出级效率只有25%,折衷考虑选用AB类输出级(如图6所示)。

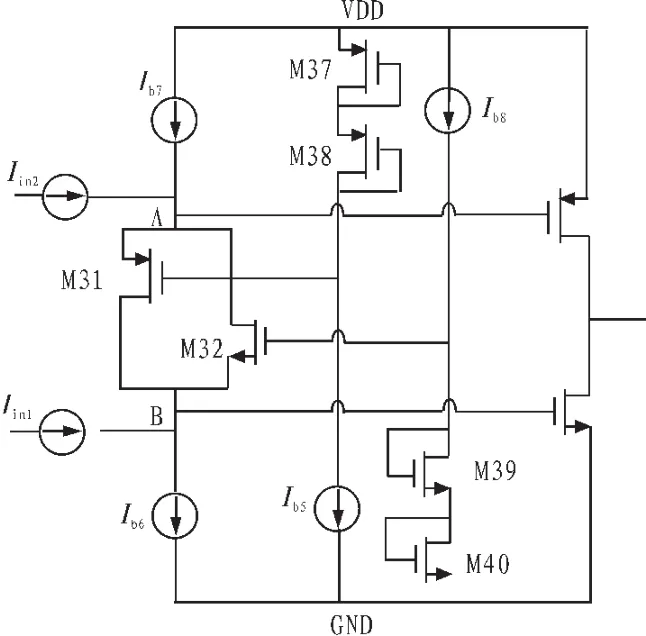

AB类输出级由两个共源级连接的输出晶体管M41、M42组成,其关键在于保持两个输出晶体管栅极间电压的恒定。浮置电流源由 M30、M31构成,二极管连接的 M37~M38、M39~M40 分 别 为 它 们 提 供 偏 置 。 M31、M37、M38、M41 和M32、M39、M40、M42 组成的两个跨导线性环[5],决定了输出晶体管的静态电流,稳定两个输出管栅极间的电压。

AB类输出级的工作原理如下:Iin1和Iin2分别为两个同相位的交流小信号电流源,设 Ib5=Ib6=Ib7=Ib8=I,Iin1=Iin2=0。 若(W/L)M29/(W/L)M38=1/2;(W/L)M30/(W/L)M39=1/2; 这样 M31 和 M38、M37和M41为同一个栅源电压;同理,M32和M39、M40和M42也为同一个栅源电压。 若 Ids(M41)=mI,Ids(M42)=mI,则(W/L)M41/(W/L)M37=m;(W/L)M42/(W/L)M40=m;各管子的宽长比还满足一下要求:(W/L)M42/(W/L)M41=(W/L)M40/(W/L)M37=(W/L)M39/(W/L)M38=(W/L)M32/(W/L)M31, 因为 A、B 间可视为一个浮动电压源,交流小信号下可视为短路,即VA=VB。于是有两种情况:1)当Iin1=Iin2>0时,电流流入节点A和B,则节点A和 B的电压升高,最终使 M41 截至、M42 导通,VA=VB=VDD;2)当 Iin1=Iin2<0时,电流流出节点A和B,最终使M41导通、M42截至,VA=VB=0,从而实现了轨到轨输出。

图6 浮置电流源控制的AB类输出级Fig.6 Class-AB output stage with floating current source control

文中采用了由两个电流镜M25、M26及M35、M36,共源共栅管M27、M28和M33、M34构成的特殊的求和电路。浮置电流源M31、M32稳定输入级电流的变化,它产生的电流流过M28、M34。输入差分对的电流在M27的源极汇集,该电流被M25、M26镜像,在M28的源极又被减掉。这样 M28、M34中的电流就与浮置电流AB类控制晶体管M31、M32中的电流一样并保持不变。采用这种结构的好处是输出级的偏置不受输入共模电压的影响。

由于采用了浮置电流AB类控制,电源电压的变化会影响输出晶体管中的静态电流,为了消除输出晶体管中静态电流随电源电压变化的敏感性,在浮置电流控制AB类左侧支路再引入一个结构完全相同的浮置电流源M29、M30(如图5所示)。

为避免出现正的零点,文中通过共源共栅管的路径来作米勒补偿,且米勒电容值C1=C2=1 pF。

5 仿真结果

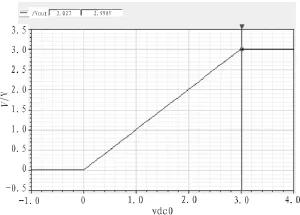

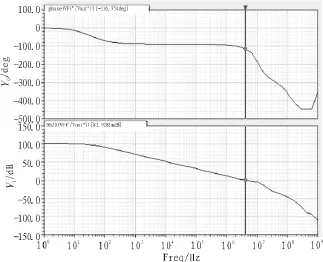

整个电路采用CSMC的0.5 μmCMOS工艺参数设计,经过Cadence仿真显示,运放可以实现轨到轨输入/输出(如图7所示),其幅频特性如图8所示,整个电路在3 V电源下工作,静态功耗仅为0.206 mW,驱动10 pF的容性负载时,增益高达100.4 dB,单位增益带宽约为4.2 MHz,相位裕度为63°。

图7 运放轨到轨输入、输出特性Fig.7 Input/output characters of the opamp

图8 运放的幅频特性Fig.8 Amplitude/phase characters of the poamp

6 结束语

本文设计了一个具有高增益且功耗相对较低的恒跨导轨到轨CMOS运算放大器,输入级采用最大电流选择电路来获得恒定跨导,输出级采用浮置电流源控制的AB类输出结构,最后仿真的结果表明,运放的各项性能均达到了预定的设计要求。

[1]陈斯,恽廷华.采用最大电流选择的恒定跨导Rail-to-Rail CMOS运放输入级[J].电路与系统学报,2006(12):120-122.CHEN Si,YUN Ting-hua.The input stage of constant-gm rail-to-rail CMOS opamp with max current selecting circuit[J].Joutnal of Circuit and Systems,2006(12):120-122.

[2]王红燕,陈向东.恒定跨导Rail-to-Rail CMOS运放设计[J].微电子学与计算机,2008(4):102-103.

WANG Hong-yan,CHEN Xiang-dong.Design of a constant transconductance rail-to-rail CMOS operational amplifiers[J].Microelectronics&Computer,2008(4):102-103.

[3]张红强,李攀.高性能Rail-to-Rail恒定跨导CMOS运算放大器[J].微电子学与计算机,2008(3):168-169.

ZHANG Hong-qiang,LI Pan.High-performance rail-to-rail constant-gm CMOS operational amplifier[J].Microelectronics&Computer,2008(3):168-169.

[4]Hogervorst R,Tero J P,Eschauzier RGH.A compact powerefficient 3V CMOS Rail-to-Rail input/output operational amplifier for VLSI cell libraries[C].ISSCC’94.San Francisco,CA,1994:244-245.

[5]Klass-Jan,Langen D,Huijsing H.Compactlow-voltage power-efficient operational amplifier cells for VLSI[J].IEEE J Solid-State Circuit,1998(33):1482-1496.

[6]LIN Chi-Hung,Ismail M.Robust design of LV/LP lowdistortion CMOS rail-to-rail input stages[J].Analog Integrated Circuit and Signal Processing,1999(21):153-162.

[7]Willy M.C.SANSEN.Analog Design Essentials[M].Catholic University,Leuven,Belgium.Published by Springer,2007.