一种宽电压差电平转换接口电路设计

孙 烁

(中国电子科技集团公司第四十七研究所,沈阳 110032)

1 引言

随着现代电子系统运行速度越来越快,并行处理的数据量越来越大,为了降低核心处理器的功耗,产生了各种大量低电压供电的核心处理器。为了与原有的5V 系统相兼容,需要引入相应的电平转换电路,用以实现不同供电电压芯片之间的数据转换。这就要求这种电平转换电路运行速度快,电平转换范围宽。为了适应这种需求,芯片供应商已经研制并提供了一些专用的电平转换电路,如美国德克萨斯公司提供的SN74ALVC164245[1]等。这些电路具有很好的性能,但电平转换电压相对固定,例如5V至3.3V 之间转换,或3.3V 至1.8V 之间转换,如果要实现更宽电压差的电平转换,例如实现5V 与低至接近1V的电平转换,这类芯片还难于胜任。

笔者在数据电平转换方面做了有益的尝试,基本设计思想是:充分利用通用的74HC 系列芯片实现不同供电系统之间的高速、并行数据转换。74HC系列芯片的电源电压范围为2V~6V,但实际上供电电压降至1V时仍可正常工作,利用这一特点,可以实现从5V 至接近1V的电平转换。本设计具有转换电压差宽、通用性强、设计简便、使用灵活、成本低、易操作、易于采购的特点。

2 电平转换电路组成原理

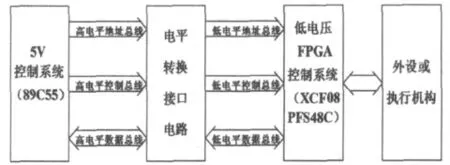

笔者在承担的一个课题中,需要测试一个低压供电的FPGA 电路的数字逻辑功能。为此,设计了一个5V的单片机测试系统,通过电平转换电路向该FPGA 发送各种指令和数据,并接收FPGA 执行指令后的反馈数据,包括电平转换电路在内的单片机测试系统原理框图如图1 所示。

图1 原理框图

3 电平转换接口电路

3.1 电平转换接口电路原理图

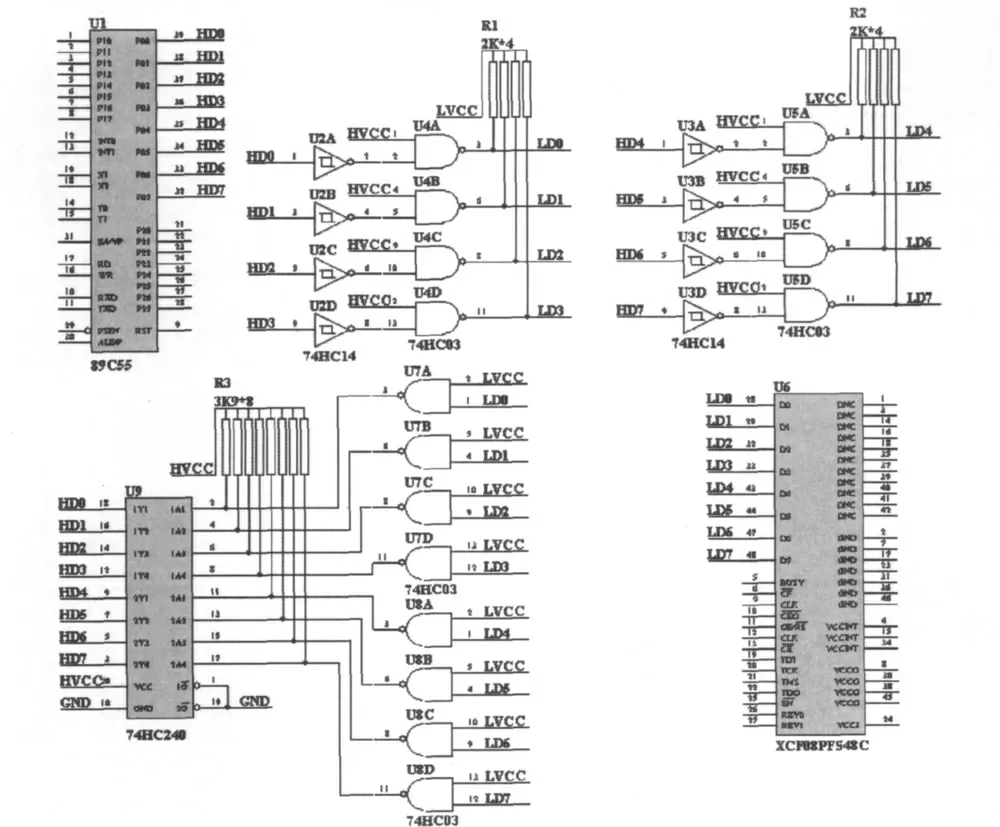

测试电路由5V 控制系统(89C55),电平转换接口电路,低电压的FPGA(XCF08PFS48C[2])电路,外设或执行机构,地址、控制、数据总线等构成。在设计中,89C55是5V 控制系统的核心,通过电平转换接口电路,将控制总线、地址总线及8 位的数据总线与低电压的FPGA 电路相连接,FPGA 对数据高速处理后,对外设或执行机构进行控制,同时FPGA将数据处理的情况,通过数据总线和电平转换接口电路发回给89C55。在本设计中,无论数据总线、控制总线还是地址总线,其数据在传输过程中,经过电平转换接口电路的结构形式是一样的,所以,仅以8 位数据总线为例来介绍本电平转换电路,如图2 所示。

图2 电平转换接口电路原理图

3.2 电平转换电路的工作过程

图2 中,数据信号由高电平向低电平转换的电路位于上半部分,即由74HC14[3]、74HC03[3]和2K排电阻组成。数据信号由低电平向高电平转换的电路位于下半部分,即由74HC240[3]、74HC03 和3.9K排电阻组成。电平转换的本质是依靠74HC03的OC 门输出实现的,由于74HC03是与非门电路,为保障电平转换前后的一致性,在高电平变为低电平端增加了非门电路74HC14,在低电平变为高电平端也增加了非门电路74HC240。

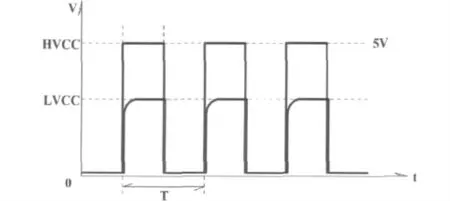

3.3 电平转换电路的波形图

本设计电平转换电路的波形如图3 所示,HVCC为高电平端电源电压,LVCC为低电平端电源电压,实际使用中HVCC为5.0V,LVCC为2.5V,主控芯片89C55的时钟频率为24MHz,整个试验过程顺利,电路工作稳定。图3是在T为100ns的条件下测试的波形图。笔者曾将LVCC 下调至1.2V,电平转换电路的工作依然正常稳定,上升沿和下降沿的边沿波形仍然良好。

图3 电平转换电路的波形图

4 结束语

以上介绍的电平转换电路适用于转换电压差范围要求较大的产品,特别适合低成本、大量生产的产品。该电路简单、实用、方便,是经过实际应用并取得成功的设计。

[1]INTERBIRD.SN74ALVC164245[DB/OL].http://www.alldatasheet.com/datasheet- pdf/pdf/465609/TI1/SN74ALVC164245-EP.html,204-06—2005-10.

[2]INTERBIRD.XCF08PFS48C[DB/OL].http://www.alldatasheet.com/datasheet- pdf/pdf/133722/XILINX/XCF08PFS48C.html,2005-3-14.

[3]电子工程手册编委会,集成电路手册分编委员会.高速CMOS 电路[M].北京:电子工业出版社,1994.