基于FPGA 和Qt的图像处理系统设计

王炳松,李汶洲,庄圣贤

(西南交通大学信息科学与技术学院,成都 610031)

1 引言

CIS 图像采集处理系统存在数据量大,图像质量要求高,同时对便携性、体积、功耗、成本也有极高的要求,因此在设计时必须综合考虑这些因素,提出合理的设计方案。通常的方案是以FPGA 作为主处理器,先将采集到的数据全部存到外部缓存,然后从缓存中读出数据处理,后经D/A 转换送至PC 端显示[1]。这种系统虽很稳定也不会出现掉数据的情况,但由于FPGA的硬件电路特性,只能做一些简单的图像处理,同时时效性、功耗、灵活性也会很差,不能满足CIS 图像处理的要求。另一种方案是,将采集到的数据在FPGA 内部缓存预处理之后送DSP 做后续复杂处理[2],但有时我们只要实时获取很好的图像质量,后续处理不是必须或特定的,并且对速度要求也不高(如便携式扫描仪系统),采用FPGA +DSP 会加大复杂度和浪费资源。所以本设计提出一种既能满足实时获取图像,又能做后续复杂处理的低成本方案。

2 系统结构设计

CIS 图像采集与处理系统主要由CIS 图像获取模块、实时图像滤波模块、通信模块、Qt 显示与处理模块以及相应的外围电路组成,各个模块的功能介绍如下:

图像获取模块:将CIS 输出的模拟信号,经隔直、放大后,在FPGA的控制下完成A/D 转换,将模拟信号转换成数字信号,并将数字信号送图像滤波模块。

数字滤波模块:该模块的主要功能是:①在FPGA内部,对进入该模块的数字信号完成滤波;②将滤波后的数据写入外部缓存器,并在滤波算法间隙将外部缓存中的数据读出发往USB 传输模块。数字滤波模块是整个设计能否成功的关键部分。

通信模块:配置好USB 固件后,在FPGA 控制下,图像数据通过USB 传送到PC 端。同时,USB 也可以接收PC 端的命令,并把命令读出给FPGA,FPGA译码出命令后执行相应的操作。

PC 端显示与处理模块:一方面,PC 端软件接收到数据后,把数据编码成图像显示出来。另一方面,用户还可以在Qt 软件上通过操作界面控制硬件工作,或对图像做复杂的后续处理。

CIS 采集处理系统框图如下图1 所示。

图1 CIS 采集处理系统结构框图

3 系统的具体实现方案

明确了各模块的功能后,现在要解决的问题是:如何把这些模块组合起来,让它易于实现,并保持长时间的稳定性;同时寻求可靠的改进方法,让图像质量更好。下面将详细介绍各模块的实现方式。

3.1 CIS 图像获取模块

为扩展系统应用,该设计可选如下采样模式:按接触面大小有A4、A5、A6、A7 和任意幅面五种模式,按需求颜色有彩色、黑白、二值三种选择,按分辨率有300DPI 和600DPI 两种模式。可根据需要在PC 端选择好,然后再开始采样。由于CIS是行采集器件,所以必须要计算好行频、每行的有效点数以及采样的行数,让采样出来的数据和PC 端设置的工作模式相对应,同时为了图像色彩更加真实,必须调节好曝光时间。再者CIS的输出是模拟信号,在进入FPGA之前,必须把它转换成数字信号,而要获得我们需要的数字信号必须先对A/D 内部寄存器进行正确的配置。当然,为防止外部信号的干扰,数字信号在进入FPGA 之前会加隔离芯片对干扰信号隔离。

3.2 实时图像滤波模块

由于电子电路噪声和低照明度或高温带来的传感器噪声大体上呈现高斯分布,为了消除这些噪声而获得较好的图像质量,本模块采用高斯平滑滤波器。实现高斯滤波,常选用的高斯核有:3 ×3,5 ×5,7 ×7。更大的高斯核需要更多的缓存,也即意味着所需的FPGA 价格也就更高。综合性价比,本设计选择高性价比FPGA EP4CE10F17C8,此芯片内部有46KB RAM,最高工作频率可达200MHz,能满足设计要求。

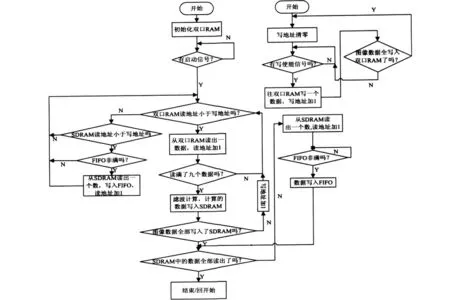

进入到FPGA 中的数字信号,实时写入双口RAM 缓存,同时从缓存中读出所需的图像数据构成3 ×3的高斯核,然后进行高斯滤波算法,把计算出的值写入SDRAM,去检测是否可以从双口RAM 中读出数据,如若能,继续读出数据计算,否则把SDRAM 中的数据读出来写入FIFO 中,以备下一个模块使用。此过程图像数据依次流入:实例化双口RAM、SDRAM、实例化FIFO,具体的操作流程如下图2 所示。

3.3 通信模块

图像传输采用外部FPGA 主控Slave FIFO 方式来实现,因此USB 通信模块由三部分组成。

(1)FPGA 主控部分

控制滤波后的数据有效地写入已激活的USB大端点FIFO。在USB 固件中配置好端点后,FPGA中完成的只是检测端点数据包非满后,从上一模块的FIFO 中读出数据,写入有效的端点FIFO,直到图像的数据全部写完,回到初始状态。

(2)USB 固件配置部分

Cypress的安装程序中提供了一些固件配置例程,通常的应用只要根据需要修改相应的程序即可,本设计是通过修改例程Bulkloop 中的bulkllop.c 完成的,其它的文件,包括端点配置或协议文件等,如非必要,尽量不要动。bulkllop.c 已经为用户搭好了架构,用户只需在对应的函数中添加代码即可。此处要完成USB 大小端点的配置、检测启动扫描信号及PC 与FPGA 间的通信。端点配置在TD_Init()函数中完成,需配置的寄存器如下表1 所示。

图2 图像滤波算法流程图

表1 USB 固件配置的寄存器

检测启动信号在TD_Poll(void)函数中实现,此函数会在USB 空闲时反复调用。PC 与FPGA的通信会在ISR_Ep1out(void)interrupt 0 函数中完成,当EP1OUT 中有数据时就会触发中断,接收PC 端发来的命令,验证后把它传递给FPGA 中的编译码部分。

FPGA 编译码部分,译码USB 发送的指令,并控制FPGA 执行相应的操作,同时也可编码FPGA的状态通过USB 告知PC 端。

3.4 PC 端显示及处理模块

设计中存在USB 芯片与应用程序之间的通信,而应用程序和硬件交互信息要借助API 接口,所以本例调用了Cypress的CyAPI 库接收USB的端点数据并应用Qt 库函数将RGB 数据转换成图像显示在Qt 软件上。接收图像数据流程如图3 所示。

图像显示出来后,随即可以利用Qt 库函数或手写算法完成图像的后续处理。本设计调用QMtrix库函数实现了图像的放大、缩小、旋转、镜像,手写算法完成了图像的锐化、对比度饱和度校正、伽马值矫正、自动裁剪、手动裁剪等操作,如有需要还可简便地添加其它图像处理算法。

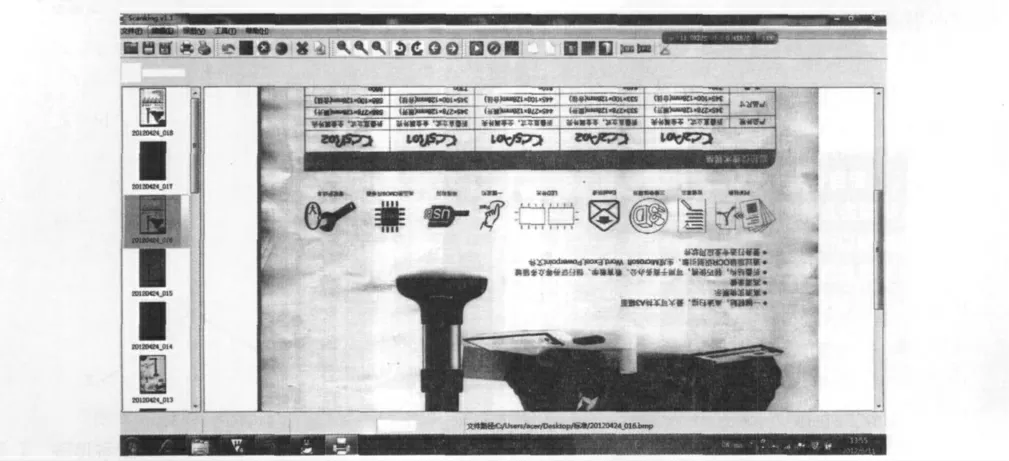

下面仅对在Qt 界面中加入缩小动作做介绍,其它以此类推。因为Qt是利用信号槽机制完成界面操作的响应,信号会在某个特定情况下被触发,槽是等同于接收并处理信号的函数。所以首先在工具栏中加入缩小动作按钮,然后给这个动作配上相应的槽函数,当点击缩小图标时,信号被触发,槽函数响应事件并实现图像的缩小算法,处理完成后,调用Qt的相关库函数显示图像。图4,图5 分别是原图与缩略图。

图3 Qt 软件接收图像数据流程图

图4 原始图像

4 结束语

根据上面提到的设计思路完成了CIS 图像采集处理系统的设计,并在软硬件平台上得到了验证。实验结果表明:CIS 采集完成后界面上可立即出现图像,延时不超过1s。显示效果如图(5)所示,从图中可看出已采集到了完整的图像,但是由于PCB 板布线及抗干扰措施并没做的很好,以及后期调试时间有限,所以后续图像质量改善的空间很大。

在设计中,数据传输用到的是Cypress 超低功耗芯片CY7C68013A,它的工作电压为3.3V,容限输入为5V,而采集板上的最高电压是CIS的供电电压5V,所以可以借助USB 供电,满足即插即用。

Qt 软件是微软旗下的开源跨平台界面软件,利用它可以方便的完成很多图像处理操作,代码不用重写就可以再移植到其它操作平台上,给后续的升级扩展带来了很大方便。现在图像处理应用非常广泛,以此设计为基础,只要稍加改动就能应用到许多软硬件相结合的图像处理系统中。

图5 缩略图像

[1]伍乾永,陈彬.基于FPGA的实时图像数据采集模块设计[J].微电子学,2010(3):453-456.

[2]罗戈亮,鲁新平,李吉成.基于FPGA +DSP的实时图像处理系统设计与实现[J].微处理机,2010(2):108-110.

[3]WaleWasfy,Hong Zheng.General Structure Design for fast Image Processing algorithms based upon FPGA DSP slice[R].IEEE ISEC 2010 国际计算通信控制管理研讨会,2010:726-729.

[4]王诚,蔡海宁,吴继华.Altera FPGA/CPLD 设计[M].北京:人民邮电出版社,2011.

[5]钱峰.EZ- USB FX2 单片机原理、编程及开发应用[M].北京:北京航空航天大学出版社,2006.

[6]谭安菊,龚彬.USB2.0 控制器CY7C68013 与FPGA 接口的Verilog HDL 实现[J].电子工程师,2007(7):52-54.

[7]郑阿奇.Qt4 开发实践[M].北京:电子工业出版社,2011.

[8][英]Mark Summerfield.Qt 高级编程[M].白建平,王军锋,闫锋欣,白净,译.北京:电子工业出版社,2011.

[9]詹红霞.Visual C ++6.0 程序设计[M].西安:西安电子科技大学出版社,2009.

[10]求是科技.Visual C++图像处理典型算法[M].北京:人民名邮电出版社,2006.