W波段宽带倍频器的设计与仿真

严 琳,董 俊,李天明,汪海洋,周翼鸿

(电子科技大学 物理电子学院,四川 成都 610054)

W波段宽带倍频器的设计与仿真

严 琳,董 俊,李天明,汪海洋,周翼鸿

(电子科技大学 物理电子学院,四川 成都 610054)

本文介绍了一种由低次级联形式构成的W波段宽带六倍频器。输入信号先经过MMIC得到二倍频,再由反向并联二极管对平衡结构实现宽带三倍频,从而将Ku波段信号六倍频到W波段。该倍频器的输入端口为玻璃绝缘子同轴转换接头,输出为 WR-10标准矩形波导结构。仿真结果表明当输入信号功率为20dBm时,三倍频器在整个W波段的输出三次谐波功率为4.5dBm左右,变频损耗小于17dB。该设计可以降低毫米波设备的主振频率,扩展已有微波信号源的工作频段。

W波段倍频器;带通滤波器;平衡电路;反向并联二极管对

随着毫米波技术在现代通信和雷达系统等领域的广泛应用,我们对稳定、可靠和易于工业化生产的毫米波信号源的需求越来越迫切。目前获得毫米波源的方式有毫米波锁相源、毫米波振荡源和倍频器,其中宽带倍频技术是一种既有效又经济实用的途径,可以降低本振的主振频率又将微波频段信号扩展到毫米波段并保持原信号的优点,比如高稳定性和低相位噪声。

由于在毫米波段国外对我国实行了严格的军事禁运政策,W波段倍频MMIC难以获得,所以本文就如何实现W波段宽带六倍频作了一定的介绍。肖特基二极管属于电阻性倍频,可实现较宽的倍频程,其原理简单,成本低,是低次倍频的常用器件[1],但效率不高,文献[2]证明了其最优倍频效率不超过1/n2(n为倍频次数)。所以要想在W波段获得高的输出功率是目前公认的难题。采取低次级联倍频和合理选取电路结构将有助于提高全波导带宽内的输出信号功率,同时这也是本设计的重点和难点。本设计先由AMMC-5040得到二倍频,再级联反向并联二极管对实现三倍频,整个设计结构简单、易加工,在W频段全波导带宽内实现了较高的功率输出。

1 肖特基二极管倍频原理

目前国外W频段倍频器大都采用MMIC方式实现[3],而国内芯片的发展水平与国外存在的差异使我们只有寻求用混合集成电路形式来实现。利用非线性电导器件(如GaAs肖特基势垒二极管)的I/V特性,通过一定的平衡式结构,使输入信号波形产生畸变,从中提取出某次谐波分量,即可实现所要求次数的倍频。且其带宽性能主要由外电路的带宽性能决定,而不取决于器件本身。所以对于全波导带宽倍频器的实现,使用非线性电导器件是非常理想的选择。

采用两只反向并联的肖特基二极管对可以提供较大的输出功率并有效地抑制不必要的

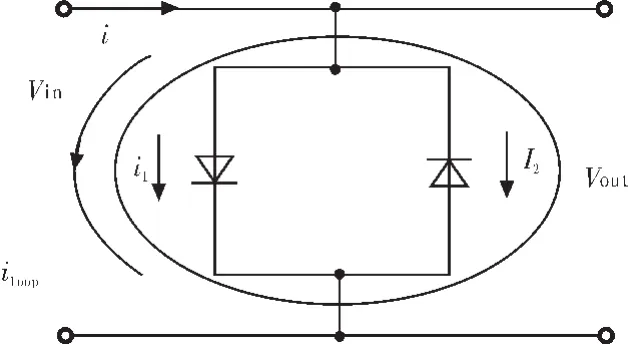

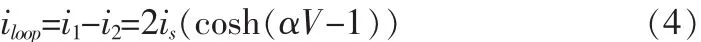

谐波分量来实现三次倍频。其工作原理如图1所示,二极管对对于输入输出回路均呈反向并联。

当图1所示电路输入端有信号激励时,设输入电压为V,则两个单管的电流分别为

其中,is为二极管的反向饱和电流,α=q/nKT(n为二极管的理想因子),表明只与二极管本身特性和绝对温度有关。

图1 反向并联二极管对工作原理Fig.1 Operating principle of anti-parallel diode pair

则反向并联二极管对的外部总电流为:

环内的电流为:

将 V=Vscos(ωst)代入(3)、(4)式,并作傅立叶级数展开,得:

式(6)中In为n阶第一类变态贝塞尔函数。

由(5)、(6)式可知,反向并联二极管对外电路中只有输入信号的基波和奇次谐波,而输入信号的偶次谐波仅存在于内部环路中。通过以上分析,说明这种电路结构适合用于奇次倍频,并且由于外电路不包含偶次谐波,因而可减少其他一些辅助电路(如空闲回路)的设计。

2 W波段六倍频器的设计

目前40 GHz以下频段商用MMIC芯片易获得,为了减小电路的复杂性和体积,本设计的前置二倍频器采用MMIC芯片,W频段三倍频器采用的倍频二极管为Alpha公司的DMK-2790 GaAs肖特基势垒二极管,它具有低结电容,低串联阻抗的特性,适合于混频器、倍频器的设计。

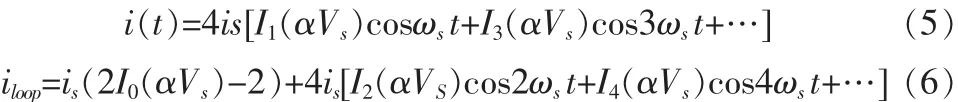

整个电路的结构流程如图2所示。

图2 六倍频电路设计框图Fig.2 Design block for sextupler circuit

2.1 MMIC前置二倍频和功率放大器

AMMC-5040芯片是一款四级宽带、高增益的放大器,其输入输出匹配至50,在20~40 GHz范围内,增益可达20 dBm,饱和输出功率为21 dBm。作为倍频器使用与放大器唯一差别在于倍频时需要给第一栅极单独供电,其余的栅、漏偏置则与放大器模式完全相同。为了方便起见,本设计中的二倍频器和前置功率放大器都采用此芯片,由MAX881R和NTMS 5P02R2提供所需偏置电压。

2.2 带通滤波器的设计

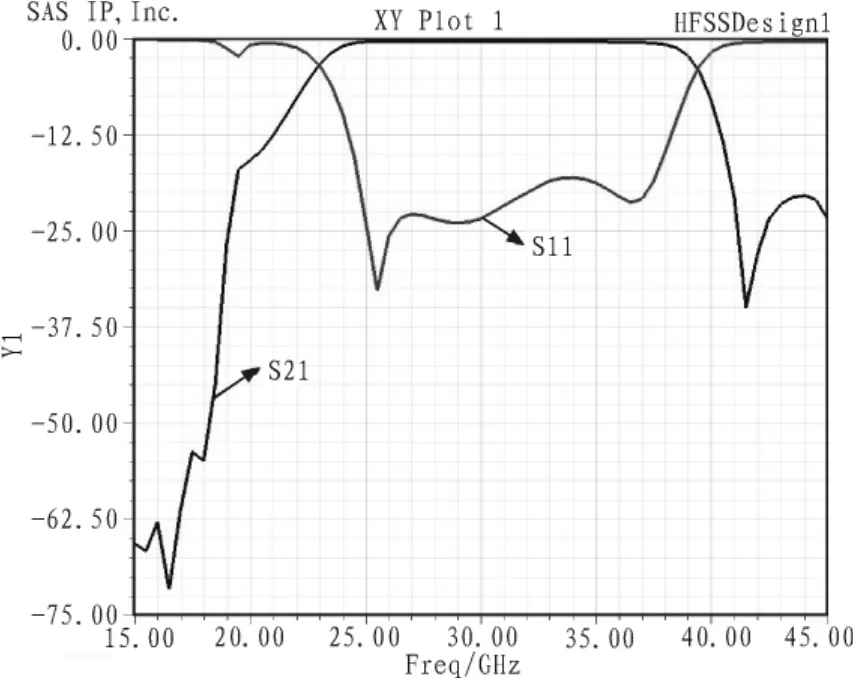

由AMMC-5040的性能图可知,其作二倍频时,当输入信号频率超过13 GHz后,基波输出功率上升,而二次谐波输出功率下降,对基波的抑制越来越不够,尤其到了17 GHz后的频率,基波功率大于二次谐波功率,如果不对基波进行有效的抑制,那么将对倍频器最终的谐波抑制产生不利。另外还必须对二倍频后产生的3次谐波进行抑制,以防有用信号功率淹没。本设计的输入信号为12.5~18.33 GHz,要求二倍频后得到干净的输出以驱动二极管对三倍频,所以必须在二倍频后添加一带通滤波器来抑制不需要的信号。该滤波器要求通过25~36.66 GHz的信号,对带外信的抑制度大于20 dB,尤其是对13~18.33 GHz信号要有较大的抑制度。常用的微带带通滤波器有平行耦合线型,发夹型,交指型等结构。综合考虑带宽和电路尺寸等因素,本设计采用的是直接耦合短截线带通滤波器中的λg/2并联开路短截线和λg/4连接线滤波器[5],阶数是四阶。图3和图4分别是此滤波器在高频仿真软件HFSS中的仿真模型和优化后以dB为单位表示的S11与S21曲线,从图上可以看出滤波器带内插入损耗小于0.5 dB,带外抑制大于20 dB,其结果较好的满足了设计要求。

图3 带通滤波器在HFSS中的仿真模型Fig.3 Simulation model of bandpass filter in HFSS

图4 滤波器S11和S21参数优化结果Fig.4 Optimized insertion and return losses of the filter

2.3 微带-波导过渡转换的设计

微带-波导过渡应满足以下要求:低的传输损耗和高的反射损耗;宽的频带范围;设计和制作简单,便于加工;便于与系统的集成。目前,常用的微带-波导过渡结构主要有3种:阶梯加脊波导过渡、对极鳍线过渡、耦合探针过渡。其中微带-探针-波导过渡由于具有低损耗、宽频带、结构简单、体积小和可靠性而被广泛采用。

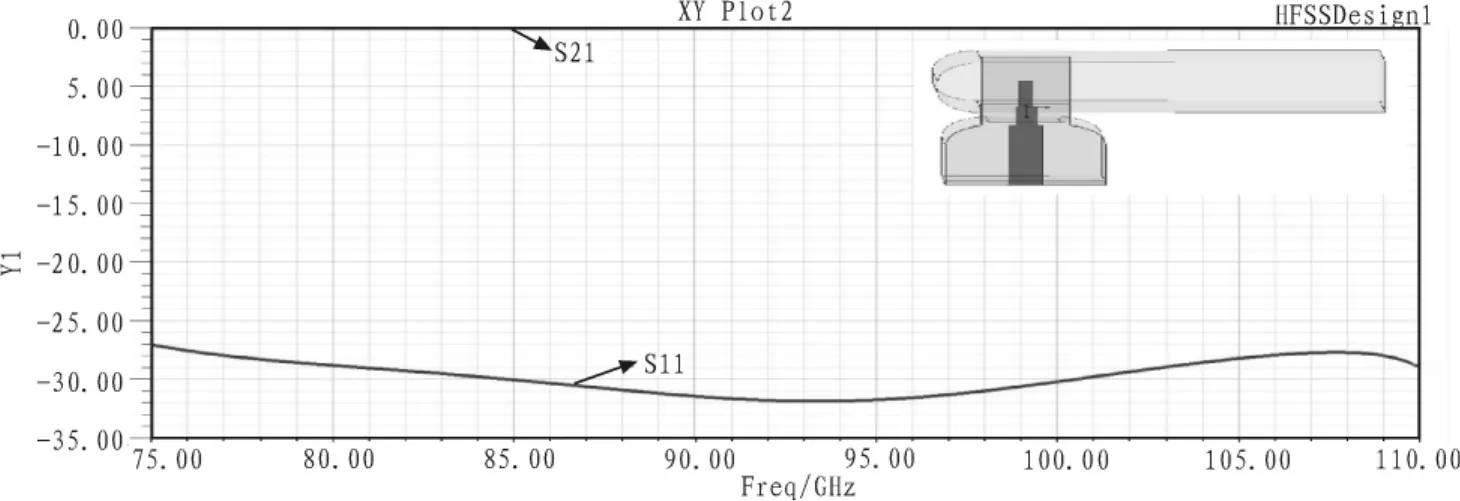

此倍频电路的输出为采用E面探针过渡模型。通过调节插入波导内部探针的长度、宽度、与短路面的距离及四分之一阻抗变换和窗口尺寸来得到过渡性能的最优值。为了便于精确测试,需要建立微带探针过渡的背靠背模型,单个过渡结构的插入损耗则为背靠背仿真模型的一半。图5为HFSS仿真优化后得到单个过渡结构的插入损耗和回波损耗,其中S11小于-27 dB,S21大于-0.065 6 dB,能够较好地实现从微带到波导的传输。

图5 输出微带-探针-波导过渡S参数Fig.5 Insertion and return losses of microstrip to waveguide probe transition

2.4 倍频器整体电路的仿真设计

该设计的整个电路制作在Rogers Duriod5880基片上,介质基片厚0.127 mm,介电常数为2.2,输入端采用玻璃绝缘子插针配合K接头的信号输入方案,输出为微带探针波导过渡。将在HFSS中设计好的带通滤波电路和输出微带探针波导过渡的S参数文件导入 ADS中,根据二极管的Spice模型参数,得到其仿真原理图如图6所示。

图6 三倍频整体仿真原理图Fig.6 Simulation principle of the tripler

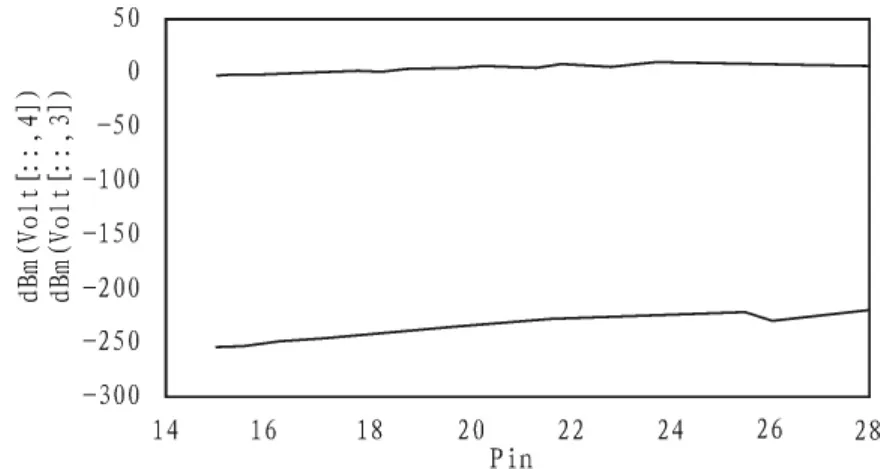

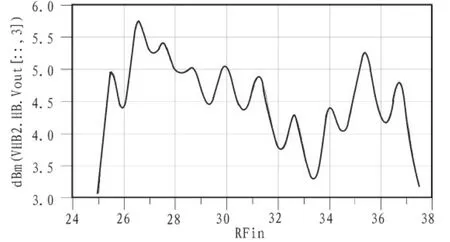

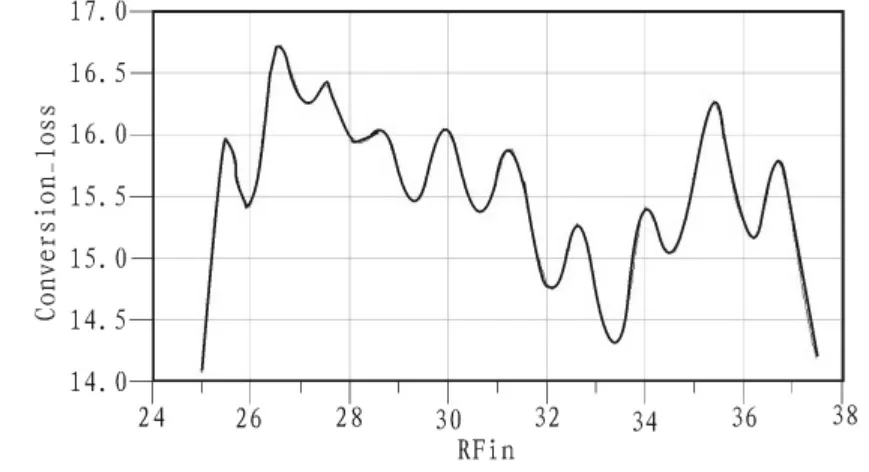

图7是固定频率26 GHz时3次谐波与4次谐波输出功率随输入功率变化曲线。从输出谐波功率值来看,4次谐波输出功率值相对于3次谐波功率值已经非常小了,可以忽略不计,也就是说此电路结构对于外部电路来说只产生奇次谐波,而偶次谐波被电路内部环路所消耗,由此验证了文中关于奇次倍电路设计理论的可行性[7]。仿真结果如图7和8所示,3次谐波平均输出功率在4.5 dBm左右,输出功率平坦度小于 1 dB,全频带内的变频损耗约 15.5 dB。

图7 3、4次谐波输出功率Fig.7 Output power of third and forth harmonics

图8 三次谐波输出功率与频率关系曲线Fig.8 Relation curve between third harmonic’s output power and frequency

3 结 论

图9 变频损耗与频率关系曲线Fig.9 Relation curve between conversion loss and frequency

文中利用HFSS和ADS设计了W波段宽带六倍频器,并介绍了整个设计过程。其仿真结果表明在W波段全波导带宽内,该结构的输出功率和变频损耗都较好,可作为一种3 mm频率源设计参考,应用于雷达、通信等相关系统中。带通滤波器直接影响倍频器的谐波抑制度与功率平坦度,若要实现高效率的W波段宽带倍频器,则设计性能优良用、结构简单、体积较小和加工方便的带通滤波器是关键,其仿真优化的时间较多。由于ADS在毫米波段路仿真的准确性不高,会导致实际测试结果会与仿真结果有较大偏差,所以要使设计达到更佳性能还需反复调试。

[1]费元春.固态倍频[M].北京:高等教育出版社,1985.

[2]Batelaan P D,Freking M A.Quantum well multipliers,Int.Conf.on Infrared and Millimeter Waves,1987:14-15.

[3]Morgan M,Weinreb S.A full waveguide band MMIC tripler 75-110 GHz, IEEE MTT-S Digest,2001:103-106.

[4]Stephen A Mass.Nonlinear Microwave and RF Circuits[M].2nd ed.Artech House, INC.2003:301-315.

[5]甘本祓,吴万春.现代微波滤波器的结构与设计[M].北京:科学出版社,1973.

[6]Leong Y-C,Weinreb S.Full Band Waveguide-to-Microstrip Probe Transtions,IEEE-MMTS InternationalMicr-owave Symposium Digest,1999(4):1435-1438.

[7]张国飞,崔志胜,徐广鑫,等.基于瞬时无功功率理论的APF谐波补偿能力的仿真研究 [J].陕西电力,2012(11):77-81.

ZHANG Guo-fei,CUI Zhi-sheng,XU Guang-xin,et al.Instantaneous reactive power theory-based simulation of harmonics compensation performance of active power filter[J].Shaanxi Electric Power-2012(11):77-81.

Design and simulation of broadband frequency multiplier in W-band

YAN Lin, DONG Jun, LI Tian-ming, WANG Hai-yang, ZHOU Yi-hong

(School of Physical Electronics, The University of Electronic Science and Technology of China, Chengdu 610054, China)

A broadband frequency multiplier in W-band has been realised by the way of low-cascading.The input signal is doubled by a MMIC first and then tripled by a balance circuit which is formed by anti-parallel Schottky-Barrier diode pair,the signal of Ku-band has been extended to W-band.Its input signal is fed in by the glass insulator,the output signal is fed out by a WR-10 waveguide.While the input signal power is 20dBm,simulation shows the third harmonic output of the tripler is about 4.5 dBm, and the conversion loss is lower than-14.3dB.It can reduce the frequency of main vibration equipment, expanding microwave signal source’s working frequency.

W-band multiplier; bandpass filter; balance circuit; anti-parallel diode pair

TN454

A

1674-6236(2013)04-0068-03

2012-08-24稿件编号201208130

严 琳(1988—),女,江西赣州人,硕士研究生。研究方向:微波毫米波电路与系统。