基于PCI总线无时钟LVDS数据采集卡的研究

姜日东,徐志跃

(北京航空航天大学 北京 100191)

PCI总线因其速度高、兼容性好、可靠性高且成本低等优点使其在各种与主机通信的总线技术中优势很明显[1],而LVDS(Low Voltage Differential Signaling)通信协议采用数据串行化差分信号传输方式,可以有效地降低噪声和低电磁干扰,具有低功耗、低噪声、低成本等优点使数据能在差分传输线或平衡电缆上以几百兆比特/秒的速度传输[2],因而广泛应用于高速信号传输的场合中。在基于PCI总线的数据采集卡对LVDS数据接收过程中,底层板卡收到的每一帧数据通常是以中断方式通知上位机来进行读取。在某些工程项目中,上位机不仅要完成数据存储而且还要对数据进行实时解析显示,当要接收的数据量很大,数据流很快时,经常出现上位机来不及响应底层板卡中断而导致数据丢失。针对这一问题,本文设计了一种大容量LVDS数据采集卡,在板卡上增加了数据存储模块,既满足在采集数据的过程中能够对数据进行实时解析显示也保证了所采集的数据能够被无丢失地存储下来。

1 PCI总线数据采集卡概述

本文所设计的基于PCI总线无时钟LVDS数据采集卡主要接收产品发送过来的两通道无时钟LVDS数据。按功能该板卡可分为LVDS数据的接收模块,基于NAND-FLASH的大数据量存储模块和PCI总线接口模块。在采集数据的过程中,不需要上位机对数据进行存储,采集卡会将数据先存储在本地存储器中,同时底层板卡每隔五帧数据以中断的方式通知上位机读取一帧数据进行实时解析显示。等到本次数据接收完毕后,上位机再从底层板卡的存储器中将接收到数据读取上来进行文件存储和后续的分析。

2 系统硬件设计

2.1 硬件总体设计

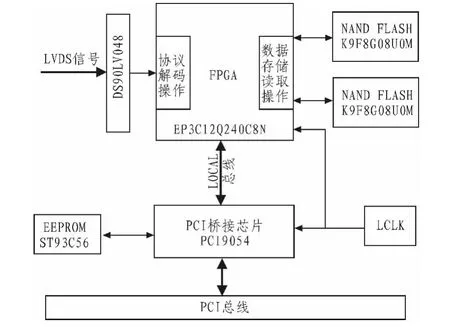

基于PCI总线LVDS数据采集卡硬件总体设计如图1所示。

图1 系统硬件结构图Fig.1 Structure diagram of the hardware system

本数据采集卡以CycloneⅢ系列FPGA为核心构建,通过PCI-9054桥接芯片实现本地总线与PCI总线的通信,采用LVDS信号接收芯片完成差分信号到单端信号的转换,数据存储模块使用NAND-FLASH来实现。利用FPGA控制硬件的总体时序逻辑,完成对LVDS数据的采集、存储以及上传操作。板卡硬件实物如图2所示。

图2 数据采集卡实物Fig.2 Physical map of data acquisition card

2.2 数据接收模块设计

数据接收模块采用DS90LV048芯片将差分LVDS信号转换成单端信号输入到FPGA,该芯片具有4路转换通道,最高转换速率可达400Mbps。DS90LV048每路接收通道接有100欧的终端匹配电阻进行阻抗匹配。通过FPGA内部的协议解析模块完成串行信号到并行数据的转换,进而实现LVDS数据的采集和存储[3]。

2.3 数据存储模块设计

该模块采用两片型号为K9F8G08U0M的NAND-FLASH实现本地采集数据的存储,K9F8G08U0M具有1Gbyte的数据存储容量,数据线与地址线复用,并行数据传输,除了8路I/O引脚与FPGA直接相连外,控制引脚如CE_等均通过电阻上拉后再与FPGA相连。

2.4 PCI总线接口设计

PCI总线接口模块采用FPGA与PCI-9054桥接芯片来实现PCI总线和局部(Local)总线之间的信息传递。PCI-9054提供了PCI,EEPROM,LOCAL总线3个接口,其作为桥接芯片在PCI总线与LOCAL总线之间传递信息,既可以作为2个总线的主控设备去控制总线也可以作为2个总线的目标设备去响应总线。本采集卡的PCI-9054工作在C模式下,芯片上的模式选择引脚MODE[1:0]都置低,在该模式下PCI总线中的地址线与数据线被分开,编程控制较为简单。Local总线即为PCI-9054与FPGA互联部分,FPGA需要配合LOCAL总线信号,产生相应的时序,实现读写功能[4]。其中重要的通信引脚有LA[31:2](地址)、LD[31:0](数据)、LHOLD(总线请求)、LHOLDA(总线)应答,LADS#(地址周期开始)、READY#(局部总线准备好)、LINT#(局部中断)等。PCI-9054内有两路DMA数据传输通道,可以使数据在PC机与PCI板卡之间进行高速传输[5]。本文所设计的LVDS数据采集卡即采用DMA数据传输方式来实现本地存储数据的快速上传。

PCI-9054芯片上电的时候要从外部EEPROM读取数据信息来配置内部寄存器、板卡的硬件资源要求以及选择PCI-9054的工作方式,因此EEPROM的配置信息是十分必要的[6]。本文所设计的LVDS数据采集卡的EEPROM选用ST93C56芯片,PCI-9054的配置方式为数据总线32位宽度,支持DMA数据传输方式,分配地址空间大小为4M。

3 FPGA内部各功能模块的开发

本采集卡的核心单元FPGA采用Verilog语言进行开发[7],按照功能分为数据采集、数据存储、总线控制3个功能模块,通过编程实现对各个功能模块的调用[8]。FPGA内部功能模块如图3所示。

图3 FPGA内部各功能模块Fig.3 Function modules inner FPGA

为了防止数据丢失,各个模块之间的数据在传输时都通过FIFO进行缓冲,所以本采集卡在FPGA内部开辟了3个用于数据缓存的FIFO。分别是数据直接上传FIFO,数据存储FLASH FIFO和FLASH数据上传FIFO。每个FIFO的容量都是两帧数据。当数据从接收模块向存储模块传输时要经过数据存储FLASH FIFO进行缓冲,当数据从接收模块向上位机传输时由数据直接上传FIFO对其进行缓冲,当数据由FLASH芯片向上位机传输时则通过FLASH数据上传FIFO进行缓冲。

3.1 无时钟LVDS数据接收模块的开发

根据采集卡的设计要求和目的可知,需要接收的LVDS串行数据没有时钟及相应的同步信号,传送过来的只有5 Mbit/s的串行数据,数据以字节为单位,每个字节共十位,包括1位起始位,8位数据位和1位停止位。发射端以固定周期发送一帧数据,每帧数据的开始处设有帧头。因此数据采集功能可分为字节提取与数据判断传送两部分。字节提取部分将传送过来的串行10 bit数据转化成8 bit字节数据,数据判断与传送部分将采集到的字节数据进行判断,如果检测到帧头就开始一帧数据的向外传送存储操作,直到传完一帧数据为止。

字节提取部分:传送过来的数据是5 Mbit/s,板卡采用40 M时钟,所以要对本地时钟进行分频产生5 M的采样时钟,由于发送端时钟与本地时钟不同,采用本地产生的时钟会产生累积误差,导致采集到的数据错位。因此采集卡的采集时钟每个字节同步一次,用本地的40 M时钟来对起始位进行检测,如果检测到起始位则立即产生5 M的采集时钟用于后续的数据采集,在停止位取消采集时钟。本模块设有一个八位的串并转换移位寄存器,当检测到起始位并且采样时钟启动时,该寄存器逐位接收到来的串行数据,同时依据采样时钟逐位右移,直到经过八个采样时钟遇到停止位为止,此时该寄存器的数据即为接收到的并行数据。为了防止毛刺信号的干扰导致对一字节起始位的误判或漏判,每次检测到一个字节的起始位后再进行采集检测一次,连续两次采到的起始位电平一致则确定是有效起始位,进而产生采样时钟进行采集。

数据判断与传送部分:当数据采集部分采完一字节数据后,会以标志位的方式通知数据判断与传送部分进行帧头判断,如果判断到帧头则认为一帧数据到来,对后续接收到的数据均传进数据存储FLASH FIFO中,直到传完一帧数据为止,然后等待下一帧数据的到来重新判断帧头。同时按照设计要求,为了减轻上位机的负担,底层板卡每接收到五帧数据向上位机传送一帧数据来进行实时解析显示。因此该模块设有一计数器,对接收到的帧数进行计数,当收到五帧数据时,在将一帧数据传送到数据存储FLASH FIFO中的同时也传进数据直接上传FIFO中,并通过中断通知上位机以DMA方式从数据直接上传FIFO中读取数据进行实时解析显示。

3.2 数据存储模块的开发

数据存储模块实时检测数据存储FLASH FIFO中是否有一帧数据存在,如果有则将一帧数据存入FLASH芯片中。当数据采集结束,上位机要读取FALSH芯片中的数据时,该模块也要检测FLASH数据上传FIFO是否为空,如果为空则从FLASH芯片中取出两帧数据存入到FLASH数据上传FIFO中,并以中断的方式通知上位机来进行读取,当FLASH数据上传FIFO又为空时,数据存储模块继续向其传送数据,直到接收的所有数据都被上位机取走为止。因为NAND-FLASH本身存在坏块问题,所以每次上电后该接口模块首先对硬件进行一次坏块搜索,在后续的操作过程中将坏块屏蔽掉。

3.3 总线控制模块的开发

总线控制模块接收来自上位机通过PCI-9054发送过来的指令进行相应的操作,同时配合上位机进行数据的DMA传输操作,该模块循环查询LADS#信号,当其为低时说明PCI总线对本地发起总线操作,如果LOCAL端完成相应的指令操作或要上传的数据已准备好就及时给出READY#信号释放总线。

4 系统调试

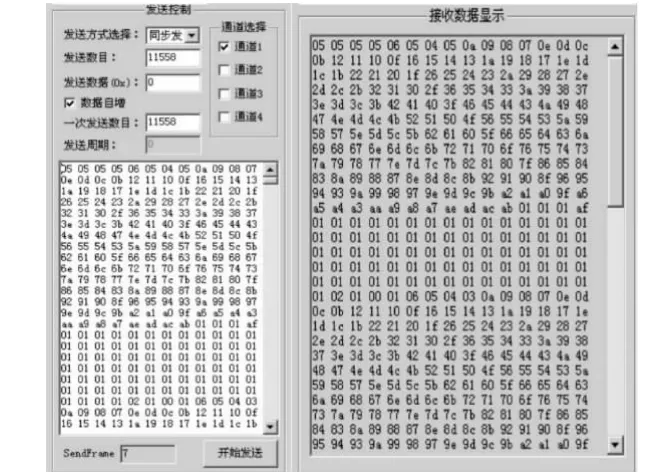

为了验证板卡功能,采用一块无时钟LVDS数据发送板卡与设计的无时钟LVDS数据接收板卡相连,发送板卡以固定周期发送一帧数据,数据的格式按照工程协议要求设定。观察接收板卡测试界面显示接收的数据。试验板卡连接如图4所示。

图4 无时钟LVDS数据接收试验Fig.4 Experiment of receiving non-clock LVDS signal

测试结果如图5所示:从实验结果可知接收数据显示界面的显示结果和发送板卡的发送数据内容完全一致,说明本采集卡能够很好地接收无时钟LVDS数据。

图5 实验结果Fig.5 Experiment of receiving non-clock LVDS signal

5 结 论

文中设计了一种基于PCI总线的无时钟LVDS数据采集卡,该采集卡结构紧凑,工作稳定,并且在该板卡的基础上对无时钟LVDS数据接收问题进行了分析研究,通过每字节同步接收时钟的方式保证了接收数据的准确性,板卡上自带的大容量存储器即使在上位机负担较重的情况下仍能保证数据的无丢失接收,该板卡可广泛应用于航空测控领域。在教学试验中,学生可利用该板卡学习verilogHDL语言对FPGA的开发及PCI总线的相关操作,有助于提高自身的专业技能。

[1]于劲松,李行善.美国军用自动测试系统的发展趋势[J].测控技术,2001,20(12):1-3 YU Jing-song,LI Xing-shan.Future trends of U.S.Military ATS[J].Measurement&Control Technology,2001,20(12):1-3.

[2]宋千.高速数据采集系统理论与实现技术研究[D].长沙:国防科技大学,2001.

[3]黄晓敏.LVDS驱动器电路设计及其硬件实现[D].武汉:华中科技大学,2004.

[4]李贵山,陈金鹏.PCI局部总线及其应用[M].西安:西安电子科技大学出版社,2003.

[5]PCI-9054 Data Book Version 2.1,PCI 9054 Data Book[S].U.S.:PLX,2000

[6]伊勇,李宁.PCI总线设备开发宝典[M].北京:北京航空航天大学出版社,2005.

[7]夏宇闻.复杂数字逻辑系统的Verilog HDL设计技术和方法[M].北京:高等教育出版社,2000.

[8]褚振勇,翁木云.FPGA设计及应用[M].西安:西安电子科技大学出版社,2002.