一种低功耗,高性能微处理器复位芯片的设计

吴桐,张涛

(武汉科技大学 信息科学与工程学院,湖北 武汉 430081)

随着CMOS IC朝着低功耗[1],低工作电压,高性能高集成度方向发展。为了保证系统在复杂的条件下能稳定性的工作,电源电压检测[2]电路必不可少。文中研究一种低功耗,高性能复位芯片,其高可靠性的复位特性大大提高了系统的稳定性。设计上保证在宽温度范围内当电源电压掉电和上电瞬间实现复位,内置分频电路连接级数实现复位时间可调。该芯片采3个管脚SOT封装,工作电流仅有10μA,功耗低,成本低,性能高,电路结构简单且工艺容易实现,广泛应用于各类工业控制类系统中。RESET为恒高电位。

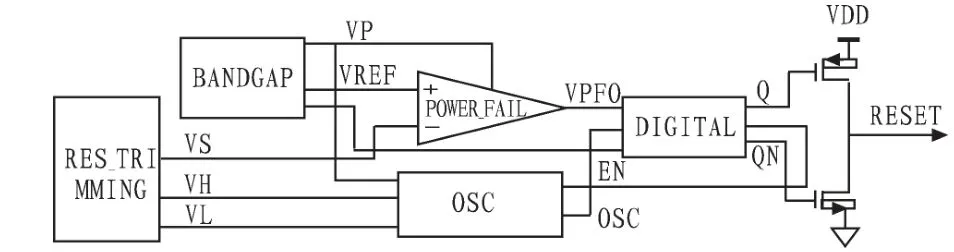

图1 MCU复位芯片内部结构图Fig.1 The MCU Reset chip internal structure block

1 芯片内部系统框架结构图

具体工作原理如下:在电源上电瞬间,由内部数字控制逻辑电路产生一个使能信号,使内部张弛振荡器振荡,振荡信号通过内部数字控制逻辑电路的分频电路产生分频信号,此时整个系统输出端为一个高电平信号驱动NMOS,PMOS管,输出实现上电复位。经过一段时间以后,分频电路分频结束,使整个数字控制逻辑电路输出翻转,输出一个低电平信号驱动NMOS,PMOS。整个系统正常工作,输出信号消失,当整个系统工作电压由于某种原因下降时,如果电压值下降到门槛电压以下,内部电阻调整电路采样电源电压按比例线形比例下降,而带隙基准[3]电压的随电源电压变化几乎保持不变,此时内部掉电检测比较器[4]输出产生翻转信号送入内部数字控制逻辑电路,输出控制信号使振荡器[5]振荡,内部分频电路[6]开始对振荡信号进行分频计时,此时输出复位,经过一段时间以后分频结束,数字控制逻辑输出发生翻转,输出复位信号消失,输出端为恒高,系统恢复正常工作模式。此芯片各输入,输出引脚处均有ESD[7]保护电路,避免静电放电击穿。

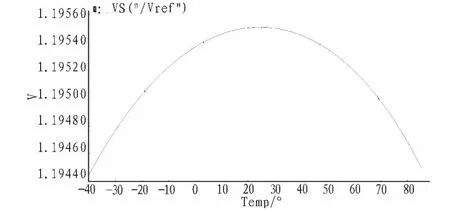

2 带隙基准电压源的原理和特性分析

复位芯片正常工作,内部各个电路模块需要一个稳定的偏置信号提供直流工作点,并且该信号工作特性具有良好的抑制PVT特性的能力。内部偏置电路能提供一个随工艺,电压,温度变化较小的稳定信号源,带隙基准可以实现这个功能。

带隙基准的基本原理:如果将两个具有相反温度系数的量以适当的权重叠加,结果可以得到零温度系数的信号量。由大量的实验可以得到结论:双极性晶体管的基极-发射级电压即PN结的正向电压具有负温度特性。而如果当两个双极性晶体管工作在不相等的电流密度下,那么基极-发射级电压的差值就与绝对温度成正比而呈现正温度特性。

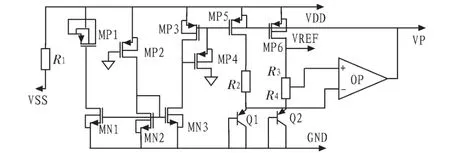

由图2知:双极性晶体管Q1的发射结面积是Q2的N倍,由运放输入端虚短特性知A,B两点电压被钳制相等,则可得以下表达式:

图2 复位芯片内部带隙电压基准源Fig.2 Reset chip internal bandgap voltage reference source

对带隙基准电路进行数学分析,由于VBE的温度特性一般已知或者可以进行线形抽象逼近,而热电压VT的温度特性一般已知,故通过调节N,R3,R4的值可以设置合理的温度系数点。VREF一般为1.2 V左右,零温度系数点一般在室温附近。图2中MP2,MN2,MN3,MP4组成启动电路,避免上电瞬间电路由于工作点设置不合理而进入简并点异常状态。MP2为倒比管,减小正常工作后之路的功耗。对MP4管,上电启动瞬间MP3管不导通而MP4管栅压为低,MP4管导通并且漏端电压被拉低,同时MP3,MP5,MP6组成的电流镜开始工作。电路启动以后MP3管工作,MP3漏端电压使MP4管的栅端电压变高,MP4断开,整个启动过程结束。启动速度很快,很稳定,采用Cadence Spectre对电路进行仿真,采用CSMS035标准CMOS工艺库。曲线如下:

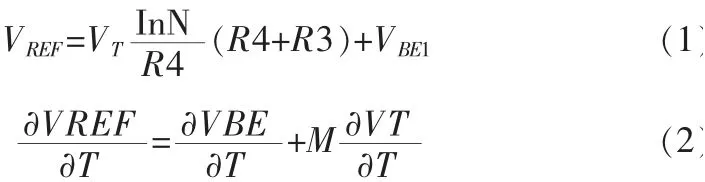

由图3可知:在整个温度范围内,电压变化最大值不到1 mV温度系数只有10ppm抑制温度变化能力很好。

图3 带隙基准源温度特性曲线Fig.3 Bandgap reference temperature characteristic

由图4可知:电源受到噪声干扰时,在很宽的频率范围内,基准对电源噪声的抑制程度很好,尤其在低频时1KHZ时电源抑制比达到-60 dB,整个频率范围内电源抑制比很高,通过合理设置OP补偿电容可以保证整个基准的环路稳定,不会出现自激振荡。

图4 带隙基准源的电源抑制噪声特性曲线Fig.4 Bandgap reference source of power suppress noise characteristic

3 内部张弛振荡器的原理和特性分析

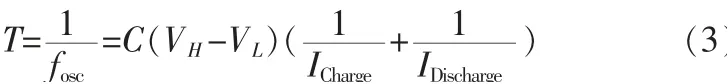

所谓张弛振荡器,就是利用恒流源[8]对电容进行充电,使电容极板聚集电荷,电压升高,当电压超过一个高门槛值时通过整个环路的开关控制电路控制放电电路对电容进行放电,此时电容极板放电,电压下降到低于一个低门槛电压时通过整个环路的开关控制充电电路再次对电容进行。这样,电容的极板电压就在两个电压门槛值之间不断的上升,下降,形成张弛锯齿波电压信号。然后通过整形电路形成张弛振荡方波信号。

由图5可知:VP为基准电路提供的一个偏置信号,通过MP1管转换为电流然后通过电流镜MN2,MN3,MN8,MP2,MP3,MP6等形成一定的充放电电流,具体工作原理如下:

图5 张弛恒流充放电RC振荡器Fig.5 Relaxation constant current charging and discharging RC Oscillator

EN为使能控制信号,当且仅当EN=0低电平时,控制开关管MN1,MN14关断,振荡器正常工作,否则OSC输出为恒定高电位。初始时,电容C上极板电荷为零,处于低压状态。此时电压VC小于VH,OSC输出为低,MP6,MP7均导通,电流IMP6对电容C进行充电,电压VC逐渐上升,当VC大于VH,输出OSC电平翻转,MN7,MN8导通,电容通过MN7,MN8进行放电,放电电流为IMN8,电压逐渐下降。当VC小于VL时,输出OSC再度翻转,OSC输出为低,再次对电容充电。如此循环,在电容C上获得锯齿波,通过整形电路以后形成方波。

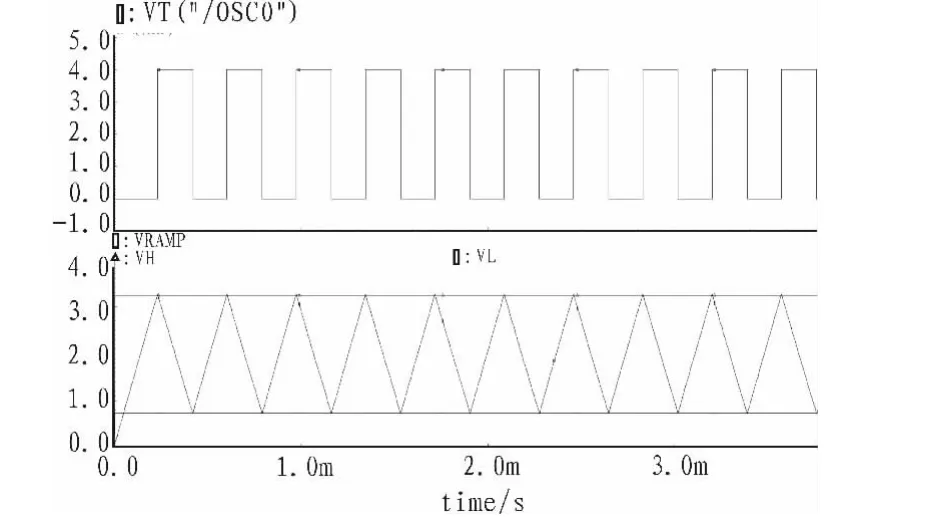

振荡器周期数学模型:仿真后,振荡器曲线如如下:

4 内部数字控制逻辑电路

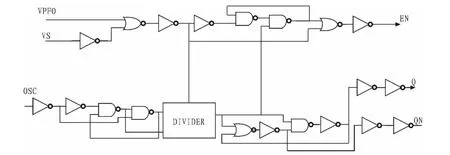

复位芯片内部的振荡器频率一般确定,但是复位时间针对不同应用场合时需要一定的调整,内部数字控制逻辑电路[9]就是实现这个调整的功能,内部的分频电路不同的级联个数可以实现不同的分频输出信号周期,即调整复位时间,然后通过逻辑控制电路对内部振荡器进行控制,保证上电瞬间系统复位,掉电以后系统复位,恢复正常后系统持续复位一定时间后进入正常状态。

图6 振荡器输出OSC波形和电容上的张弛门槛电压,三角锯齿波电压Fig.6 The OSC output waveform,the relaxation threshold voltage of capacitor,triangular voltage

由图7可知:电源上电后,分频器输出为高电平,此时掉电比较器和VS信号均正常输出,EN为低电平,振荡器工作,产生振荡信号,然后进入分频器进行分频计时,此输出Q,QN均为高,输出复位信号RESET为低,经过一定时间以后,分频器输出翻转,QN,Q均为低,复位信号关断,正常工作,RESET输出恒高。

图7 复位芯片数字控制逻辑电路框架图Fig.7 Reset chip digital control logic circuit framework Figure

整个复位芯片进行系统仿真,包括上电瞬间和过程中电源掉电,整个系统工作电流。整个系统仿真波形如下。

由图8可知:整个复位芯片的掉电阈值电压为2.93 V,上电复位时间为5 ms(调整内部分频单元个数可以改变复位时间),正常工作时的工作电流仅为10μA,由于内部基准运放使用大电容补偿以实现高稳定性,大相位裕度,所以在掉电瞬间,系统时延约为270μs不影响正常工作。

图8 (自左向右)系统工作电流,掉电阈值电压,系统上电,掉电输出响应波形图Fig.8 Rhreshold voltage of power drops,Response of power on,power drop,Operating current

5 结束语

该复位芯片,内部电压基准源温度特性好,抑制电源噪声能力强,内部振荡其结构简单,频率比较稳定,掉电检测电路实现迅速掉电响应,内部数字控制逻辑电路产生一系列时序逻辑控制信号保证系统上电,掉电瞬间进行复位,并且保证系统电源电压恢复到门槛电压以后再进行一段复位时间进行平滑过渡。整个芯片结构简单,功耗低,性能强,工艺实现性好,成本较低,已成功流片并通过终测。现在已经应用于工业控制系统中,封装简单,工作温度范围广,复位精度高。

[1]陈力颖.CMOS低功耗电路设计[M].北京:科学出版社,2011:103-122.

[2]张飞龙.开关电源的电压检测与控制[D].西安:电子科技大学,2010.

[3]唐广.低温度系数高电源抑制比的基准源设计与应用[D].西安:电子科技大学,2010.

[4]李杰,吴光临.一种低失调CMOS比较器设计[J].电路与系统学报,2007,12(3):27-32.LI Jie,WU Guang-lin.A Design of low offset CMOS comparator[J].Circuit and Systems,2007,12(3):27-32.

[5]张睿.适用于LED电流驱动的高性能张弛振荡器的设计[D].武汉:华中科技大学,2008.

[6]包志华,景为平.3.75GHz 0.35umCMOS1:4静态分频器集成电路设计[J].南京邮电学院学报,2001(4):91-94.BAO Zhi-hua,JING Wei-ping.3.75GHz 0.35umCMOS1:4static frequency divider IC Design[J].Nanjing University of Posts and Telecommunications,2001(4):91-94.

[7]王怡飞.CMOS片上ESD保护电路设计研究[D].合肥:中国科学技术大学,2009.

[8]张春华.CMOS亚阈值偏置恒流源的分析与设计[J].电子设计工程,2007,16(5):21-26.ZHANG Chun-hua.CMOS sub-threshold analysis and design of bias constant current source[J].Electronic Design Engineering,2007,16(5):21-26.

[9]康松默.CMOS数字集成电路[D].北京:电子工业出版社,2009:243-275.