一种高速全数字卫星信号模拟源平台❋

马力科

(中国西南电子技术研究所,成都610036)

一种高速全数字卫星信号模拟源平台❋

马力科❋❋

(中国西南电子技术研究所,成都610036)

提出了一种高速全数字卫星信号模拟源的平台实现方案,该方案以在线可编程门阵列(FPGA)和高速模数转换器(DAC)为平台设计核心,采用了DAC与FPGA高速接口设计、并行编码调制设计、数字白噪声生成设计、速率分级设计、DSP接口设计等设计手段,实现了高速编码和并行调制,完成了高速DAC全数字中频信号直接合成、实时宽带信道模拟、超宽带数字高斯白噪声生成等技术的研究与工程实践。

卫星信号模拟源;高速DAC;高速数字信号直接合成;数字高斯白噪声

1 引 言

无线宽带、高速数据传输技术是星地无线测控通信系统的核心技术之一,随着侦查、遥感、探测等卫星测控通信系统业务的不断增长,越来越多的卫星采用更高传输码速率,如美国Quick Bird下行码速率高达320 Mb/s,印度IRS-P6和欧空局Envisat-1卫星的下行码速率也分别达到了105 Mb/s和100 Mb/s。日本超高速因特网卫星可实现最高速率1.2 Gb/s的超高速双向数据通信。

由于高速数据传输设备传输中心频率高、带宽宽,通常的实现方法是采用大规模可编程门阵列(FPGA)产生基带信号,通过宽带低通滤波,经正交调制的方式上变频到高中频,这种实现方式存在IQ双路一致性的问题,对模拟电路设计要求较高。

目前,国内卫星数传技术通常采用较为成熟的低中频数字调制和信道模拟变频技术,但数据带宽和数据传输速率十分有限[1]。

国内也有一些采用通用芯片实现的高速数传设备[2],这些设备主要由调制器单元、解调器单元和接入单元组成,并可完成多种调制方式,可提供多种编码制式,支持多种卫星制式,但不支持用户自定义的UQPSK等调制方式,且设备组成复杂,对模拟射频电路、微带电路等模拟硬件电路设计的要求很高。而国内市场上可购买的信号源仪器可产生几种常用的调制波形,但模式有限,且数据带宽不超过50 MHz。任意波形发生器[3]可产生的模式多、编程灵活、数据注入方便,但通常采用的方式是通过如MATLAB[4]等软件直接计算输出信号并编译、循环播放,不能适应高实时性和低延时等系统要求。

由于国内卫星测控通信系统用户自定义模式多,而上述设备又不可直接用作模拟源设备的要求。需要重新设计出一种可具备多种调制模式、多种码型,码速率连续可变,实时宽带信道模拟,数字高斯白噪声生成等功能的全数字卫星信号模拟源设备。

本文提出的一种全数字卫星信号模拟源设计方法,通过FPGA高速并行处理编码调制合成中频信号,高速数模转换器(DAC)直接产生宽带模拟中频调制信号,并由数字信号处理器(DSP)完成多种调制模式的参数计算和配置管理,能满足用户的需要。

2 硬件平台电路设计

2.1 硬件平台组成

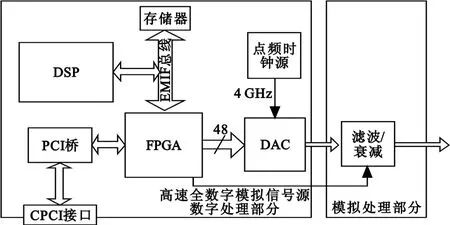

高速全数字卫星信号模拟源采用了全数字的调制方式,电路组成简单。要数字直接产生中频信号频率到吉赫、数据带宽为几百兆赫的信号,根据Nyquist采样定理,需选用采样速率至少大于2 GHz的DAC芯片,同时在模拟前端添加宽带滤波器输出。由于所有多模式多编码的数字运算均需动态配置实现,需选用大规模的可编程器件FPGA实现。同时,选用DSP作为参数计算及主控模块,周边组件接口PCI桥芯片作为PCI接口。

高速全数字卫星信号模拟源系统组成框图如图1所示。

图1 系统组成框图

硬件设计主要芯片包括一片Xilinx Virtex-5大规模FPGA XC5VLX220以实现各种模拟逻辑,一片高速DAC MD652D[5],一片DSP TMS320C6416作为参数主控器,一片PCI桥芯片PLX9656作为PCI接口以及部分外围电源和接口芯片。FPGA通过DAC产生各种调制信号;DSP可对FPGA进行各种参数配置,PCI桥片提供CPCI接口,通过监控界面对参数进行控制。

2.2 高速DAC与FPGA接口实现

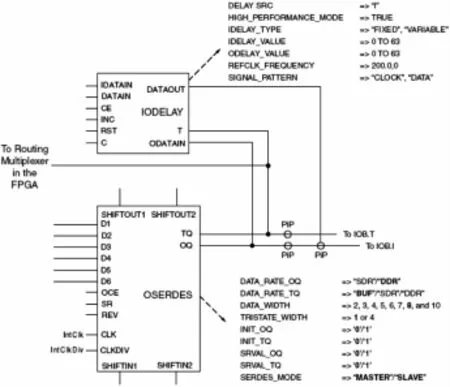

高速DAC的使用关键在于实现与其连接的高速数据接口。由于普通的FPGA IO管脚不能输出速率高达1 Gb/s的高速数据信号,需使用FPGA的高速接口,而一般专用的高速IO接口数量有限,不能提供48对IO接口,故采用Xilinx FPGA[6]内部的OSERDES高速串化器模块。OSERDES高速串化器模块可配置于任何一对差分输出管脚,资源丰富,应用非常方便。它可将FPGA内部低速并行信号串化为高速串行信号,OSERDES模块最高可支持3.2 Gb/s数据速率的输出。

FPGA OSERDES模块组成如图2[7]所示。

图2 FPGA OSERDES模块组成图

高速接口实现的另一个关键在于时钟的选取。采用4 GHz高速时钟作为DAC的采样工作时钟,DAC芯片将输出八分频时钟信号反向输入FPGA的内部模拟锁相环(PLL),PLL锁定时钟作为全局时钟并送到BUFG上,作为高速输出接口OSERDES模块的输出接口时钟,同时将OSERDES配置为DDR模式。此外,使用PLL分频时钟作为OSERDES模块的输入接口时钟和FPGA内部工作的主时钟信号,FPGA内部大部分逻辑、接口、编码算法均运行在内部主时钟频率上。OSERDES模块将内部8路并行信号按DDR的方式串化为1路高速LVDS数据,并作为DAC的一个数据位输出。

该部分设计需保证硬件的数据和时钟链路等长,保证FPGA内部时序的一致和规范。同时,高速DAC还要注意相位对齐。

FPGA与DAC接口设计框图如图3所示。

图3 FPGA与高速DAC接口框图

3 FPGA算法设计实现

3.1 算法实现

FPGA内部算法主要包括两部分,即信号波形产生和数字白噪声产生。

根据监控参数的控制,FPGA内部信号波形生成流程依次为:

(1)数据成帧、存储:接收外部注入的数据,或者自己生成监控要求的数据,按控制要求帧头和帧长,形成数据帧存放在存储器内;

(2)数据读取:在数据时钟生成单元产生的时钟驱动下,将存储器中的数据读出;

(3)数据时钟生成:生成不同速率的数据时钟,并可以模拟数据的多谱勒频率动态;

(4)RS编码:生成要求的RS编码格式;

(5)加扰:按控制的多项式和初相进行数据加扰;

(6)码型变换:根据要求的码型进行码型变换;

(7)卷积编码:生成Viterbi编码格式;

(8)差分编码:按格式生成差分编码后数据;

(9)基带调制:将发送序列按照指定调制方式、差分编码类型进行星座映射,产生基带调制信号。

(10)并行成形滤波:以多相滤波为基础,利用多个分解的子滤波器实现并行滤波,每个子滤波器分别完成不同相位的滤波运算。

3.2 并行编码调制实现

采用高速DAC,在FPGA接口软件设计上区别于传统的串行设计的方式,所有的编码数据及调制数据均并行产生。

本方案采用两级串化的方式实现数据并行。前一级是FPGA的OSERDES将每一路8位并行数据串化为高速DAC的一个通道,每一时刻数据由8个支路并行产生;后一级是高速DAC将4路48位并行数据信号串化为1路12位数据送到数模转换模块。即在FPGA中总共32路并行,每路12位,总共384个数据位,经两级串化到1路12位数据。

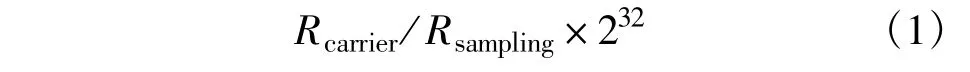

由于载波频率是可以确定的,对32路的每一路来讲,每一路信号的相位差是一个固定值,载波变化是有规律的。故采用DDS产生32个输出查找表,载波信号均可通过查表的方式得到每一路相差固定的初始相位,再完成对载波信号的调制。根据公式(1),可确定每个DDS的相位关系:

式中,Rcarrier为载波速率,Rsampling为数据采样率。

根据调制码速率的不同,根据公式(2),可计算调制信号的翻转点:

式中,Rdata为数据速率,Rsampling为数据采样率。

图4说明了载波调制信号翻转点的计算确定。

图4 载波及调制信号调制波形示意图

3.3 数字白噪声生成

在FPGA中,并行采用了32路的Box-Muller算法,得到多路并行高斯白噪声带宽信号,并通过4 GHz高速DA采样产生模拟的高斯白噪声信号,与32个DDS产生的载波信号在FPGA内部完成数字调制,并通过4 GHz高速DA采样产生模拟的高斯白噪声信号。

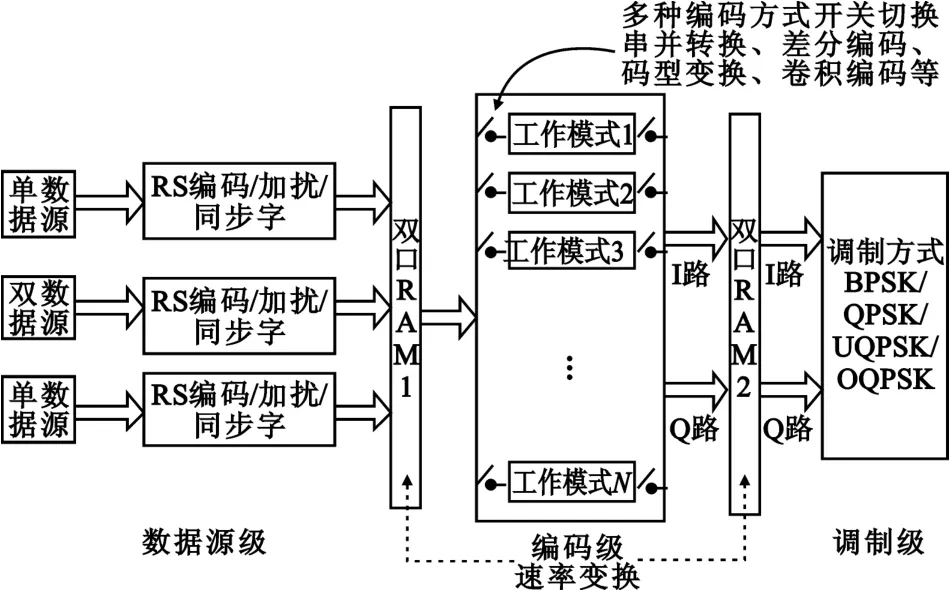

3.4 速率分级实现

高速全数字卫星信号模拟源在软件设计上的另一个难点在于要兼容多种卫星编码模式,且每种模式的操作流程不一致,编码后速率并不一致。本方案针对这一难题在编码和数据输出过程中添加了两级双口RAM,将前后按速率不同分为三级进行分别设计,双口RAM用于不同数据速率之间的接口和前后编码数据的隔离。

两级DPRAM分别用于以下两个方面。

(1)由于要兼容多种编码模式,多种模式的结构组成各有不同。包括有单、双数据源的不同,有无差分编码的不同,有无串并转换模块的不同,导致从数据源读数与编码的速率接口有多种速率,为了兼容多种模式,在此处需添加一个双口RAM作为前后编码数据的隔离,保证数据的无缝连接。这是第一级速率隔离分级。

(2)由于码速率要求在200 Mb/s内连续可变,而FPGA内部主工作时钟保持不变。因此,需通过DPRAM进行隔离,满足内部主时钟连续向外读数,而写入数据在将DPRAM写满后将CE拉底,前一级编码工作暂停。在DPRAM读数端将RAM中数据读空时,将CE拉高,前一级编码继续工作。这是第二级速率隔离分级。

通过隔离,使得从DPRAM中输入数据速率固定,而它的数据输出端速率可以连续可变。由于输入端数据速率始终高于输出端速率,必然存在RAM空间存满的情况,采用调制信号数据EN有效位机制,当空间存满时,暂停前级运算,并保持停止的状态,等待空间读空,再重启动运算。对于后一种问题,同样可以通过隔离,将多种数据速率进行前后级的无缝连接。

FPGA多级速率隔离和分级设计原理框图如图5所示。

图5 FPGA多级速率隔离和分级实现原理框图

3.5 DSP接口实现

高速全数字卫星信号模拟源的DSP芯片在模块内完成接口功能、命令解析、数据注入接口等。

DSP上电加载后,首先进行硬件的初始化,包括寄存器的初始化和中断信号的使能;然后配置FPGA,使之工作在默认的工作模式,包括对FPGA内部配置寄存器设置为默认值和对FPGA默认工作状态的数据注入等。完成这些操作后进入while(1)死循环,处于等待状态,等待中断的发生。有两种类型的中断需要进行处理,其一是DSP将模块的工作状态向监控界面做周期性的上报,表明当前工作状态;其二是DSP响应由监控界面下发的PCI数据中断,将在主函数中完成包括配置命令解析或数据注入。若为配置命令,对之进行解析,得到相应的配置参数,并置入FPGA,使模拟源工作在新的模式;若为数据注入,数据从PCI总线上得到,并置入FPGA数据源的RAM空间,此时需要对FPGA完成一次复位,保证数据不会与前面的数据重在一起。当FPGA切换完成后将使用新注入的数据进行下一次调制。完成以上处理后DSP向监控软件进行状态上报,表示已工作在新的状态下,并回到等待状态,等待下一次中断发生。DSP工作流程如图6所示。

图6 DSP主工作流程图

4 模拟源硬件实现与测试指标

模拟源硬件实现局部图如图7所示。

图7 模拟源硬件局部图

对该高速全数字模拟信号源设计方案进行实际测试,实现的主要指标包括以下几个方面。

(1)宽带实时信道模拟,可实现BPSK、QPSK、OQPSK、UQPSK等多种调制方式;实现输出中频频率不低于400 MHz、码速率不低于200 Mb/s以内连续可变的模拟信号;实现NRZ-L、M、S,Biφ-L、M、S,格雷差分等多种码型;输出模拟信号电平动态范围不小于50 dBm;输出模拟信号杂散大于60 dBc。

(2)误码率测试性能:在200 Mb/s码速率的情况下,测试EVM为6.5。

(3)实现的高斯白噪声在几百兆频率范围内不平坦度不大于1 dB。

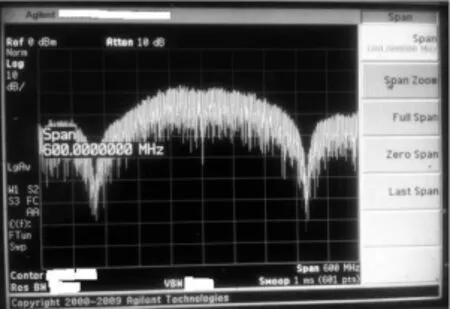

模拟源输出的一种宽带QPSK信号频谱图如图8所示。

图8 模拟源输出频谱

5 结束语

本文介绍的是一种高速全数字卫星信号模拟源的平台实现方案,依照软件无线电理论所有处理均由高速ADC、DAC转换到数字域进行处理的设计思想,在工程上成功实践了以FPGA、高速DAC为平台设计核心,采用全数字的方式实现整个编码调制的过程,并通过高速DAC合成模拟信号的设计方法,突破了高速数字信号直接合成、实时宽带信道模拟、超宽带数字高斯白噪声生成等设计技术难题,实现了高速并行编码和调制、高速DA接口及高速信号完整性设计等技术,在国内尚未见发表过的应用,为下一步对更高速率的数据传输研究提供了参考。本方案已成功应用于工程,且设计已申请国防专利。

[1]谢剑锋,谢文楷,汪远玲.综合基带全数字测试信号源[J].电子科技大学学报,2004,33(5):539-542.XIE Jian-feng,XIEWen-kai,WANG Yuan-ling.Reserch of All Digital Test Signal Source of Comprehensive Baseband[J].Journalof University of Electronic Science and Technology of China,2004,33(5):539-542.(in Chinese)

[2]吴兵,王忠华,顾何方.基于软件无线电的卫星通信模拟源的实现[J].现代电子技术,2010,17(1):27-29.WU Bing,WANGZhong-hua,GUHe-fang.Implementation of Silulation Source for Satellite Communication Based on SR[J].Modern Electronic Technique,2010,17(1):27-29.(in Chinese)

[3]封治华,杜改丽.FPGA实现的任意波形发生器的设计[J].电子设计工程,2010,18(10):164-168.FENG Zhi-hua,DU Gai-li.Design of arbitrary waveform generator based on FPGA[J].Electronic Design Engineering,2010,18(10):164-168.(in Chinese)

[4]Garcia T R.Communication Signal Analysis Using MATLAB[C]//Proceedings of 1996 Frontiers in Education Conference.Salt Lake City,UT:IEEE,1996:616-619.

[5]Euvis Corporation.MD652D Data Sheet[EB/OL].(2009-01-23)[2009-04-15].http://www.euvis.com/products/ic/ds/MD652D.pdf.

[6]Xilinx Corporation.Virtex-5 User Guide,UG190(v3.1)[EB/OL].2007-11[2009-04-18].http://china.xilinx.com/support/documentation/data-sheets/c-ds100.pdf.

[7]Marc Defossez.Virtex-5 FPGA Interface for Fujitsu Digitalto-Analog Converters with LVDS Inputs[EB/OL].Xilinx XAPP873(v1.0),2008-05[2009-04-18].http://china.xilinx.com/support/documentation/application-notes/xapp873.pdf.

马力科(1982—),男,四川成都人,2007年获工学硕士学位,现为工程师,主要从事通信与信号处理处理平台及嵌入式系统开发工作。

MA Li-ke was born in Chengdu,Sichuan Province,in 1982.He received the M.S.degree in 2007.He is now an engineer.His research concerns communication and signal processing,embedded system development.

Email:mcdona-cn@163.com

A High-Speed Digital Satellite Signal Simulator Platform

MA Li-ke

(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

A high-speed digital satellite signal simulator solution is provided.This solution uses Field Programmable Gate Array(FPGA)and high speed Digital-Analog Convertor(DAC)as the core framework.DAC to FPGA high-speed interface design,parallel encoding and modulated design,digital white noise generation design,data rate graded design,DSP interface design technology are adopted.High-speed parallel encoding and modulation are realized.Intermediate Frequency(IF)digital signal direct synthesizion,real-time broadband channel simulation and ultra-broadband digital Gausewhite noise generation technology are practiced in project.

satellite signal simulator;high-speed DAC;high-speed digital signal direct synthesizion;digital Gausswhite noise

TN802;TN911

A

1001-893X(2013)03-0318-05

10.3969/j.issn.1001-893x.2013.03.018

2012-09-21;

2012-12-19 Received date:2012-09-21;Revised date:2012-12-19

❋❋通讯作者:mcdona-cn@163.com Corresponding author:mcdona-cn@163.com