极低电源电压和极低功耗的亚阈值SRAM存储单元设计

柏 娜 冯 越 尤肖虎 时龙兴

(1东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

(2安徽大学电子信息工程学院,合肥 230601)

(3东南大学移动通信国家重点实验室,南京 210096)

亚阈值区域电路是一种新兴的低功耗技术.该技术通过极大限度地降低系统电源电压至MOS晶体管亚阈值区域(Vdd

1 亚阈值SRAM存储单元设计

SRAM的芯片面积和电学特性很大程度上依赖于存储单元的组成结构和工艺指标.为满足高集成度要求,存储单元各组成晶体管普遍采用最小尺寸设计,这种设计方式使得各组成晶体管更易受工艺偏差的影响.在亚阈值区域时,由于噪声容限迅速降低,各种外界干扰和工艺偏差更会严重恶化小几何尺寸晶体管(特别是SRAM单元)的阈值电压Vth的稳定性.驱动电流和阈值电压的指数级关系使得单纯的调节晶体管尺寸满足良率需求的方式已不再适用.因此,存储单元结构设计成为亚阈值存储电路平衡读写操作、协调各失效率、满足设计良率要求的关键.驱动电流和阈值电压的指数级关系如下:

(1)

式中,n为亚阈值摆幅参数;η为DIBL系数;γ为体效应系数;VT为热电压,VT=kT/q,其值在室温下约为26 mV;Isub0是VGS=Vth,W/L=1条件下获得的特定电流;VGS为栅源电压;VDS为漏源电压;VSB为源体电压.

图1 带自适应限制泄漏电流机制的存储单元电路及其控制信号

本设计的可读性由缓冲电路(N5~N7和N6~N8)保证.缓冲电路可以在读操作过程中保护该存储单元内存储的信息不被破坏,进而扩展其读静态噪声容限.自适应泄漏电流关断管可以根据存储单元的操作瞬态动态地限制泄漏电流.为了保证在各工艺角下的稳定性并且减少动态操作(读/写操作)和静态操作时的泄漏电流,本设计采用可配置的控制字信号,如图1(b)所示.可配置的外部控制字线信号WL,WWL同时保证了本设计的可写性.上述结构使得本设计可以全部采用最小尺寸的晶体管以满足存储电路面积的约束,如表1所示.

表1 与其他文献中亚阈值存储单元的比较

2 自适应限制泄漏电流原理

自适应限制泄漏电流的原理是:亚阈值区域MOS晶体管的驱动电流随着VGS和晶体管的阈值电压Vth的差(器件过驱动电压)呈指数级变化,如式(1)所示.下面以写操作为例,描述本设计的自适应限制泄漏电流原理.

图2 写信号“0”至点的瞬态波形

晶体管的阈值电压计算公式如下:

(2)

式中,Vth0是衬底偏压为“0”时的阈值电压;VSB为源体偏置;2φF为表面势.

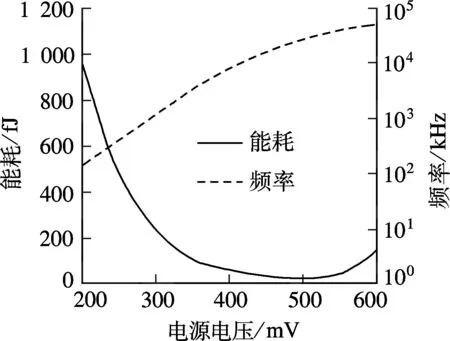

由式(2)可看出,若晶体管的源体(源极相对于衬底)电压小于“0”(VSB≠0),则|Vth|VSB≠0>|Vth|VSB=0,即该存储单元在写操作瞬间正常工作.一旦写操作完成,P3的漏源电流就随着|Vth|P3的增长呈指数级降低.同时,P4的VGS从“0”变为一个正值.根据式(1),P4的漏源电流也随VGS的增加呈指数级降低(对于PMOS晶体管开启状态要求VGS 图3 读、写和保持操作的模拟波形 综上所述,自适应切断管P3和P4可根据本设计的操作瞬态,动态地调整自身的运行状态进行限制泄漏电流的操作.在自适应限制泄漏电流的操作过程中,既无需额外附加辅助开关管帮助系统进入泄漏电流关断模式,也没有在位线上引入额外的负载,因此本文设计的亚阈值存储单元在获得泄漏电流降低的同时对动态功耗和读取时间无任何损耗. 在亚阈值区域,由于晶体管开启和关断电流比(Ion/Ioff)较小、负载电容大以及受工艺偏差的影响较大,因此如何确保足够的写操作裕度成为SRAM设计的一个难点.文献[11]通过在写操作过程中关断存储体的电源电压来提高写操作能力.但是,这也降低了其他未被选中存储单元在保持数据阶段的稳定性.文献[9]中采用反向短沟道技术增加MOS晶体管的驱动电流,考虑到存储体的大容量应用领域,该方法引入的大面积消耗十分严重.故本文采用增强的WL和WWL来替代门控电源技术和反向短沟道技术[9,11].相应的伪写(pseudo-write)问题可采用外围辅助逻辑来避免[12-13]. 图4 往点写“0”的瞬态波形 在亚阈值区域,采用单端读出结构的存储单元的读位线摆幅易受工艺偏差的影响,这使得后续逻辑部件很难识别出正确信号,导致设计失效.为解决该问题,本设计采用差分读出方式. 在保持操作期间,WL被置为“0”,WWL被上拉至250 mV.在此过程中,N3和N4处于开启状态.这样根据存储单元具体的存储信息,N3~N7或N4~N8将形成一个到地的直流通路,增强存有“0”节点的拉低电位能力.相应地,也保证了本设计的保持静态噪声容限. 图5给出了在相同条件下,10T[7]和本设计保持静态噪声容限的1 000次蒙特卡罗分析结果.从图5中可看出,与10T[7]存储单元相比,本设计的保持静态噪声容限更具优越性.这是因为在保持操作时,由于N3~N7或N4~N8所形成的一个下拉直流通路,使得本设计即使在存储单元最差工艺角(FNSP)的情况下,仍能保证较好的保持静态噪声容限. 图5 10T[7]存储单元与本设计保持静态噪声容限比较 图6给出了在充分考虑工艺偏差和器件失配的条件下,10T[7],ST[8]和本设计的静态泄漏电流和动态操作电流的分布.从图6中可看出,本设计的静态泄漏电流均值分别比10T[7]和ST[8]存储单元的静态泄漏电流的均值小9.0%和55.59%.10T[7]和ST[8]存储单元的动态有效平均电流分别为592.845 pA和224.567 pA. 图6 10T[7],ST[8]和本设计存储单元静态泄漏电流和动态操作电流的比较(总采样次数为1 000) 本设计在200 mV时动态有效平均电流为154.619 pA,明显小于文献[7-8]中的存储单元.这充分证明了相比于10T[7]的存储单元仅能减少静态操作时的泄漏电流,本设计能够同时减少动态操作和静态操作时的泄漏电流.与10T[7]和ST[8]存储单元相比,本设计具有以下特点:① 静态操作时泄漏电流的标准方差分别减少了90.0%和30.38%;② 动态操作时泄漏电流的标准方差分别减少了21.11%和58.78%.这说明,同样是亚阈值存储单元设计,本设计具有更好的工艺鲁棒性. 本文采用全定制实现方式,采用IBM 130 nm 工艺实现了一款256×32 bit的亚阈值存储阵列.整体面积为141.4 μm×352.6 μm,如图7所示.图8给出了200 mV电源电压条件下,存储阵列读、写、保持操作的波形. 图9给出了本设计的存储阵列在不同电源电压条件下的最大工作频率和能耗.图9中,在电源电压为200 mV条件下本设计的最大工作频率可达138 kHz.采用每周期翻转率为50%的随机输入向量进行功耗测试,可以得出在电源电压为200 mV时,本设计的总功耗(包括静态和动态功耗)是0.13 μW,为常规六管存储单元功耗的1.16%. 表2比较了本设计与常规存储单元及文献[7-8,13]中各存储单元的性能指标. 图7 亚阈值存储阵列的芯片照片(单位:μm) 图8 200 mV电源电压下存储阵列的工作波形图 图9 亚阈值存储阵列在不同电源电压条件下的能耗和最大工作频率 本文提出了一款能够在200 mV电源电压条件下正常工作的具有自适应泄漏电流切断机制的亚阈值存储单元.本设计在不提高动态功耗与不增加性能损失的前提下,可同时降低动态操作(读/写操作)和静态操作时的泄漏电流,极大地降低了电路功耗.与10T[7]和ST[8]的亚阈值SRAM存储单元相比,本设计的存储单元具备更好的工艺鲁棒性和更低的泄漏功耗.与常规六管存储单元相比,本设计的功耗仅为六管存储单元功耗的1.16%. 表2 本设计与常规存储单元及文献中存储单元的性能比较 ) [1]Lutkemeier S, Jungeblut T, Berge H K O, et al. A 65 nm 32 b subthreshold processor with 9T multi-Vt SRAM and adaptive supply voltage control [J].IEEEJournalofSolid-StateCircuits, 2013,48(1): 8-19. [2]Makosiej A, Thomas O, Vladimirescu A, et al. Stability and yield-oriented ultra-low-power embedded 6T SRAM cell design optimization [C]//Design,Automation&TestinEuropeConference&Exhibition. Dresden, Germany, 2012: 93-98. [3]Tu Ming-Hsien, Lin Jihi-Yu, Tsai Ming-Chien, et al. A single-ended disturb-free 9T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing [J].IEEEJournalofSolid-StateCircuits, 2012,47(6): 1469-1482. [4]Eid S T, Whately M, Krishnegowda S. A microcontroller-based PVT control system for a 65nm 72Mb synchronous SRAM [C]//2010IEEEInternationalSolid-StateCircuitsConferenceDigestofTechnicalPapers. San Jose, CA, USA, 2010: 184-185. [5]Chen Jinhui, Clark L T, Chen Tai-Hua. An ultra-low-power memory with a subthreshold power supply voltage [J].IEEEJournalofSolid-StateCircuits, 2006,41(10): 2344-2353. [6]Lakshminarayanan S, Joung J, Narasimhan G, et al. Standby power reduction and SRAM cell optimization for 65nm technology [C]//QualityofElectronicDesign. Kuala Lumpur, Malaysia, 2009: 471-475. [7]Chang I J, Kim J J, Park S P, et al. A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS [J].IEEEJournalofSolid-StateCircuits, 2009,44(2): 650-658. [8]Kulkarni J P, Kim K, Roy K. A 160 mV robust Schmitt trigger based subthreshold SRAM [J].IEEEJournalofSolid-StateCircuits, 2007,42(10): 2303-2313. [9]Kim Tae-Hyoung, Liu J, Kim C H. An 8T subthreshold SRAM cell utilizing reverse short channel effect for write margin and read performance improvement [C]//CustomIntegratedCircuitsConference. San Jose, CA, USA, 2007: 241-244. [10]Bo Z, Hanson S, Blaauw D, et al. A variation-tolerant sub-200 mV 6-T subthreshold SRAM [J].IEEEJournalofSolid-StateCircuits, 2008,43(10): 2338-2348. [11]Verma N, Chandrakasan A P. A 256 kb 65 nm 8T subthreshold SRAM employing sense-amplifier redundancy [J].IEEEJournalofSolid-StateCircuits, 2008,43(1): 141-149. [12]Kim Tae-Hyoung, Liu J, Keane J, et al. A 0.2 V, 480 kb subthreshold SRAM with 1k cells per bitline for ultra-low-voltage computing [J].IEEEJournalofSolid-StateCircuits, 2008,43(2): 518-529. [13]Kushida K, Suzuki A, Fukano G, et al. A 0.7V single-supply SRAM with 0.495 μm2cell in 65 nm technology utilizing self-write-back sense amplifier and cascaded bit line scheme [C]//SymposiumonVLSICircuits. Hawaii, USA, 2008: 46-47.

3 仿真验证

3.1 写操作

3.2 读操作

3.3 保持数据

3.4 存储单元静态泄漏电流和动态操作电流比较

4 版图设计和测试

5 结语