基于SoPC的数码电子音乐相册设计与实现*

权震华,罗 亮

(西南科技大学 信息工程学院,四川 绵阳621010)

数码电子音乐相册形式新颖、展示信息丰富,在商场、站台、家庭有着广泛的应用。本文提出了一种基于SoPC技术的数码电子音乐相册设计方案,在FPGA内部定制一个Nios II软核处理器,再以其为核心,配以一定的外围电路和驱动程序设计,通过软硬件协同设计实现了一个人机接口友好的音乐相册。

1 系统总体设计

1.1 系统硬件框图

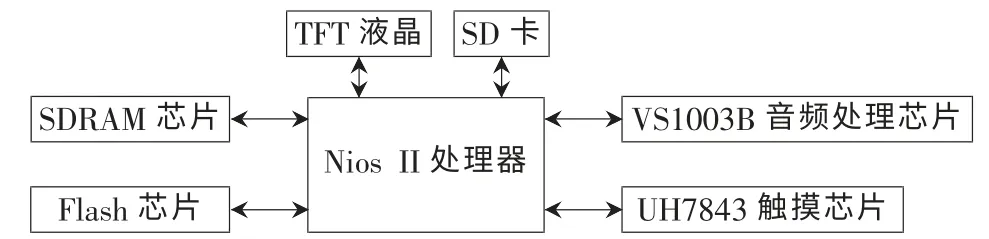

本系统以在Altera FPGA产品内定制的Nios II软核作为处理器,外围电路包括外围存储器驱动、MP3音频解码、TFT液晶屏控制、触摸屏驱动和SD卡驱动等电路。外围存储器和SD卡的驱动部分在FPGA内部实现,而MP3音频解码、TFT液晶屏控制、触摸屏驱动则分别选用了VS1003B、HX8347和UH78430芯片来实现。系统硬件框图如图1所示。

图1 系统硬件框图

1.2 SoPC系统设计

SoPC,即片上可编程系统,是Altera公司提出来的一种灵活高效的SoC解决方案,是指将处理器、存储器、定时器、总线控制器、通信接口、I/O端口等系统设计需要的功能模块集成到一个FPGA上,构建成一个可编程的片上系统。本设计基于Nios II处理器组建的SoPC系统框图如图2所示。

2 硬件设计

2.1 外部存储器

图2 SoPC系统框图

系统需在FPGA上添加Flash存储器和SDRAM存储器,分别用于存储应用程序代码和运行应用程序。Flash选中的应用程序代码在系统运行前将被拷贝到SDRAM中执行。本设计中的Flash存储器选用S29AL032D芯片,SDRAM存储器选用具有8 MB字节容量的A2V64S40CTP芯片。Flash存储器和SDRAM存储器都是使用Altera SoPC Builder工具中免费提供的Avalon总线IP挂接到片上Avalon总线上,以实现Nios II对它们的访问。

2.2 VS1003B芯片接口设计

VS1003B是芬兰VLSI公司出品的单芯片MP3/WMA/MIDI音频解码和ADPCM编码芯片,支持MP3、MP3+V、WMA、WAV、MIDI和SP-MIDI格式的音频解码播放,内部拥有高性能、低功耗DSP处理器核和缓存,且外围接口丰富。

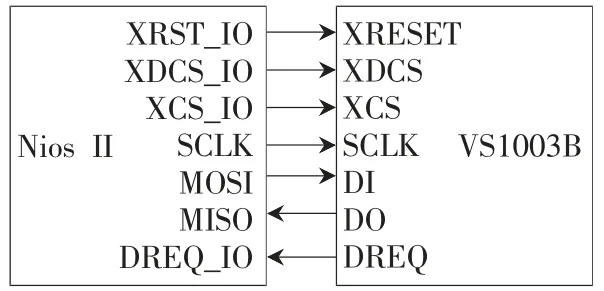

本设计使用7个IO口用于操作VS1003B,其端口连接图如图3所示。其中,各端口功能分别为:XRESET,复位;XDCS,数据片选;XCS,芯片片选;SCLK,SPI通信接口时钟输入;MOSI,SPI通信接口数据输出;MISO,SPI通信接口数据输入;DREQ,数据处理完中断输出。

图3 VS1003B硬件接口设计

VS1003B芯片内部共有16个16位控制寄存器,地址分别为0x0~0x0F,可通过SPI接口使用SCI通信协议来配置控制寄存器。需解码的数据也是通过SPI接口使用SDI通信协议传送到缓存,让芯片正确播放音频文件。

在使用VS1003B之前,需要对VS1003B的控制寄存器进行初始化配置;完成配置后,即可往VS1003B的缓存中写入解码数据,实现音频解码。

2.3 HX8347芯片接口设计

HX8347芯片是TFT液晶屏专用驱动芯片,最大支持320×240分辨率的TFT液晶屏。其内置173 KB的RAM,色彩模式支持最高26万色的显示。HX8347具有4种接口方式:8/9/16/18 bit系统总线方式、SPI总线方式、寄存器接口方式和RGB接口方式。

本设计采用16 bit系统总线方式,端口连接如图4所示。需使用21个IO口,各端口功能分别为:RST:复位;CS:片选;RS:指令/数据选择;WR:写使能;RD:读使能;DATA[15:0]:16 bit数据。

图4 HX8347硬件接口设计

HX8347内部共有132个寄存器,地址从0x00~0x93。在使用液晶屏前,需对其中大部分寄存器初始化。寄存器操作要使用CS、RS、RD、WR、DATA[7:0]端口。在正确配置寄存器后,就可进行显示数据的传送。数据传输与寄存器配置使用的端口是一样的,只是寄存器配置使用的是数据总线的低8 bit,而数据传送要使用全部16 bit数据总线。

对TFT液晶屏的操作,首先进行初始化操作,主要包括对液晶内部参考电压、开启晶振、显示缓冲区和RGB色彩等寄存器的设置。在完成初始化之后即可进行显示操作,先在液晶的RAM中开辟一个显示缓冲区,然后再向显示缓冲区填入显示数据即可实现TFT屏的显示与更新。

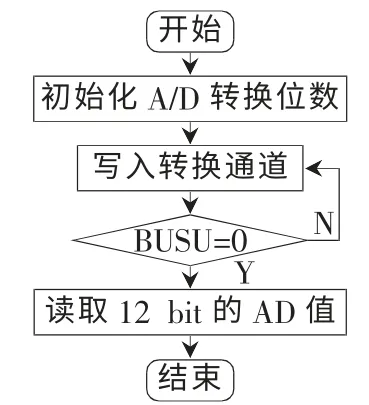

2.4 UH7843芯片接口设计

UH7843是TI公司生产的4线电阻触摸屏转换接口芯片,具有同步串行12位取样数模转换器,功耗低,转换速率高。

本设计使用了6个IO口来操作UH7843芯片,端口连接如图5所示。其中,各端口功能分别为:CS:芯片片选;SCLK:SPI通信接口时钟输入;DIN:SPI通信接口数据输入;DOUT:SPI通信接口数据输出;BUSY:芯片忙信号输出;IRQ:芯片中断信号输出。

图5 UH7843硬件接口设计

当触摸屏上有触摸动作时,触摸屏的X+、X-、Y+、Y-端会产生不同的模拟电压并送入UH7843。UH7843会对输入电压产生一个转换过程,转换完成后用中断通知处理器,处理器便会去读取此时的AD采样值,再调用程序计算实现触摸点的定位。

2.5 SD卡硬件接口设计

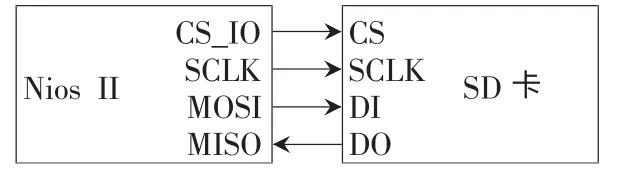

SD卡支持两种总线方式:SD方式与SPI方式。本设计采用IO口模拟SPI模式通信,使用4个IO口实现SD卡的控制。端口连接如图6所示。

图6 SD卡硬件接口设计

本设计采用CMD0、CMD1、CMD17和CMD24 4个命令组合操作SD卡。CMD0为SD卡复位指令,设置SD卡工作于SPI接口模式;CMD1初始化SD卡,激活SD处于工作状态;CMD17读SD卡扇区,读取一个扇区512 B数据,在读取时需要给出地址信息;CMD24写SD卡扇区,给出写入扇区地址以及数据后即可往SD卡指定扇区写入512 B数据。

通过复位SD卡、初始化SD卡、读取SD卡扇区数据3个步骤完成对SD卡的操作,实现从卡中读取数据的工作。

2.6 SoPC系统构建

在Altera Quartus II软件中建立工程,启动SoPC Builder工具定制Nios II处理器,进行SoPC系统的构建。本SoPC系统包括Nios II处理器模块、存储器接口模块、UART模块和PIO口总线模块等部分。

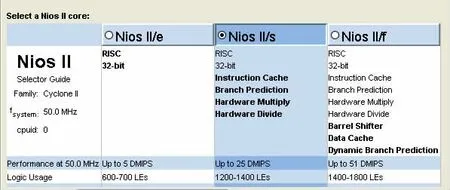

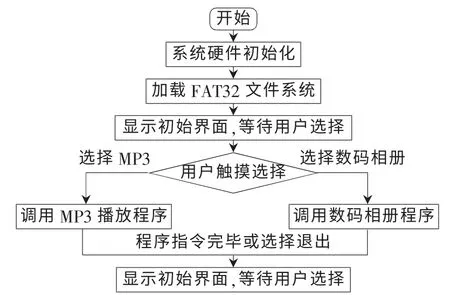

(1)Nios II/s CPU

结合本设计所需资源,选用标准型,如图7所示。

图7 SoPC构建

完成软核类型的选择之后,再进行JTAG Debug Module的设置,以便于调试。所得到的CPU配置如图8所示。

图8 CPU构建

(2)SDRAM、Flash等存储器接口模块

使用SRAM作为系统的通用数据存储器。SDRAM空间较大,可作为应用程序的运行空间;Flash作为程序存储器,用于存放应用程序代码。

(3)UART模块和PIO口总线模块

UART串口模块用于调试,系统也可以在此基础上扩展串口外设。将串口波特率设置为最大的115 200 bit/s。PIO口则用于控制SD卡、TFT液晶、触摸芯片以及音频模块这几个外部设备。

在添加完各个模块后,还需要为各个模块指定名称、类型、存储器地址映像和系统外设的中断设置,如图9所示。为了方便起见,通常将Flash的首地址设置为0,其他模块地址由系统自动分配。

3 软件设计

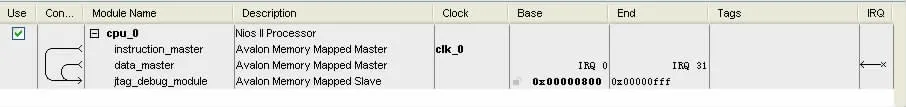

3.1 系统整体软件流程图

整个应用软件需要设计3大模块程序:MP3音乐播放程序、数码相册程序和触摸控制程序。整体软件流程图如图10所示。

图9 SoPC整体配置

图10 系统软件流程图

3.2 FAT32文件系统

为了方便对MP3文件和图像文件的访问,应用程序需要提供对文件系统的支持。本设计采用了znFAT32文件系统。

znFAT32是于振南为小型嵌入式设备完全独立编写且源代码开放的FAT32文件系统解决方案。znFAT32能够支持众多 的存储设备 (SD卡、CF卡、Flash、U盘等),支持多个存储器共同工作以及同时访问多个存储器对文件的操作;其对硬件资源要求低,代码完全由C语言编写,能够方便地移植到51单片机、AVR、ARM、Nios II等处理器上,占用资源极少,非常适合嵌入式开发中文件系统的嵌入。

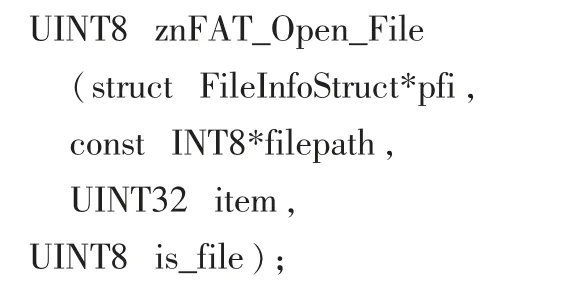

znFAT32其中的一个主要实现是文件打开函数,该函数原型如下:

其中,入口参数的意义分别为:pfi,文件信息结构体;filepath,文件名称;item,文件类型;is_file,确定是一个文件。

本设计首先使用文件打开函数打开文件,然后按需要对文件使用MP3处理函数和相册处理函数进行处理。

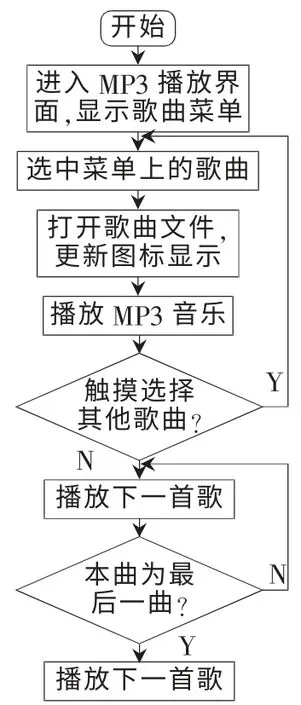

3.3 MP3播放音乐程序设计

MP3播放音乐程序流程如图11所示。

图11 MP3播放流程图

当进入MP3播放程序以后,首先读取出歌曲目录表,等待用户选择歌曲,超时等待后即刻进入目录表第一首歌曲播放。通过文件系统打开第一首歌曲,解析歌曲后,进入歌曲数据区按扇区读出数据进行解码播放。每个扇区读取完成后,查阅触摸缓冲区是否有需要处理的触摸信息,如果有换歌信息则换到相应歌曲播放,同时液晶显示界面切换;如果有退出播放信息,则执行退出播放状态切换到主界面;如果没有触摸信息,则继续播放,播放完一首歌后自动切换到下一首歌,直到所有音乐播放完成,最后返回主界面。在每个扇区读取完成后处理触摸信息,这样能实时响应触摸状态。

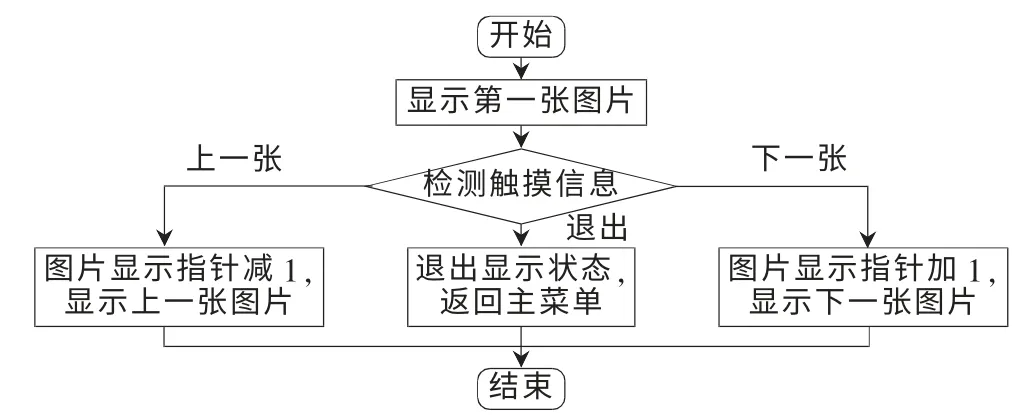

3.4 数码相册程序设计

数码相册是另一个主要功能。当系统进入到图片浏览功能后,会读取第一张图片显示,然后等待用户触摸选择显示图片或者退出。程序流程图如图12所示。

图12 图片显示主流程

在显示图片过程中,首先是通过文件系统读取图片数据区的第一个扇区,然后取出文件头、文件信息头、色彩表等信息,对图片的有效性进行检测,包括图片大小、图片格式、图片色彩模式以及图片的压缩类型。当检测到有效BMP图片时,即可进入图片显示,每显示一个扇区的数据,就检测触摸缓冲区是否有需要处理的数据,如果检测到选择下一张的触摸信息则跳入下一张图片显示,如果检测到上一张的触摸信息则退回上一张,如果是选择退出的触摸信息则返回主界面。

3.5 触摸控制程序设计

触摸控制程序流程图如图13所示。

图13 触摸控制程序流程图

4 系统调试

本设计在友晶科技的DE2开发板上进行调试验证。首先在DE2实验开发板上构建Nios II处理器;在测试构建的Nios处理器正确之后,再对各个外设的底层编写驱动,并一一进行测试;最后在底层驱动编写好的前提下,编写应用程序。

对SD卡读写模块、VS1003B音频模块、TFT显示模块、触摸芯片模块以及文件系统加载模块等外设底层驱动进行测试,可利用JTAG UART串口输出调试信息来进行正误验证。图14是当正确挂载FAT32文件系统,插上SD卡读取出SD卡的扇区信息后,在主机侧使用串口调试助手接收到的信息。

图14 FAT32文件系统加载测试图

本文给出了一种基于SoPC的数码电子音乐相册的设计方案。使用SoPC Builder开发工具在DE2开发板上构建Nios II处理器和SoPC系统,搭建了外围音频解码、TFT液晶驱动和触摸屏驱动等电路,编写了各外设的底层驱动以及应用程序,最终实现了数码电子音乐相册的设计。使用SoPC技术进行系统设计具有开发周期短、设计灵活、可将若干外部模块综合设计到一片高密度FPGA中等优点,同时设计更小巧,成本更低,更便于系统升级。目前SoPC技术的应用正在迅速扩大,具有广阔的应用空间和突出的市场竞争力。

[1]周立功.SoPC嵌入式开发系列教程[M].北京:北京航空航天大学出版社,2006.

[2]蔡伟刚.Nios II软件构架解析[M].西安:西安电子科技大学出版社,2007.

[3]武景涛,史大光,高龙,等.FPGA和Nios II软核的SD卡文件系统实现方法[J].单片机与嵌入式系统应用,2012(12):22-25.

[4]HAMBLEN J O,HALL T S,FURMAN M D.Rapid prototyping of digital systems:SoPC edition[M].Springer,2007.

[5]Gao Kun,Cai Junbo.A SoPC-based mini VGA video capture and storage system[C].2010 3rd International Conference on Biomedical Engineering and Informatics(BMEI 2010),2010.